福田昭のセミコン業界最前線

1mm角に10Gbitを詰め込む超高密度の3D NANDフラッシュ技術

2021年4月2日 06:55

超高層ビルディングと化した3D NANDフラッシュメモリ

3D NANDフラッシュメモリの高層化が止まらない。垂直に連なるセルトランジスタの積層数、あるいはワード線の積層数は最大で、176層に達した。一昨年(2019年)の春には最大で128層だったので、2年間で積層数は1.375倍に増加した。

3D NANDフラッシュメモリの高層化は、しばしば高層ビルディングにたとえられる。100階建てを超えたのが2019年のことだ。そして今年(2021年)には176階建てに高層化した。来年(2022年)あるいは再来年(2023年)には、200階を超える超高層ビルディングになることが確実視されている。

高層化よりもすさまじいのが記憶密度(記憶容量/シリコンダイ面積)の向上ペースだ。2021年春に記憶密度は4bit/セル(QLC)方式が13.8Gbit/平方mm、3bit/セル(TLC)方式が10.8Gbit/平方mmに達した。

過去の最高記録は、QLC方式が8.9Gbit/平方mm(2020年春)、TLC方式が7.8Gbit/平方mm(2019年春)である。それぞれ1.55倍、1.38倍に向上した。わずか1mm角のシリコンに、10Gbitを超えるデータを記憶できるようになった。

半導体回路技術の国際学会ISSCCで発表されたNANDフラッシュメモリの記憶密度は、2011年から2021年までの10年間で31.4倍に向上した。年率換算だと、1.41倍/年で増え続けたことになる。「2年で約2倍」、「4年で約4倍」という高い伸びを継続してきた。

3次元化(3D化)は記憶密度向上ペースの維持が目的

10年前、すなわち2011年の最先端NANDフラッシュメモリは3次元(3D)ではない。プレーナ(2D)技術によるもので、記憶密度は0.44Gbit/平方mmである。2年後の2013年にも2D技術によるチップが発表されており、記憶密度は0.87Gbit/平方mmと「2年で約2倍」を2D技術でも維持していることがわかる。

ちなみにISSCCの委員会が報道機関向けに配布しているプレスキットの2020年版によると、2006年以降、NANDフラッシュメモリの記憶密度は15年にわたってほぼ「2年に2倍」のペースで増え続けてきた。

NANDフラッシュメモリは一見すると3次元化(3D化)によって記憶密度の向上ペースが2D技術に比べて高まったかのような印象を受ける。しかし現実に起こったのは、2D NANDフラッシュメモリは「2年に2倍」の速度で記憶密度を高めており、その速度を維持するためにNANDフラッシュメモリは3D化したということだ。

言い換えると2D NAND技術では従来と同じペースの密度向上が不可能になってきたので、3D NAND技術に切り換えた。そして3次元技術の進化によって過去と同じペースの密度向上を現在まで維持してきた。

セルアレイの4分割、周辺回路とセルアレイの積層が性能と密度の両立を支援

ワード線の積層数が144層~176層の超高密度3D NANDフラッシュメモリ技術は、この2月(2021年)に開催された国際学会ISSCCで大手ベンダー各社が概要を公表した。

公表企業はIntel(講演番号30.2)、SK hynix(講演番号30.1)、キオクシア-Western Digital連合(以降は「キオクシア-WD連合」と表記)(講演番号30.4)、Samsung Electronics(以降は「Samsung」と表記)(講演番号30.3)である。

各社の発表から見えてくる共通技術は、メモリセルアレイの分割数を従来の2プレーン(2分割)から今回は4プレーン(4分割)に増やしたことによる高速化と、CMOS周辺回路とメモリセルアレイの積層構造(CUA(CMOS Under the Array)構造)を採用したことによるシリコン面積の削減と高速化である。

高層化と4プレーン化、CUA構造は、お互いに関連がある。高層化による製造の難しさを緩和するために、ワード線の配線膜と層間絶縁膜は薄くせざるを得ない。するとワード線の抵抗と容量が増加し、セルトランジスタの動作速度が低下する。これを防ぐために、メモリセルアレイの分割数を4つに増やしてワード線を短くし、ワード線抵抗の増加を防ぐとともにワード線容量を減らす。

4プレーン化の問題は、CMOS周辺回路のシリコン面積の増加である。2019年の国際学会ISSCCで128層の512Gbitチップを発表したキオクシア(当時は東芝メモリ)-WD連合は、メモリセルアレイのレイアウトを2プレーンから4プレーンに変更することで、シリコン面積が約15%増大すると述べていた(以下の関連記事参照)。ここでCUA技術を導入すると、シリコン面積の増加は1%以下に抑えられるという。

このほかの要素技術も見ていこう。多値記憶技術はTLC(3bit/セル)方式あるいはQLC(4bit/セル)方式で、これまでと変わらない。シリコンダイの記憶容量は1Tbitあるいは512Gbitである。大容量化は依然として進まない。シリコンダイ面積は1Tbit品が74~98平方mmと100平方mmを切っており、512Gbit品が47~60平方mmと約50平方mm(約7mm角)にまで小さくなった。

Intel : 144層とQLCで過去最高の記憶密度を達成

ここからは、NANDフラッシュ大手各社の最先端3D NANDフラッシュメモリ技術を概観していこう。

はじめはIntelの3D NANDフラッシュメモリ技術である。同社はプレーナNANDフラッシュの時代から、一貫してフローティングゲート技術を記憶原理に用いてきた。さらに時間を遡るとNORフラッシュメモリ、さらに戻ると紫外線消去型EPROM(UVEPROM)から、フローティングゲート技術の不揮発性メモリを開発してきた。Intelと不揮発性メモリ用フローティングゲート技術の付き合いは50年を超える。

Intelは、NORフラッシュメモリの開発と商業化では先行したものの、NANDフラッシュメモリの開発ではキオクシア(当時は東芝)およびSamsungに比べて出遅れた。そこで同じくNANDフラッシュ開発に出遅れたMicron Technologyと連合を組んで共同開発をはじめた。共同開発連合はプレーナNANDフラッシュではじまり、3D NANDフラッシュでも連合を継続した。

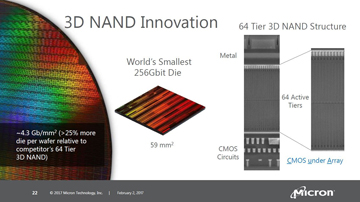

3D NANDフラッシュの技術世代だと、第1世代から第3世代まではIntelとMicronの共同開発である。ワード線の積層数で32層(第1世代)、64層(第2世代)、96層(第3世代)は共同開発の成果だ。

144層(第4世代)はIntelの独自開発による3D NANDフラッシュメモリである。この技術によって試作した1Tbitチップの概要をIntelは国際学会ISSCC2021で2021年2月に公表した(講演番号30.2)。第4世代の試作チップはQLC方式を採用したこともあり、13.8Gbit/平方mmと半導体メモリとしては過去最高の記憶密度を達成した。

IntelとMicronが共同開発した96層(第3世代)の1Tbitチップに比べ、ワード線の積層数は1.5倍と大幅に増えた。記憶密度は1.55倍とさらに増えている。シリコンダイ面積は65%に縮まった。

試作チップで注目すべきは、QLC(4bit/セル)方式の3D NANDフラッシュメモリでは過去最高の動作速度を達成していることだ。書き込み(プログラム)時間は1.63msと96層のQLC品に比べて2割ほど短い。プログラムのスループットは40.0MB/sと96層のQLC品に比べて3割ほど高い。最大読み出し時間は128μsと96層のQLC品に比べて2割ほど短い。

Intelの開発姿勢を継続して見ていくと、TLC方式よりもQLC方式の開発に熱心なように見える。QLC方式による開発成果の発表が目立つ。

SK hynix : TLC方式では過去最高の記憶密度を実現

次はSK hynix(同社は最近「SK Hynix」ではなく、「SK hynix」と表記するようになったので、本稿では表記を改めることにする)の最先端3D NANDフラッシュメモリ技術である。同社は3D NANDフラッシュメモリの開発では当初、競合する大手メーカーに比べると遅れているとみなされていた。しかしその後は急速にキャッチアップを進めており、ここ2年ほどは競合他社と遜色のない水準に達している。

SK hynixは3D NANDフラッシュメモリから、記憶技術をチャージトラップ方式に切り換えた。プレーナNANDフラッシュメモリではフローティングゲート方式を採用していた。この点はSamsungやキオクシア-WD連合などと同様であり、標準的な方向に見える。

特徴的なのは、CMOS周辺回路とメモリセルアレイを積層する技術「PUC(Periphery Under Cell array)」を、フローティングゲート方式では最初に製品に採用したことだ。

一方でQLC技術の製品化には、あまり積極的でないように見える。製品の主流はTLC技術のようだ。これは2019年までは、NANDフラッシュメモリの売り上げに占めるSSDの割合が30%以下と低く、モバイル向け(スマートフォン向け)が大半を占めていたためと見られる。

2020年にはNANDフラッシュの売り上げの半分をSSDが占めるようになっており、今後はQLC品の開発と生産にもリソースを割いていくと見られる。

国際学会ISSCC2021では、SK hynixとしては第7世代(4D V7)となる176層の3D NANDフラッシュメモリ技術の開発成果を報告した(講演番号30.1)。176層というワード線積層数はこれまで国際学会で発表された3D NANDフラッシュのなかではもっとも多い。多値記憶はTLC方式である。記憶密度は10.8Gbit/平方mmとTLC方式ではもっとも高い。試作したシリコンダイの記憶容量は512Gbitである。

ワード線積層数の増加に伴うワード線抵抗とワード線容量の増大を抑制するため、メモリセルアレイを4つのプレーンに分割するとともに、ワード線デコーダをプレーンの中央にレイアウトした。ワード線デコーダをプレーンの端部に配置する場合に比べ、ワード線の抵抗と容量を半分に減らした。

またワード線積層数の増加により、ワード線の抵抗値と容量値のばらつきが大きくなる。ばらつきを吸収するためにメモリセルの位置に応じてワード線を4つのグループに分け、各グループに対して遅延時間が最短になるようにワード線のオーバードライブ電圧を制御した。この工夫によって書き込み(プログラム)時間を5%短縮した。

キオクシア-WD連合 : TLC方式では過去最高に匹敵する記憶密度を達成

続いてキオクシア-WD連合の最先端3D NANDフラッシュメモリ技術の概要を説明しよう。キオクシア(前身は東芝および東芝メモリ)とWD(前身はSanDisk)の連合はプレーナ(2D)NANDフラッシュメモリの時代からはじまっており、その歴史は長い。

筆者の調べでは、1999年10月7日に東芝とSanDiskが、NANDフラッシュメモリの共同開発と製造合弁会社(折半出資)の設立で合意したと発表したのがはじまりだ。21年を超えるパートナーシップということになる。半導体業界では業務提携そのものはめずらしくないが、20年を超えて継続した事例はあまり聞かない。

キオクシア-WD連合が3D NANDフラッシュメモリの開発に取り組んだのは非常に早い時期だ。キオクシアの前身である東芝が2007年6月に、BiCS(Bit Cost Scalable)構造の3D NANDセルストリングを国際学会VLSI Technologyで発表した(講演番号2-2)。このときすでに、基本技術となるメモリスルーホール形成と埋め込みの技術、チャージトラップ方式のセルトランジスタ技術が登場している。

しかし3D NANDフラッシュメモリへの本格的な取り組みでは、Samsungに遅れをとった。Samsungが2013年8月に24層の3D NAND技術(第1世代)による128Gbit品の製品化を発表してプレーナNANDからの切り換えを積極的に進めたのに対し、東芝-SanDisk連合が3D NANDの製品化に本格的に取り組んだのは、第3世代(BiCS3)の64層品からだ。

2017年2月の国際学会ISSCCで発表したTLC方式の512Gbitチップにより、技術開発でトップグループに位置していることが明らかになった。

国際学会ISSCC2021では、キオクシア-WD連合としては第6世代(BiCS6)となる3D NANDフラッシュメモリ技術で試作した1Tbitチップの概要を発表した(講演番号30.4)。ワード線の積層数は170層を超える(講演および論文の表記は「170+」)。

なおキオクシアとWDが共同で2021年2月18日に公表したニュースリリースでは、ワード線の積層数は「162層」となっている。

多値記憶技術はTLC方式を採用した。記憶密度は10.4Gbit/平方mmとTLC方式ではトップのSK hynixが記録した10.8Gbit/平方mmとほぼ同じ水準であり、非常に高い。シリコンダイ面積は98平方mmで、TLC方式の1Tbitメモリとしては過去最小となった。

記憶密度を高めるためにCUA(Circuit Under Array)構造を採用し、アナログ回路とセンスアンプ回路をメモリセルアレイ直下のシリコンウェハ表面に作り込んだ。メモリセルアレイを4つのプレーンに分割して動作速度を向上させるとともに、電源線(および接地線)をプレーンごとに割り当てることでプレーン間の電源雑音干渉を防いでいる。

Samsung : 高速動作を重視した17x層の3D NAND技術を開発

ここからは、NANDフラッシュメモリの最大手ベンダーであるSamsungの最先端3D NANDフラッシュメモリを報告しよう。同社はNANDフラッシュメモリの大手メーカーのなかでは、3次元(3D)化にもっとも熱心だった企業として知られる。

Samsungは2013年8月に第1世代(V1)の3D NANDフラッシュメモリを製品化したと発表した。第1世代から量産に踏み切ったメーカーは、たぶん、Samsungだけだろう。2013年~2016年頃は、3D NANDフラッシュメモリの開発と量産ではSamsungの独走状態が続いた。技術世代では第1世代(V1)から第3世代(V3)、ワード線の積層数では24層~48層の3D NANDフラッシュである。

しかし第4世代(V4)の64層になると、競合他社が追いつきはじめる。キオクシア-WD連合は64層とTLC方式の組み合わせで512Gbitチップを開発、Intel-Micron連合は64層とQLC方式の組み合わせで1Tbitチップを開発し、技術と市場の双方でSamsungと競い合うようになった。これが2017年~2018年頃のことだ。残るSK hynixも2019年には技術開発でSamsungなどのトップグループと競える水準に達した。

競争優位が崩れるという危機感からか、2018年からSamsungはフラッシュメモリ業界への露出を控えるようになった。まず起こったのが、2018年8月のイベント「フラッシュメモリサミット(FMS : Flash Memory Summit)」に参加しなかったことだ。

FMSはフラッシュメモリに関する世界最大のイベント(講演会および展示会)であり、前年まではSamusngは基調講演と出展社の常連だった。2019年と2020年のFMSにもSamsungは基調講演および展示会に参加していない。

続いての異変が2019年2月の国際学会ISSCCである。Samsungは2014年から2018年のISSCCでは極めて力の入った技術講演を披露していた。それが2019年では最新世代(あるいは次世代)の技術情報を公開することに対してやや消極的な発表が見られた。

2020年のISSCCは92層の現行世代(第5世代)をQLC化したチップの発表だったので消極さは見られなかったものの、次世代(第7世代)の発表である2021年は再び、2019年と類似の消極さが感じられた。非常にナーバスになっているようにうかがえる。

国際学会ISSCC2021では、次世代技術である第7世代(V7)の3D NAND技術によって512Gbitのフラッシュメモリを試作した結果を報告した(講演番号30.3)。ワード線の積層数は170層を超える(発表論文の表記は「17x」)。多値記憶技術はTLC方式である。記憶密度は8.5Gbit/平方mmで、SK hynixおよびキオクシア-WD連合が試作したチップに比べると少し低い。

高速化のためにメモリセルアレイを4つのプレーンに分割するとともに、周辺回路とメモリセルアレイを積層するCOP(Cell Over Peri)技術を駆使した。メモリセルアレイと入出力パッドを除いた周辺回路のほとんどを、メモリセルアレイの直下にレイアウトした。読み出しのスループットは1.84GB/s、書き込み(プログラム)のスループットは184MB/sと高い。

Micron : 128層に続けて176層の3D NANDを単独で開発

残る大手メーカーはMicronである。Micronは第1世代(32層)~第3世代(96層)までをIntelと共同開発してきた。第4世代(128層)と第5世代(176層)はMicronの単独開発である。

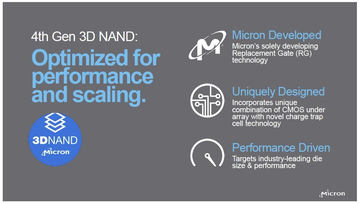

Micronは共同開発から単独開発に移行したときに、セルトランジスタ技術を切り換えた。第3世代まではフローティングゲート方式のセルトランジスタを採用していた。これを第4世代以降は、チャージトラップ方式のセルトランジスタに変更した。

チャージトラップ方式の3D NAND技術には大別すると、東芝が開発したBiCS技術とSamsungが開発したRG(リプレイスメントゲート)技術がある。Micronが採用したのはRG技術だ。RG技術とチャージトラップ方式の組み合わせは、Intelを除いたNANDフラッシュ大手が共通して採用している技術でもある。

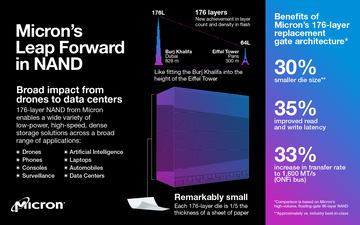

Micronは2020年11月9日に、3D NANDフラッシュメモリとしては過去最多のワード線積層数となる176層の3D NAND技術を開発し、同技術によるメモリチップの出荷を開始したと報道機関向けに発表した。

多値記憶はTLC方式である。メモリチップの記憶容量や記憶密度、シリコンダイ面積、動作性能などは明らかにしていない。この技術はIntelとの共同開発時代から数えると第5世代、単独開発だけで数えると第2世代に相当する。

Micronは2020年11月30日に開催した技術説明会「2020 Technology Briefing」で、3D NANDフラッシュメモリの技術開発に関する状況を公表した。176層の3D NANDフラッシュは、88層を1つのスタック(ティアーあるいはデッキ)とする2つのスタックで構成する。

フローティングゲートからリプレイスメントゲート(RG)の移行により、RGの第1世代である128層品の開発にはかなりの期間を要した。しかしRGの第2世代である176層品の開発は、かなり短い期間で完了したとする。

また第3世代までのフローティングゲート(FG)方式と第4世代以降のリプレイスメントゲート(RG)方式(チャージトラップ方式)を比較し、ワード線の積層数が100層未満ではFG方式が、100層以上ではRG方式が優位になると述べていた。FG方式は100層を超えるとスケーリングとコスト、消費電力、性能で問題が大きくなるとする。

3D NANDフラッシュの記憶密度向上はとどまるところを知らない。技術世代ごとにワード線の積層数は1.33~1.5倍に増加してきた。次世代あるいは次々世代は、176層の1.33倍だと234層、176層の1.5倍だと264層になり、144層の1.33倍だと192層、144層の1.5倍だと216層になる。

製造の難しさは当然ながら上昇する。決して低いハードルではないが、実現可能だというのが3D NANDフラッシュ開発コミュニティの共通認識だ。まだ限界は見えていない。

![[月間優良ショップ] ミニPC Windows11Pro デスクトップパソコン ミニパソコン mini pc office付き intel core i5/i7 8G+256GB 13世代CPU 【メモリ16GB DDR4 1TBSSD】M.2NVMe 4K出力 超軽量 静音 省スペースpc 小型 wifi5 BT5.2 初期設定済 持ち運び 製品画像:4位](https://thumbnail.image.rakuten.co.jp/@0_mall/japan-beauty/cabinet/12412735/12490269/imgrc0119629090.jpg?_ex=128x128)

![90日つけるだけ 健康ダイエットノート [ 福田千晶 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2906/9784522442906_1_5.jpg?_ex=128x128)

![2025-26年版 技術士第二次試験 建設部門 最新キーワード100 [ 西村 隆司 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7947/9784296207947_1_51.jpg?_ex=128x128)

![NI44DC 聖書 新共同訳 旧約聖書続編つき 小型(A6判) ビニールクロス装 [ 共同訳聖書実行委員会 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2058/9784820212058.jpg?_ex=128x128)

![乱雲 傀儡剣合わせ鏡 密命(十二)決定版 (文春文庫) [ 佐伯 泰英 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5130/9784167925130_1_7.jpg?_ex=128x128)

![イン・ザ・メガチャーチ [ 朝井リョウ ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1045/9784296121045_1_4.jpg?_ex=128x128)

![サイコ×パスト 猟奇殺人潜入捜査 13 【電子書籍】[ 本田真吾 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/6954/2000020406954.jpg?_ex=128x128)

![貴族転生 〜恵まれた生まれから最強の力を得る〜 11巻 【電子書籍】[ 三木なずな ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0537/2000020190537.jpg?_ex=128x128)

![情報リテラシー Windows 11 Office 2024/Microsoft 365対応 [ 富士通ラーニングメディア ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2159/9784867752159_1_4.jpg?_ex=128x128)

![2026-2027年版 図解わかる税金 [ 芥川靖彦 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4747/9784405104747_1_3.jpg?_ex=128x128)