福田昭のセミコン業界最前線

1mm角のシリコンに15Gbitを詰め込む超々高密度の3D NANDフラッシュ技術

2022年9月29日 08:48

高密度化は1年で1.4倍強のハイペースを2022年も維持

昨年(2021年)4月2日付けの本コラム「1mm角に10Gbitを詰め込む超高密度の3D NANDフラッシュ技術」では、同年2月の時点で3D NANDフラッシュメモリの記憶密度が1平方mm当たりで10Gbitを超えたこと、記憶密度は1年で1.41倍のペースで向上してきたことを述べた。

また本文の末尾では、3D NANDフラッシュの高密度化を支える「高層化」について「技術世代ごとにワード線の積層数は1.33倍~1.5倍に増加してきた。次世代あるいは次々世代は、176層の1.33倍だと234層、176層の1.5倍だと264層になり、144層の1.33倍だと192層、144層の1.5倍だと216層になる。製造の難しさは当然ながら、上昇する。決して低いハードルではないが、実現可能だというのが3D NANDフラッシュ開発コミュニティの共通認識だ」と指摘した。

それから1年半が経過した。2022年2月の時点で、試作チップの記憶密度は最高で15.0Gbit/平方mmに達した。2022年2月~8月までに何らかの形で発表された3D NANDフラッシュ技術はおおむね、14Gbit/平方mmを超える高い記憶密度を実現した。「1年で1.41倍のペース」は現在も維持されている。

高密度化の主力技術である「高層化」に関しては、1.33倍に積層数を増やした試作例が多い。176層の世代を2021年以前に発表した企業は2022年の次世代品では1.33倍の234層前後、具体的には232層と238層に積層数を増やした。144層の技術世代を2021年以前に発表した企業は、2022年の次世代品では1.33倍の192層に高層化した。

ワード線の積層数が1.33倍だと、高層化だけでは1.41倍に達しない。残りは横方向の縮小(メモリホールのピッチ縮小)や周辺回路積層(3Dメモリセルアレイ層の下部に周辺回路をレイアウトする構造)の改良などによって密度を稼いだことが伺える。

国際学会、プレス発表、講演会イベントで開発成果を公表

3D NANDフラッシュメモリの開発成果は、主に3つの機会で発表されてきた。1つは国際学会である。毎年2月に開催される半導体回路技術の国際学会「ISSCC」では、NANDフラッシュの大手メーカーがチップ全体の概要を含めて開発成果を公表することが多い。学会は基本的に技術情報を発表する場なので、有用な情報が少なくない。

もう1つは報道機関向けの成果発表(プレスリリースやプレス向け説明会など)である。発表企業は公表する情報を自由に選べるので、技術的な内容は貧弱なことが多い。

3つ目は展示会や講演会などのイベントである。毎年8月に開催されるフラッシュメモリ業界最大のイベント(講演会と展示会の両方を開催)「フラッシュメモリサミット(FMS.jpg

Flash Memory Summit)」では、大手メーカーがキーノート講演の中で最新の開発成果を「ほんの少しだけ」披露することが少なくない。技術的な内容には乏しいものの、技術の最新動向を把握するためには非常に重要なイベントだ。

170層前後の高層化と4bit/セルの多値記憶を組み合わせて15Gbit/平方mmを達成

今年(2022年)は2月の国際学会ISSCCで、複数の大手メーカーが開発成果を公表した。Western Digital(以降はWDと表記)とキオクシアの連合(以降はWD-キオクシア連合と表記)、Micron Technology(以降はMicronと表記)、SK hynix、Samsung Electronics(以降はSamsungと表記)がシリコンダイの試作品と回路技術を披露した。WD-キオクシア連合とMicron、SK hynixは170層前後の高層化技術とQLC(4bit/セル)方式の多値記憶技術を組み合わせ、14.7Gbit/平方mm~15.0Gbit/平方mmと高い記憶密度を達成した。

234層前後の超高層3D NANDフラッシュ技術がFMSに続出

次に3年ぶり、2019年以来のリアル開催となった2022年8月のフラッシュメモリサミット(FMS)ではSK hynixと子会社のSolidigm(ソリダイム)、YMTCが大容量3D NANDフラッシュメモリの開発成果を一部、キーノート講演で明らかにした。なおSolidigmは、SK hynixがIntelのNANDフラッシュメモリおよび応用品の事業を買収して2021年12月に設立した企業である。

報道機関向け発表では、FMSの直前となる7月26日にMicronが232層の超高層3D NANDフラッシュメモリ技術を開発したとアナウンスした。なおMicronは、FMSのキーノート講演および展示会には加わっていない。またFMSのキーノート講演と展示会に参加したSK hynixは、FMS閉幕直後の8月5日に、キーノート講演で披露した238層の超高層3D NANDフラッシュメモリ技術の概要を報道機関向けに発表した。

FMSとその前後に発表された開発成果の特徴は、ワード線の積層数を232層~238層に高層化したことにある。既存の世代では176層前後であり、その1.33倍である234層前後にワード線の積層数を増やした。この結果、多値記憶では3bit/セル(TLC)の標準的な方式を採用しているにも関わらず、176層前後で4bit/セル(QLC)方式を採用した3D NANDフラッシュメモリに匹敵する高い記憶密度を実現した。

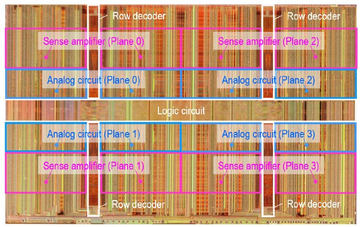

192層とPLC方式でSolidigmが過去最大となる1.67Tbitのダイを試作

またFMSのキーノート講演で見逃せないのが、SK hynixが子会社Solidigmの開発成果にふれたことだ。Intelで開発した最後の世代である144層のQLC方式から、ワード線の積層数を1.33倍に増やした192層の3D NANDフラッシュメモリ技術を紹介した。試作したシリコンダイは2種類。1つはQLC方式、もう1つはPLC(5bit/セル)方式である。QLC方式では1.33Tbit、PLC方式では1.67Tbitと大きな記憶容量を達成した。QLC方式ではシリコンダイ写真も披露した。PLC方式のシリコンダイ写真は見せていない。

PLC方式で大容量フラッシュメモリを試作した事例はたぶん、これが初めてだろう。しかも1.67Tbitという過去最大の記憶容量を備えた。キーノート講演では、31通りのしきい電圧を書き込んだ後の分布状況と、1,000回の書き換えサイクルを経てもしきい電圧の分布がほぼ変わらないとのテスト結果を示していた。

1年半前と比較すると、3D NANDフラッシュメモリの要素技術にはかなりの変化がみられる。ワード線の積層数は1.33倍に増加し、多値記憶では5bit/セル(PLC)技術の試作チップが登場した。単純計算では、PLC方式はQLC方式と比べて1.25倍の記憶密度を得られる。高層化と組みわせると、理論的には記憶密度は1.66倍になる。

また同じ記憶容量でのシリコンダイ面積は、TLC方式では約70%に縮小した。一方でQLC方式は高層化が古い世代のままであるため、シリコンダイ面積がそれほど小さくなっていない。2022年後半から2023年前半には、234層前後の高層化とQLC方式を組み合わせたさらに高い記憶密度の達成が期待できそうだ。

![逃げ上手の若君 25 【電子書籍】[ 松井優征 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2520/2000020202520.jpg?_ex=128x128)

![住みにごり(10) 【電子書籍】[ たかたけし ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9499/2000020239499.jpg?_ex=128x128)

![呪術廻戦≡ 3 (ジャンプコミックス) [ 岩崎 優次 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0429/9784088850429_1_10.jpg?_ex=128x128)

![百姓貴族(9) 【電子書籍】[ 荒川弘 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/3568/2000020383568.jpg?_ex=128x128)

![雑用付与術師が自分の最強に気付くまで(コミック) : 11 【電子書籍】[ アラカワシン ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/3698/2000020463698.jpg?_ex=128x128)

![[注文後キャンセル不可/代引き不可/発売後に発送] ワンピースマガジン ONE PIECE magazine[本/雑誌] Vol.21 【特集】 ヒロインズ 【カード付き同梱版】 (集英社ムック) (単行本・ムック) / 尾田栄一郎 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/neowing-r/cabinet/item_img_2196/neobk-3205619.jpg?_ex=128x128)