福田昭のセミコン業界最前線

Intel 18AやSamsungの第9世代NANDがVLSIシンポジウムで披露

2025年6月11日 09:40

半導体のデバイス・プロセス技術と集積回路技術に関する最先端の研究開発成果を披露する国際学会「VLSIシンポジウム(2025 IEEE Symposium on VLSI Technology and Circuits:VLSI 2025)」が8日に始まった。開催地は京都府京都市、会場は「リーガロイヤルホテル京都」である。京都開催ではこのホテルがコロナ禍前から会場として使われており、常連の参加者にとっては馴染み深い。

プレイベントである8日のワークショップ、9日のショートコースを経て、10日にはメインイベントの技術講演会(テクニカルカンファレンス)がスタートする。VLSIシンポジウムの全体像はすでに本コラムでレポートした。今回は、メインイベントで発表される数多くの研究成果の中から、実行委員会が選出した注目講演をご紹介する。具体的には、シンポジウムを構成する2つの分野、「デバイス・プロセス技術分野」(「テクノロジー」分野あるいは「技術」分野と呼ぶことが多い)と、「回路技術分野」(「サーキット」分野あるいは「回路」分野と呼ぶことが多い)に分けて説明する。

今回はデバイス・プロセス技術分野の論文投稿・採択状況と、ハイライト講演をお届けする。回路技術分野については機会を改めるので、ご了承されたい。

投稿件数は346件で最高水準を維持、採択率は30%とまだ低い

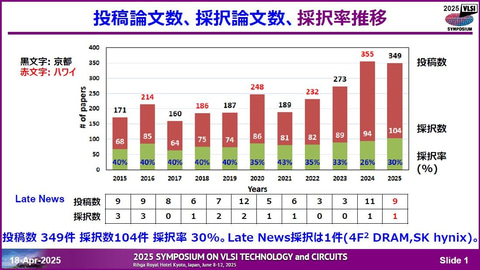

始めは「テクノロジー」分野の投稿論文数と採択論文数、採択率の状況である。投稿件数は349件で前年(2024年のハワイ開催)の355件とほぼ変わらない。京都開催の前回は273件だったので大幅に増えている。

採択件数は104件で前年から10件ほど増えた。採択率は30%である。前年は26%だったので4ポイント向上した。それでも2015年から2022年の35%~43%に比べると、まだ厳しい状況が続く。

国/地域別の投稿件数では中国、採択件数では韓国がトップを占める

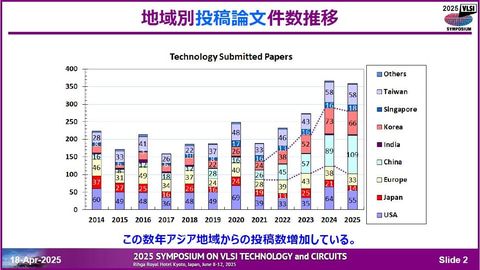

投稿論文数を国/地域別にみると、ここ数年は日本を除くアジア諸国の台頭が著しい。2010年代は米国(北米)が強かったが、2020年代は中国と韓国の投稿件数が急速に増えている。

2025年のトップは中国でダントツの109件に達する。次が韓国の66件、その次が台湾の58件、それから米国が55件と続く。なお日本は14件である。

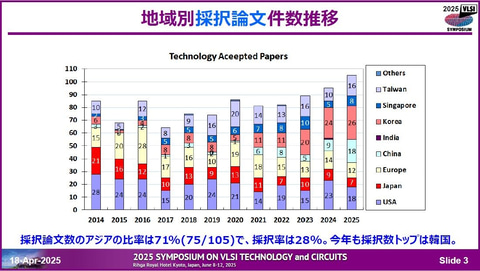

採択論文数を国/地域別にみると、韓国が26件(レイトニュースを含む)で最も多い。次が米国と中国で、いずれも18件である。その次が台湾の16件、さらに欧州が12件と続く。なお日本は7件である。

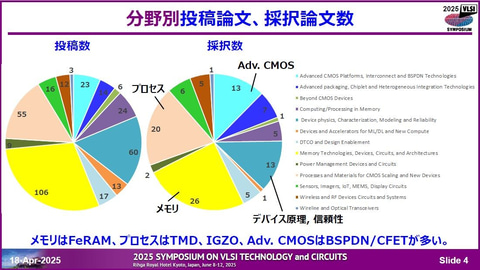

技術分野別の投稿件数ではメモリ、採択件数でもメモリが最大勢力に

技術分野別の投稿件数と採択件数ではいずれも、メモリが最多となった。「メモリ技術」分野の投稿件数は106件でダントツである。投稿件数で2番目に多いのは「デバイス物理と信頼性技術」分野で60件を数える。それから「CMOSプロセスと材料」分野が55件と続く。

メモリ技術採択件数は26件である。2番目に多いのは「CMOSプロセスと材料」分野で、20件が採択された。それから「デバイス物理と信頼性技術」分野と「先端CMOSプラットフォーム」分野がともに13件で続く。

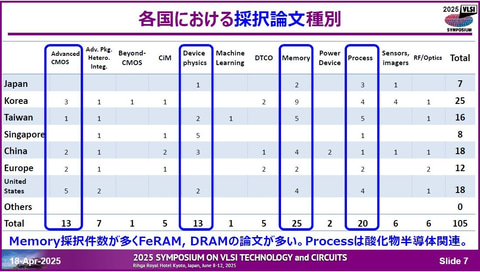

国/地域で採択論文の技術分野に差がある

主要な国/地域の採択論文件数を技術分野で分類すると、地域による差があることが分かる。先端CMOSプラットフォーム分野の13件では、米国が5件と最も多い。同じ13件のデバイス物理と信頼性技術分野だと、シンガポールが5件と多くなる。

メモリ技術分野は韓国が圧倒的に多い。25件中、9件を韓国が占める。CMOSプロセスと材料分野では突出した国/地域が見当たらない。採択数20件の中で多いのは、台湾が5件、韓国が4件、米国が4件となっている。

6年ぶりに大学の採択件数が産業の採択件数を上回る

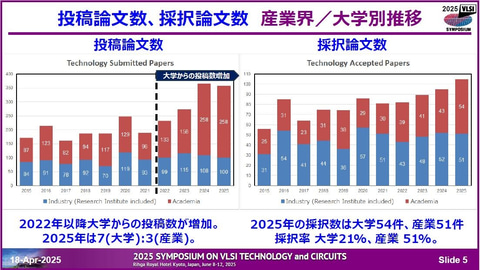

大学界(大学、大学院、大学付属機関)と産業界(企業と研究機関)の投稿件数と採択件数では、2022年以降、大学界からの投稿が急激に増えた。特に2024年における増加が著しく、投稿数の7割を占めるようになった。2025年もアカデミアからの投稿件数は前年と変わらない。件数は両年とも258件である。一方で産業界からの投稿件数はあまり変わらない。2022年~2025年の投稿数は99件~115件の範囲にとどまっている。

大学界と産業界の採択件数は基本的に大学が少なく、産業が多い。2025年は大学が54件、産業が51件と、大学の採択件数が産業を上回った。これは2019年以来のことだ。採択率は大学が21%、産業が51%で産業が高い。

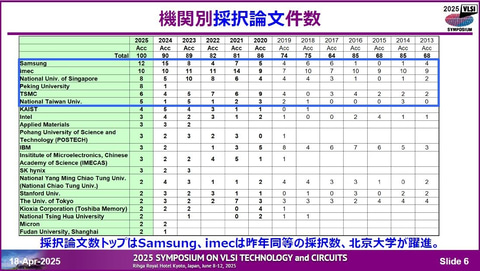

発表機関別採択件数のトップはSamsung、僅差でimecが続く

発表機関別の採択件数では、Samsung Electronicsが12件でトップを占める。僅差で10件のimecが2位につける。3位はNational Univ. of SingaporeとPeking Univ.でいずれも8件。4位のTSMCが6件、5位のNational Taiwan Univ.が5件と続く。上位6機関中、3機関を大学が占める。

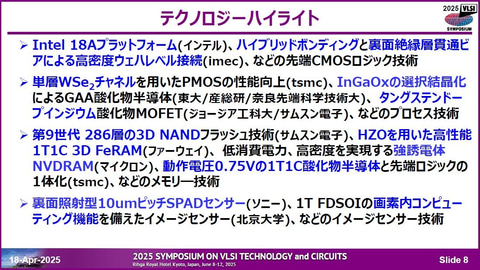

Intelの18A(2nm) CMOSプラットフォーム技術とimecのウェハレベル高密度接続技術

ここからはVLSIシンポジウムのコミッティ(委員会)が選んだ注目論文をご紹介しよう。先端CMOSプラットフォーム分野(2件)、プロセス技術分野(4件)、メモリ技術分野(4件)、イメージセンサー分野(2件)から合計で12件の論文を選んでいる。

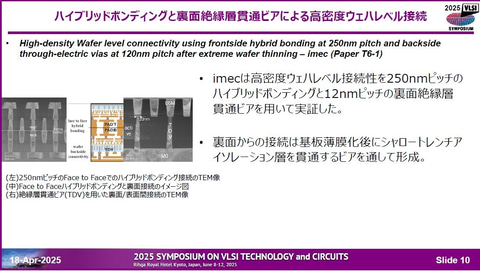

先端CMOSプラットフォーム分野では、Intelの18A(2nm相当)ノードCMOSプラットフォーム、imecの裏面絶縁層貫通ビアを備えた高密度ウェハレベル接合(ハイブリッド接合)をハイライトに選んだ。

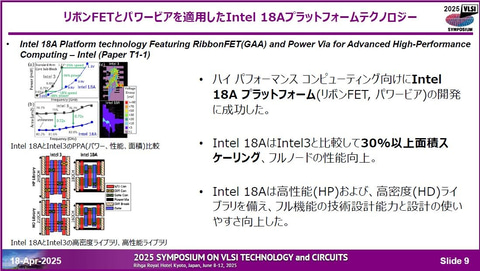

Intelが開発した18Aプラットフォーム「Intel 18A」は、3nm世代のプラットフォーム「Intel 3」の次世代に相当し、高性能コンピューティング向けである。同社が「リボンFET」と呼ぶナノシートFET技術と、パワービア技術(裏面電源供給技術)を採用した。

Intel 3に比べると、電源電圧が1.1Vのときに同じ消費電力で動作周波数が25%向上し、同じ動作周波数であれば消費電力が36%低下する。また電源電圧を0.75Vと低めに設定した時には、同じ消費電力で動作周波数が18%向上し、同じ動作周波数であれば消費電力が38%低下する。同一の動作周波数におけるロジック回路のシリコン面積は、72%に縮まるとする。

imecが開発した高密度ウェハレベル接合技術は、250nmピッチのハイブリッドボンディングによって実現した(論文番号T6-1)。ハイブリッドボンディングはフェースツーフェースであり、接合形成後にウェハを裏面から研削して薄型化する。裏面の絶縁層を貫通するビア(TDV)を12nmピッチで孔開けし、配線接続を形成する。

酸化物半導体FETの性能が継続して向上

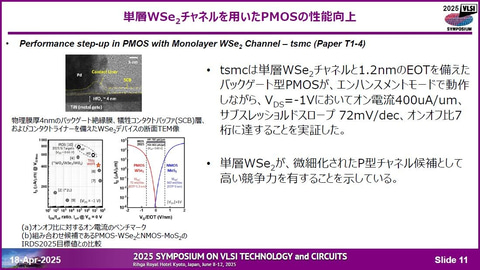

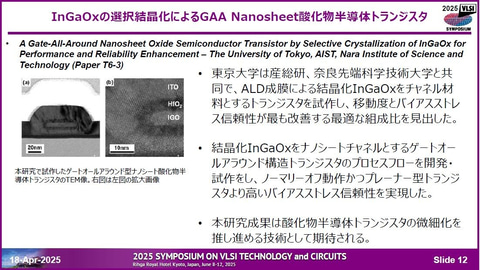

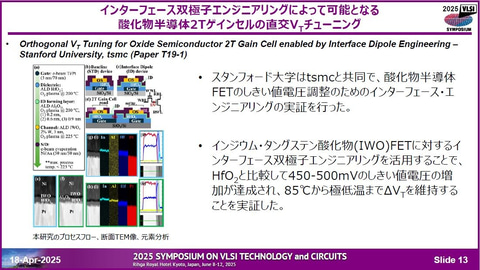

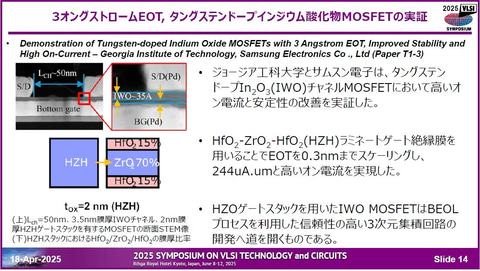

プロセス技術では、TSMCによる2次元電子材料をチャンネルに用いたpチャンネルMOS FETの高性能化(論文番号T1-4)、東京大学と産業技術総合研究所(産総研)、奈良先端科学技術大学の共同研究グループによる酸化物半導体ナノシートチャンネルの高性能・高信頼トランジスタ(同T6-3)、Stanford UniversityとTSMCの共同チームによる酸化物半導体FETの2トランジスタゲインセルでしきい電圧を調整する技術(同T19-1)、Georgia Institute of TechnologyとSamsung Electronicsに共同研究グループによるWドープのインジウム酸化物MOS FETでオン電流の増強と安定性の改善を実現した研究成果(同T1-3)を選んだ。

第9世代のNANDフラッシュと強誘電体不揮発性DRAM技術

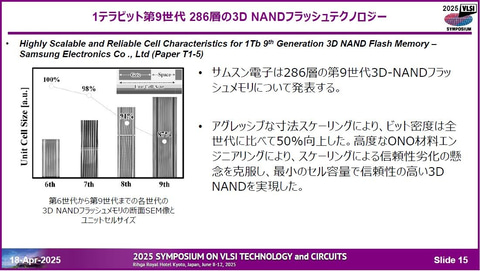

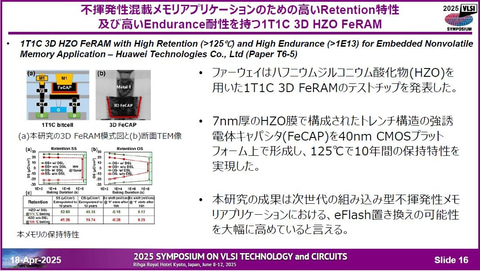

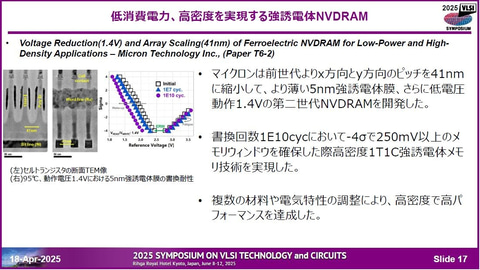

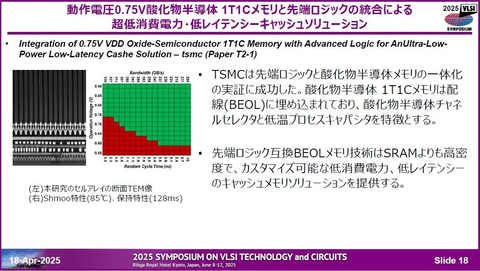

メモリ技術では、Samsungが開発した第9世代の3D NANDフラッシュメモリ技術(論文番号T1-5)、Huawei Technologiesが試作した32Mbitのハフニウム酸化物系強誘電体メモリ(FeRAM)(同T6-5)、Micron Technologyが開発した強誘電体不揮発性DRAM技術(同T6-2)、TSMCのオンチップキャッシュ用酸化物半導体メモリ(同T2-1)をハイライト論文に選んだ。

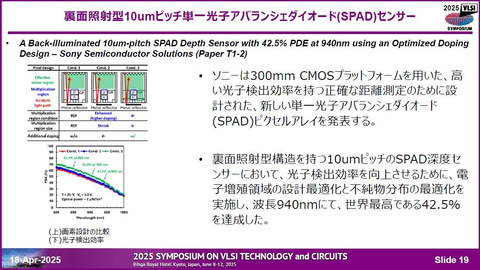

940nm波長の光子検出効率が高いSPADをソニーが開発

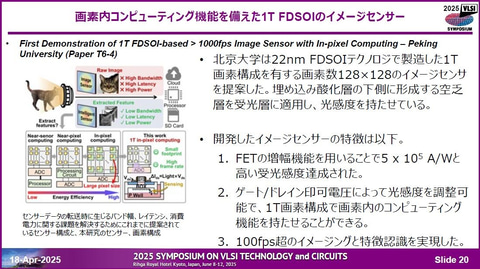

イメージセンサー技術では、ソニーセミコンダクタソリューションズが開発した光子検出効率(PDE)が42.5%と高い、距離測定用裏面照射型SPAD(単一光子アバランシェフォトダイオード)アレイ(論文番号T1-2)と、Peking Universityが試作した、22nm FD SOI構造のnチャンネルMOS FETを画素内に配置した128×128画素のイメージセンサー(同6-4)をハイライト論文に選んだ。

このほかにも興味深い研究開発成果が少なくない。機会があれば今後のレポートでご報告するので期待されたい。

![[台数限定価格★] ノートパソコン 店長おまかせ 最新 Windows11 Core-i5 等 八世代までCPU選択可 Core-i7 Core-i3 15.6型 SSD128GB メモリ8GB 無線LAN USB3.0 DVDドライブ 15.6インチ ノートPC パソコン 中古ノートパソコン 中古PC ノート Win11 Office付 中古パソコン 中古 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-shinjyo/cabinet/pc-note/omakase-vol_r5b.jpg?_ex=128x128)

![シャングリラ・フロンティア(26) 〜クソゲーハンター、神ゲーに挑まんとす〜【電子書籍】[ 硬梨菜 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/8753/2000020198753.jpg?_ex=128x128)

![最短で最大の成果を上げる AIアウトプットの全技法 [ 上岡正明 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4588/9784776214588_1_4.jpg?_ex=128x128)

![mojojojoぬいぐるみチャームBOOK [ mojojojo ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6411/9784847076411_1_4.jpg?_ex=128x128)

![学研の学習 はにわの大国宝展 世界とつながるほんもの体験キット [ 東京国立博物館 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9822/9784057509822_1_4.jpg?_ex=128x128)

![【令和8年度】 いちばんやさしい ITパスポート 絶対合格の教科書+出る順問題集 [ 高橋 京介 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8207/9784815638207_1_2.jpg?_ex=128x128)

![こころを浄化することば [ 神人 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9998/9784198659998_1_2.jpg?_ex=128x128)

![良寛遺墨集 全三巻 その人と書 [ 泉田玉堂 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1753/9784473041753.jpg?_ex=128x128)