ニュース

次世代スマートフォンの音声コマンド入力やHi-Fiオーディオなどを実現する回路技術がVLSIシンポジウムに登場

2024年6月20日 06:22

半導体デバイス・プロセス技術と半導体回路技術に関する最先端の研究開発成果を披露する国際学会「VLSIシンポジウム(2024 IEEE Symposium on VLSI Technology and Circuits)」が、2024年6月16日(現地時間)に始まった。開催地は米国ハワイ州ホノルル、会場はリゾートホテル「Hilton Hawaiian Village」である。17日には技術講座の「ショートコース」が実施された。18日には、メインイベントである技術講演会が始まった。

VLSIシンポジウムの全体像はすでに本誌でレポートした。本レポートでは、メインイベントで発表される数多くの研究成果の中から、実行委員会が選出した注目講演(ハイライト講演)をご紹介する。具体的には、シンポジウムを構成する2つの分野、「デバイス・プロセス技術分野」(「テクノロジー」あるいは「技術」分野と呼ぶことが多い)と、「回路技術分野」(「サーキット」あるいは「回路」分野と呼ぶことが多い)に分けて説明する。

VLSIシンポジウム(VLSI Symposium)は最近まで、「技術シンポジウム(Symposium on VLSI Technology)」と「回路シンポジウム(Symposium on VLSI Circuits)」の2つのシンポジウムで構成されていた。現在でも旧シンポジウムの実行委員会が分担して作業を承継している。このため、注目論文も2つの分野から選出されている。

ここでは先ほどの順番とは逆になるが、「回路技術分野」のハイライトを本レポートではご紹介する。なお、2024年4月19日(日本時間)に日本の報道機関・記者向けの説明会が事前に開催されており、このときに配布されたスライドと公式Webサイトに掲載されたプログラムなどの情報を参考にした。あらかじめご了承されたい。

432コアを搭載するRISC-V浮動小数点演算アクセラレータ

回路技術分野は、11件の発表がハイライトとして紹介された。プロセッサやメモリなどのテーマ別に注目論文を選んでいる。始めのテーマは「プロセッサとシステム・オン・チップ」、「機械学習のためのデバイスとアクセラレータ」、「メモリ技術」、「ディジタル回路・ハードウェアセキュリティ・シグナルインテグリティ・IO」である。

「プロセッサ……」では、チューリッヒ工科大学とスタンフォード大学、ボローニャ大学がRISC-Vアーキテクチャの浮動小数点演算アクセラレータを共同開発した(番号C7-4)。432個と多くのコアをデュアルチップレットで構成し、記憶容量16GBのHBM2Eモジュールを2つ、同じ基板に載せた。ステンシル演算およびスパース線形代数演算に向ける。消費電力当たりの浮動小数点演算性能は28.1GFLOPS/Wと高い。

「機械学習……」では、KAISTとサムスン電子が1T1CセルのDRAMを内蔵するインメモリコンピューティングアクセラレータを共同開発した(番号C20-1)。ResNetやBERT、GPT-2などの機械学習モデルに対応する。消費電力当たりの演算性能は28.1TOPS/Wと高い。SQNR(信号対量子化雑音比)の向上と電力効率の向上を両立させたとする。製造技術は28nm。27MbitのDRAMを内蔵した。

「メモリ技術」では、動作周波数が7GHzと高い1次データキャッシュ向けSRAMマクロをArmが開発した(番号16-3)。SRAMセルは8トランジスタによる1R1RW方式。製造プロセスは3nm、記憶密度は11.2Mbit/平方mmである。

「ディジタル回路……」では、ソウル大学とコロンビア大学が共同で、低消費電力かつ高精度のEnd-to-End方式10キーワード音声認識システムを開発した(番号C25-1)。モバイル機器を音声コマンドで起動/制御する用途に向けた。消費電力は5.6μWと低い。認識精度は92.7%である。

教師なし学習機能を備えたてんかん発作予測SoC

次のテーマは「医用生体デバイス・回路・システム」、「センサ・イメージャ・IoT・MEMS・ディスプレイ回路」、「データコンバータ」である。

「医用生体……」ではカリフォルニア大学バークレー校が、てんかん発作の予測分類用SoCの開発成果を報告する(番号C23-1)。予測には教師なし逐次型学習による分類器を実装することで、シリコンダイ面積を従来の5分の1に削減するとともに消費電力を134分の1に減らした。

「センサ・イメージャ……」では、キヤノンが50kルクスと高い照度下でも距離測定(測距)が可能な100万画素のSPAD(Single-Photon Avalanche Diode)イメージセンサーを開発した(番号C6-1)。周囲隣接画素からの発火情報を送受信するネットワークを構成することで、高照度環境での測距を可能にした。

「データコンバータ」では、16Gサンプル/sと高速で、分解能が10bitと高い時間領域アナログディジタル変換(ADC)回路を共同開発した南カリフォルニア大学とメディアテックの研究成果(番号C24-2)がハイライト論文に選ばれた。遅延ばらつきの補正機能と遅延オフセットのバックグラウンド補正機能を備えたパイプライン逐次比較型時間-ディジタル変換(TDC)回路を搭載した。製造技術は4nmのCMOSプロセスである。

6G移動体通信端末向けの110~170GHz帯CMOS無線送受信回路

最後のテーマは「アナログ&ミクストシグナル回路」、「有線および光トランシーバ・光インターコネクション」、「ワイヤレス&RFデバイス・回路・システム」である。

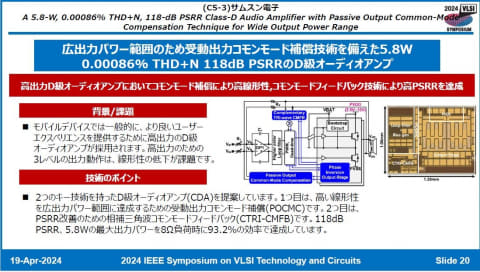

「アナログ……」では、サムスン電子がモバイル機器向けにTHD+N(全高調波歪プラス雑音)が0.00086%と低く、PSRR(電源電圧変動除去比)が118dBと高いD級オーディオアンプを開発した(番号C5-3)。最大出力は5.8W、最大効率は93.2%(負荷は8Ω)。

「有線および……」では、TSMCが3次元積層シリコンダイ間の超高速通信リンクを開発した(番号C14-1)。5nmのFinFET技術によるコンピュートダイと6nm技術によるSRAMダイを積層し、PAM-4方式によるレーン当たり16Gbit/sの通信リンクを9μmピッチで形成した。送信リンク数と受信リンク数はともに80レーン。単位面積(1平方mm)当たりの通信速度は17.9Tbit/sに達する。

「有線および……」では、インテルの研究成果であるチャンネル当たり50Gbit/s(NRZ信号)の4チャンネル光受信回路も注目論文に選ばれた(番号C14-4)。光ファイバを脱着可能なコネクタとフォトダイオード、トランスインピーダンスアンプ(TIA)IC、受信データパスICを同じパッケージに収容した。

「ワイヤレス……」では、東京工業大学が次世代(6G)移動体通信端末向けのDバンド(110GHz~170GHz帯)CMOS無線送受信回路を開発した(番号C9-2)。1チャンネル当たり200Gbit/sの送受信回路によって4チャンネル✕4アンテナのMIMO(Multi-Input Multi-Output)通信を構成し、全体では640Gbit/sの通信速度を達成した。

このほかにも興味深い研究開発成果が少なくない。機会があれば現地レポートでご報告するので期待されたい。

![【中古】LG Electronics Japan◆液晶モニタ・液晶ディスプレイ 22MP48HQ-P [21.5インチ]【パソコン】 製品画像:18位](https://thumbnail.image.rakuten.co.jp/@0_mall/jumblestore/cabinet/31999/2319405731999-01.jpg?_ex=128x128)

![新装版ブラック・ジャック 全17巻セット(化粧箱入り) [ 手塚治虫 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5142/9784253935142.jpg?_ex=128x128)

![もっと!となりの小さいおじさん 大切なことのほぼ9割は手のひらサイズに教わった 2 [ 瀬知 洋司 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2341/9784910512341_1_2.jpg?_ex=128x128)

![怠惰な悪辱貴族に転生した俺、シナリオをぶっ壊したら規格外の魔力で最凶になった Vol.3 【電子書籍】[ 菊池 快晴 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9037/2000020419037.jpg?_ex=128x128)

![悪役令嬢転生おじさん(10) 【電子書籍】[ 上山道郎 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0539/2000020190539.jpg?_ex=128x128)

![[新品]◆特典あり◆例国十二版・例漢コナンバッグ付セット[特製名探偵コナン付箋辞書引きふせん付] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0054/j0590418591_01.jpg?_ex=128x128)

![[新品]ゴールデンカムイ (1-31巻 全巻) 全巻セット 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0021/m9880472800_01.jpg?_ex=128x128)

![[新品]世界一初恋 ~小野寺律の場合~ (1-21巻 最新刊) 全巻セット 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0015/rkdk0584_01.jpg?_ex=128x128)

![AIを使って考えるための全技術 「最高の発想」を一瞬で生み出す56の技法 [ 石井 力重 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9488/9784478119488_1_2.jpg?_ex=128x128)