ニュース

性能が18%も向上した「Intel 3」プロセスの仕組み

2024年6月20日 11:42

Intelは18日(現地時間)、現在開催中のVLSIシンポジウムにおいて最新の「Intel 3」プロセスノードの詳細を発表した。量産は2023年第4四半期より既に開始しており、発表済みの「Xeon 6」に採用されている。

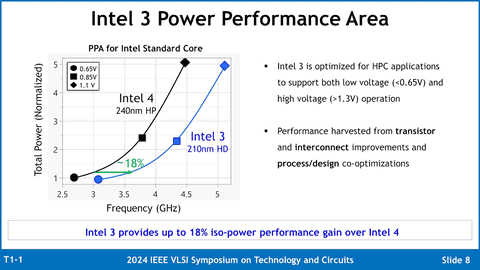

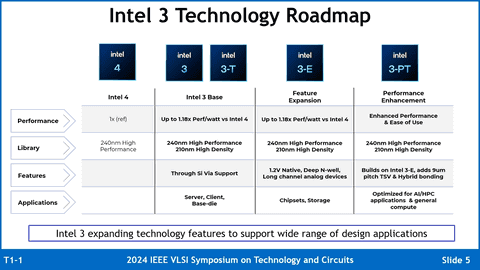

Intel 3は、個人向けのCore Ultraで既に採用され量産出荷中の「Intel 4」をベースに開発されたもの。従来のIntel 4と比較して、同じ電力下においてプロセッサコアの性能を最大18%、密度を最大10%向上させられる。この性能向上は1世代分の進化に相当する。

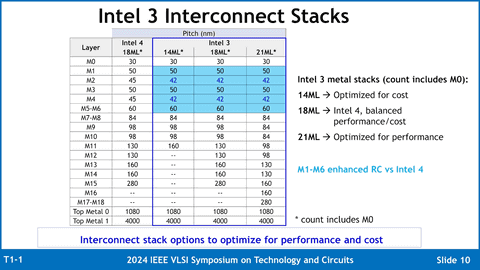

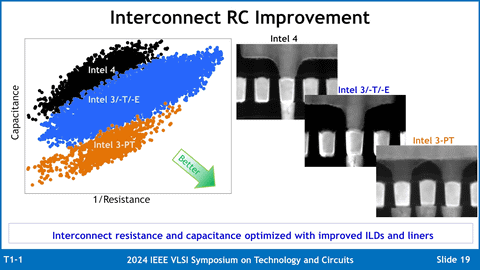

トランジスタからメタルスタックまで、プロセスにおいてほぼすべての角度で最適化を施すことで実現した。また、ライブラリは240nm高性能に加え、210nm高密度も加わった。

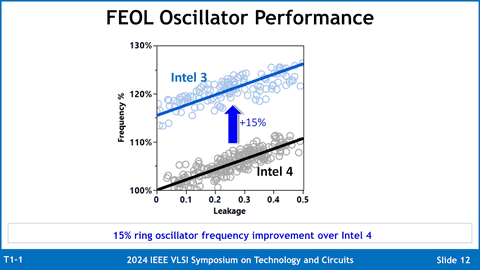

具体的には、直線的なフィンになるよう幅と高さを改善することで、より良いチャネルコントロールと低電力動作を実現。また、双極子仕事関数も導入し、低電力の性能特性を15%改善した。

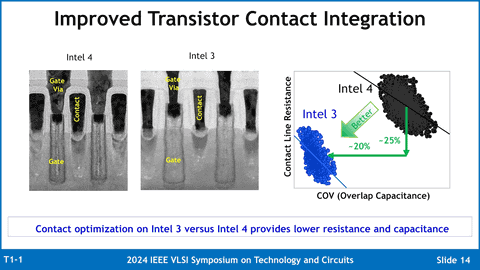

それ以外ではコンタクト、ゲート、ゲートビアの設計を改善し、スイッチング速度の低下や消費電力の増加、信号の遅延に繋がるオーバーラップキャパシタンス、そしてコンタクトライン抵抗の低減を図ることで性能向上した。

Intel 3プロセスはリスク軽減のために、Intel 3に加えて3つのバリアントが段階的に展開される。

- Intel 3-T - 複数のコンピューティングとメモリコンポーネントを1つのパッケージに統合する必要がある画像処理/高性能コンピューティング/AIなどの3Dスタッキングアプリ向けに、シリコン貫通ビア(TSV)を提供

- Intel 3-E - 外部インターフェイス、アナログ、ミックス信号機能向けにI/Oセットを追加。チップセットやストレージ向け

- Intel 3-PT - Intel 3-Eをベースに構築され、設計者にとってより使いやすくなるとともに、性能の強化、微細ピッチの9μm TSV、高密度3Dスタッキングのためのハイブリッドボンディングオプションに対応。今後何年もの間、社内外の主力となる

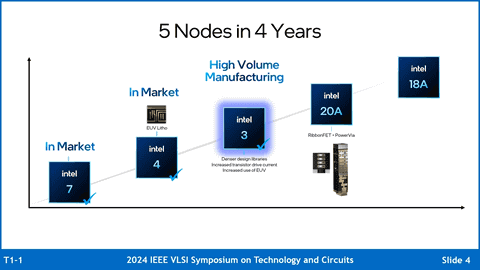

Intelは半導体製造プロセス技術のリーダーシップを取り戻すことを目指し、4年間で5つのノードを実現する「5N4Y」ロードマップを敷いたが、今回のIntel 3の実現はその一環。今後1年間で「Intel 20A」および「Intel 18A」プロセスを投入し、RibbonFETやオングストロームといった最新技術を用いるとしている。

![ASUS(エイスース) VG249QM5A ゲーミングモニター TUF Gaming ブラック [23.8型 /フルHD(1920×1080) /ワイド /240Hz] VG249QM5A 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/dtc/cabinet/mc5108/2554451.jpg?_ex=128x128)

![I-O DATA|アイ・オー・データ ゲーミングモニター GigaCrysta 3年保証 ブラック KH-GDQ271JA [27型 /WQHD(2560×1440) /ワイド /180Hz] 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/8883/00000012108334_a01.jpg?_ex=128x128)

![GOAT Summer 2026 [ 宮島 未奈 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1215/9784098021215_1_2.jpg?_ex=128x128)

![【楽天ブックス限定特典】すしらーめん りく1st写真集 さいごのふたり(限定カバー) [ すしらーめん りく ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9547/2100014909547_1_2.jpg?_ex=128x128)

![ダンダダン 23【電子書籍】[ 龍幸伸 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0120/2000019910120.jpg?_ex=128x128)

![當真あみ ファースト写真集 Ami[本/雑誌] / 屋山和樹/撮影 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/neowing-r/cabinet/item_img_1974/neobk-3058780.jpg?_ex=128x128)

![悲劇のヒロインぶる妹のせいで婚約破棄したのですが、何故か正義感の強い王太子に絡まれるようになりました 5 【電子書籍】[ 真綿マスケ ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0575/2000020430575.jpg?_ex=128x128)

![【電子版】ドラゴンエイジ 2026年6月号 【電子書籍】[ ドラゴンエイジ編集部 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7719/2000020567719.jpg?_ex=128x128)

![悪役令嬢転生おじさん(10) 【電子書籍】[ 上山道郎 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0539/2000020190539.jpg?_ex=128x128)

![Only Sense Online 23 ーオンリーセンス・オンラインー 【電子書籍】[ 羽仁 倉雲 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9038/2000020419038.jpg?_ex=128x128)

![辺境モブ貴族のウチに嫁いできた悪役令嬢が、めちゃくちゃできる良い嫁なんだが? 3 【電子書籍】[ tera ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9041/2000020419041.jpg?_ex=128x128)