福田昭のセミコン業界最前線

2022年も、半導体はおもしろい(後編)

2022年4月28日 06:17

2022年の半導体をおもしろくする、残り5個のキーワード

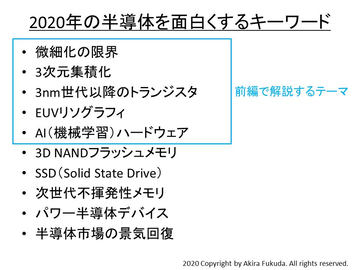

筆者が注目するテーマ(キーワード)を紹介する「半導体はおもしろい」のシリーズ、2022年版の後編をお届けする。前編では、以下の5つのキーワードについて解説した。

前編のキーワード:

1.TSMCの日本進出

2.進撃のAMD、逆襲のIntel

3.半導体の供給不足

4.半導体の自国生産

5.日本の半導体産業

後編(本稿)では、以下の5つのキーワードについて説明していく。なお前編は産業寄り、後編は技術寄りのキーワードに整理してある。また順番は、重要度の違いを意味しない。

後編のキーワード:

6.プロセッサの多様化

7.微細化の限界

8.チップレット

9.機械学習(深層学習)

10.3D NANDフラッシュメモリ

以下は、上記のキーワードに注目する理由とその近況を番号順にご説明しよう。

今さら「プロセッサの多様化」に注目する理由

最初のキーワード(テーマ)は「プロセッサの多様化」である。「何を今さら」と思われるだろう。プロセッサの歴史は多様化の歴史だとも言えるからだ。ここで改めて注目するキーワードに選んだのは、それなりの理由がある。

多くの方がご存知のように、プロセッサは汎用のCPUから始まり、特定の演算を高速に処理するプロセッサ(専用のプロセッサ)を用途別に増やしてきた。浮動小数点演算用プロセッサのFPU(Floating Point Unit)、積和演算用プロセッサのDSP(Digital Signal Processor)、グラフィックス演算用プロセッサのGPU(Graphics Processing Unit)、ネットワーク処理用プロセッサのNPU(Network Processing Unit)などが誕生した。

かつては微細化により、1枚のシリコンダイ(同じ面積)が収容する回路の規模(トランジスタ数)が技術ノード(世代)ごとに2倍に増大した。しかもシリコンダイの製造コストは前の世代と変わらなかった。そこで専用プロセッサをオンチップのアクセラレータとして搭載することで、大規模なマイクロプロセッサはSoCへと発展を遂げた。

しかし最近では、専用プロセッサをコア(マクロ)として統合するのではなく、別のシリコンダイとしてモジュール化(あるいはコプロセッサ化)する動きが強まりつつある。最初にモジュール化の動きが顕著になったのは、GPUだろう。GPUは急速な高性能化と大規模化、さらには汎用化によって独自の地位を築いた。

モジュール化の動きが強まった背景には、回路規模(トランジスタ数)の拡大と製造コストの上昇が顕著になってきたことがある。処理性能を高める手段が動作周波数の向上ではなく、マルチコア化とコア数の増強になったことがトランジスタ数の増加を招いた。微細化による製造コスト(単位面積当たりの製造コスト)の増加は、トランジスタ数の増加を抑えてシリコンダイ面積を縮小する動きを強めた。

こうなると高い処理性能を特に重視する分野では、オフチップ(別チップ化)の動きが強まらざるを得ない。2020年~2021年に特に目立ったのは、ネットワークを介した仮想化を処理するプロセッサがクラウドデータセンターのサーバー向けに登場したことだ。この専用プロセッサをNVIDIAやMarvel Technologyなどは「DPU(Data Processing Unit)」、Intelは「IPU(Infrastructure Processing Unit)」と名付けている。

DPUとIPUはいずれも、ネットワークを通じた仮想化に関連した通信処理を担う。ネットワーク処理、ストレージ管理、セキュリティ処理などである。これらの処理をCPUから省くことでCPUの実効的な処理性能を高め、サーバーのユーザーが獲得できるリソース(計算資源)を増やす。

微細化の限界がついに現実化

2番目のキーワード「微細化の限界」は、本シリーズの2020年版(前編)でも取り上げていた。変わらず重要なテーマであり、しかも限界を突破する見通しは立っていない。

「微細化」とは半導体製造技術で加工可能な寸法が細くなることを意味する。寸法は、半導体ウェハの表面に平行な方向(「横方向」とも呼ぶ)で定義する。トランジスタの大きさであったり、配線の幅であったり、コンタクト(電極)の直径であったりする。微細化には共通認識となる世代(技術ノード)があり、2022年3月時点で量産中の最先端世代は「5nm世代(「N5世代」とも呼ぶ)」となっている。

「微細化」が限界に達するのは、粗く言ってしまうと微細化によるメリット(利点)がなくなってしまうからだ。西暦2000年以前には、「消費電力の低減」、「動作周波数の向上」、「集積規模の拡大」、「集積密度の向上」といった豊富な果実を微細化によって入手できた。

ところが7nm世代~5nm世代では、微細化による果実がほとんど収穫できない。辛うじて収穫できるのは、「集積密度の向上」だけだろう。「消費電力の低減」、「動作周波数の向上」、「集積規模の拡大」は、微細化以外の要素技術の開発によってもたらされている。

この結果、微細化によって製造プロセス(ウェハ当たり)のコストが世代ごとに30%前後も上昇するという、憂慮すべき事態が進行している。シリコンダイ面積を前の世代よりも30%縮小しないと、ダイ当たりの製造コストが前の世代と同じにならない。微細化によって集積密度が2倍(一般的な目安)に増えても、同じコストで作れる面積が0.7倍だと、同一コストで製造できる集積規模(トランジスタ数)は1.4倍にとどまることになる。

さらに心配なことがある。将来世代の姿が以前に比べると見えなくなっているのだ。半導体製造技術の研究開発では過去、量産中の最先端世代よりも「2世代」進んだ量産技術(次々世代技術)が「かなり確実に」見えていた。しかし最近では、「次々世代は確実」という前提が崩れてきた。あるいは、将来世代の定義を変更することで「次々世代は確実」という前提を維持しようとしているように見える。

2022年(今年)は、3nm世代の量産開始が確実視されている。にもかかわらず、2nm世代の量産技術の姿は従来に比べると確実になっていない。その先は五里霧中だ。ひょっとしたら、量産に適用する技術世代は2nm世代が最後となるかもしれない。

チップレットが「ムーアの法則」を継続させる

3番目のテーマである「チップレット」は、「微細化の限界」と密接に関連している。チップレットの定義は曖昧だが、ここでは以下のように定義しよう。本来であれば技術的にシングルダイのSoCで製造可能なチップを、何らかの理由で複数の小さなダイ(ミニダイ)に分割し、SoCと同様の性能を備えたモジュールで実現することを指す。

従来、複数のシリコンダイで構成したモジュールは「マルチチップモジュール」と呼ばれてきた。チップレットはマルチチップモジュールの一種ではあるものの、成り立ちが違う。マルチチップモジュールは、製造技術の大きく異なる複数の半導体ダイを1個のモジュールにまとめた製品という性格が強い。例えばパワー半導体(シリコンではなく、化合物半導体のこともある)デバイスとシリコンの制御回路チップを組み合わせたり、ロジックのチップとメモリのチップを組み合わせたり、といったモジュールが開発されてきた。

これに対してチップレットは、以前の製造技術世代ではSoCで実現していたチップ(シングルダイ)を、技術世代を進めるときに複数の小さなチップ(ミニダイ)に分割する。和文では単数形と複数形の区別が難しいので分かりにくいが、英文では個々のミニダイを「Chiplet」と表記し、ミニダイを組み合わせたモジュールを「Chiplets」と表記して区別している。

シングルチップのSoCで実現できるものをわざと複数のチップレットに分割するメリットあるいは理由はいくつか存在する。SoCの内部回路には微細化が難しい回路ブロックが含まれているからだ。その代表が入出力回路である。入出力インターフェイスは共通の技術仕様に準拠することが多い。例えば電源電圧が決まっている。SoCに残しておくと入出力回路は製造技術の微細化を進められず、SoCに占める面積が相対的に増大してしまう。

そこで入出力回路はミニダイに切り出して微細化せず、ロジックなどの微細化に適したミニダイに次世代の製造技術を適用する。プロセスコストの高い次世代技術を適用するシリコンの面積が大幅に減るので、モジュール化のコストを差し引いても、SoCに比べると製造コストが下がる。

この考え方をさらに進めると、ロジックだけでもシングルチップ(SoC)に比べるとチップレットの製造コストが低い、というケースが出てくる。ハイエンドのマイクロプロセッサが性能向上のためにCPUのコア数を増やすケースを想定しよう。2021年8月に開催された国際学会「Hot Chips 33」でAMDがこのようなケースを説明している。

CPUコアを数多く搭載した巨大なシリコン面積のシングルダイ(SoC)を4枚のチップレット(ミニダイ)に分割する。ミニダイには区別はなく、同じ回路を載せる。同じ大きさのウェハから、シングルダイでは13枚、ミニダイでは45枚のシリコンダイを製造できると仮定する。単純計算では13枚の4倍で52枚になるが、実際にはオーバーヘッドがあるので45枚というのは現実的だろう。

ウェハ当たりの欠陥数を7個と仮定する。すると実際の取れ高は、シングルダイが6枚、ミニダイが38枚になる。シングルダイと同等機能のチップレット(モジュール)は9個となり、シングルダイよりも多く作れる。すなわち製造コストが下がる。

チップレット技術はシリコンダイの微細化が限界を迎えつつある現在、「ムーアの法則」を牽引する有力候補となりつつある。それはミニダイを垂直方向に積層した3次元(3D)のチップレット技術である。積層するミニダイの枚数を増やすことで、実質的な集積密度と集積規模(トランジスタ数)を拡大できる。現在は、積層したミニダイの枚数は2枚とそれほど多くない。今後の研究開発に期待がかかる。

機械学習が半導体の産業と技術を力強く牽引

4番目のキーワード(テーマ)は「機械学習(深層学習)」である。本シリーズの2018年版では「深層学習(ディープラーニング)」、2020年版では「AI(機械学習)ハードウェア」のキーワードで扱っていた。産業(市場)と技術(研究開発)の両面で、半導体にとって極めて重要なテーマだと言える。

本シリーズの2020年版では、「AIハードウェア」について「AIハードウェアの研究ブームがこの先、どこまで続くかはまだ不透明だ」と懸念を表面していた。しかし幸いなことに、この懸念は杞憂に終わった。それどころか、機械学習は人類文明の進化を後押しする基幹技術となりつつあるように見える。そして半導体の産業と技術を力強く牽引している。この状況は人類文明の終わりまで、続くかもしれない。

半導体技術の主な国際学会で機械学習(および人工知能)関連の論文が増加したのは、2010年代半ばのことだ。2019年に本コラムでご報告したように、国際学会VLSIシンポジウムで発表された機械学習および人工知能関連の採択論文は、2011年~2015年は3件以下だったのに対し、2016年は5件、2017年は8件、2018年は18件、2019年は23件と増加した。

2020年には、半導体回路技術の国際学会ISSCCが新たに「機械学習」のカテゴリを設けた。2019年まで、ISSCCではいくつかの異なるカテゴリ(デジタルアーキテクチャやメモリ、次世代技術など)で機械学習関連の研究成果が発表されていた。機械学習関連の投稿数が急速に増加したことで、投稿する研究者が迷わないように「機械学習」を新設した(どのカテゴリに投稿するかの判断は、投稿者が決める)。

3D NANDフラッシュメモリの積層セル数は200を突破

最後を飾るキーワード(テーマ)は「3D NANDフラッシュメモリ」である。NANDフラッシュメモリは、大規模な半導体集積回路の中では最も早く微細化の限界に達した。メモリセルを垂直方向(縦方向)に3次元(3D)積層することで、微細化の限界を突破した最初の製品とも言える。

NANDフラッシュメモリの記憶密度(平方mm当たりの記憶容量)は、年率1.4倍で向上してきた。10年だと記憶密度は30倍強に高まる。この向上ペースを維持することが、NANDフラッシュに与えられた最重要課題だ。3次元化と積層数の増加(高層化)、多値記憶技術の多ビット化などによって現在まで、このペースは維持されてきた。

記憶密度の向上に最も寄与する高層化は、2021年の時点で176層に達している。2022年にはついに200層を突破した。同年2月に開催された国際学会ISSCCでSamsung Electronicsが220層を超える積層数の1Tbitシリコンダイを発表した。同じISSCCでWestern Digitalとキオクシアの共同開発チームは、記憶密度が15.0Gbit/平方mmと過去最高を更新する3D NANDフラッシュを試作してみせた。記憶密度の向上はまだ続きそうだ。

![Microsoft|マイクロソフト ノートパソコン 特別モデル Surface Pro 12インチ プラチナ + キーボード(スリムペン付き)+ 充電器 EP2-46399 [Copilot+ PC /12.0型 /Windows11 Home /Snapdragon X Plus /メモリ:16GB /UFS:256GB /M365 (24か月) or Office 選択可能] 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/15530/00000014704980_a01.jpg?_ex=128x128)

![IOデータ ゲーミングモニター KH-GD251UH 240Hz&フルHD対応 GigaCrysta [24.5型 / フルHD(1920×1080) / ワイド / 240Hz] ブラック 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001504/4957180184845_1.jpg?_ex=128x128)

![怠惰な悪辱貴族に転生した俺、シナリオをぶっ壊したら規格外の魔力で最凶になった Vol.3 【電子書籍】[ 菊池 快晴 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9037/2000020419037.jpg?_ex=128x128)

![【楽天ブックス限定特典】MGA MAGICAL 10 YEARS ANNIVERSARY BOOK -OUR STORY-(限定絵柄ポストカード1枚) [ Mrs. GREEN APPLE ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2004/2100014772004_1_2.jpg?_ex=128x128)

![チャイロイコグマの10th Anniversary BOOK (生活シリーズ) [ サンエックス ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5606/9784391645606.jpg?_ex=128x128)

![転生したらスライムだった件(32) (シリウスKC) [ 川上 泰樹 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7544/9784065437544_1_2.jpg?_ex=128x128)

![地球の歩き方 スター・ウォーズ [ 地球の歩き方編集室 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6939/9784058026939_1_2.jpg?_ex=128x128)

![大きな活字の新明解国語辞典 第八版 [ 山田 忠雄 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0873/9784385130873.jpg?_ex=128x128)

![takt op. 運命は真紅き旋律の街を OFFICIAL ARTWORKS [ DeNA ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1385/9784768331385_1_5.jpg?_ex=128x128)