福田昭のセミコン業界最前線

微細化の限界と発熱の課題にどう向き合う?imecが2040年までの半導体技術を指し示す

2026年4月24日 06:04

ベルギーの半導体研究開発組織imecは、2020年代~2040年代の半導体製造技術がどのように進化していくかの研究開発ロードマップを示すとともに、いくつかの注目すべき要素技術を解説した。3月25日に、国際学会「国際信頼性物理シンポジウム(IRPS: IEEE International Reliability Physics Symposium)」の基調講演(講演番号KN3)で明らかにした。

水平方向の微細化は2010年代後半に限界に達した

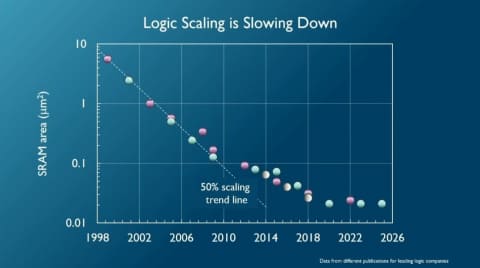

まず重要な事実として、水平方向の微細化は2010年代後半に限界に達したということがある。SRAMセル面積の縮小トレンドは「2年で半分(加工寸法は2年で0.7倍)」が2010年前後まで維持されてきた。その後は「4年で半分」の縮小トレンドに鈍化した。2012年~2018年ごろのことだ。

そして2020年以降は技術ノードの世代が進化しても、SRAMのセル面積はほとんど変化がない。標準的な6トランジスタのセル面積だと、0.025平方μm~0.023平方μmが下限となったままだ。

垂直方向、新材料、3次元接続で半導体デバイスの進化を継続

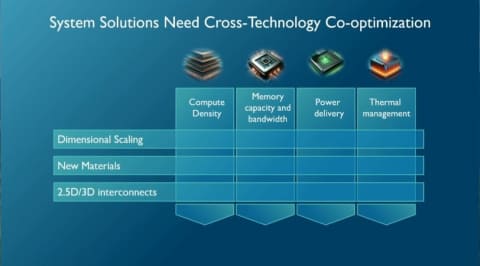

水平方向の微細化が限界を迎えた状況でも、半導体集積回路の高密度化と高性能化は継続しなければならない。AI/HPC分野では依然として、高密度化と高性能化の要求が強い。

そこで水平方向だけでなく垂直方向も考慮した「3次元のスケーリング」、トランジスタと配線における「新しい材料」の導入、「2.5/3次元の相互接続」技術といった要素技術の活用によって半導体デバイスの高密度化と高性能化を推し進める。一方でメモリアクセスのボトルネック化、安定な電源供給の難度上昇、消費電力の急増および放熱技術の強化といった課題がAI/HPCシステムの性能向上を阻害しており、異なる技術の協調による最適化が求められつつある。

ロジック向け技術ノードの改良は今後20年続く

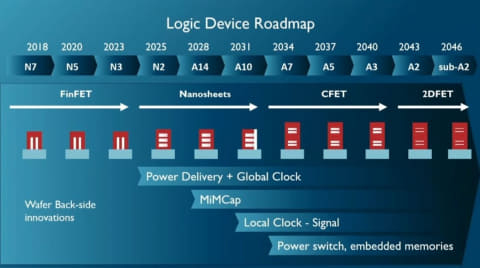

そして半導体ロジックの技術ノードは、2020年代はもちろんのこと、2040年代に至るも進化を止めない。imecが講演で示した半導体ロジックの技術ノードは、量産開始の2018年の「N7(7nm)ノード」から2046年の「サブA2(2オングストローム未満)ノード」までと28年におよぶ。今年(2026年)から数えると、20年後まで技術ノードの改良が続くことになる。なおオングストローム(Å)は、nmの10分の1の長さを意味する単位である。

FET(電界効果トランジスタ)技術で見ていくと、2018年のN7ノードと2020年の「N5(5nm)ノード」、2023年の「N3(3nm)ノード」はFinFET(フィンFET)技術を継続してきた。2025年の「N2ノード」からは、ナノシートFET(別名:GAA(ゲートオールアラウンド) FET)が選択されている。ナノシートFETは、2028年の「A14(1.4nmあるいは14オングストローム)ノード」と、2031年の「A10(1.0nmあるいは10オングストローム)ノード」でも改良され、使われるとimecは予測する。

そして2034年の「A7(0.7nmあるいは7オングストローム)ノード」では、FET技術が相補型FET(CFET: Complementary Field Effect Transistor)に替わる。CFETは、pチャンネル型ナノシートFETとnチャンネル型ナノシートFETを垂直に積層したトランジスタであり、原理的にはCMOSロジックのトランジスタ密度がナノシートFETの1.6倍~1.8倍に高まるとされる。2037年の「A5(0.5nmあるいは5オングストローム)ノード」、2040年の「A3(0.3nmあるいは3オングストローム)ノード」でもCFETの改良品が継続して使われる。

2043年の「A2(0.2nmあるいは2オングストローム)ノード」からは、CFETのナノシート型チャンネルの材料を「2次元材料」に変更した「2D FET」が使われると予測する。2D FETは2046年の「サブA2ノード」でも採用される。

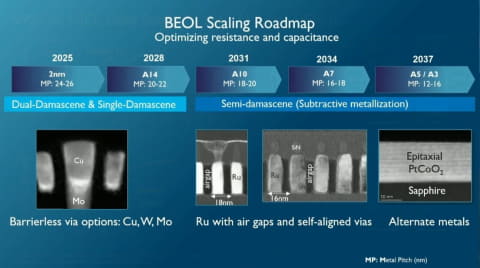

2025年~2037年の配線技術ロードマップ

半導体ウェハに大規模ロジック回路を作り込むプロセスは、トランジスタを形成するFEOL(Front End Of Line)と、多層配線を形成するBEOL(Back End Of Line)に大別される。通常はトランジスタを作り込んだ後に、トランジスタ間を接続する配線(多層配線)を形成するので、プロセスの順序としては始めがFEOL、次がBEOLとなる。

先ほどのロードマップは主に、FEOLで作るトランジスタ技術を技術ノードと併記したものだ。imecはBEOLのロードマップも講演で示した。BEOLのロードマップがカバーする時間的な範囲は、FEOLのロードマップに比べるとかなり狭い。2025年の2nmノード(N2ノード)から、2037年のA5/A3ノードまでとなっている。

2025年のN2ノードに対応する配線技術は、最小ピッチが24nm~26nm、配線金属は銅(Cu)、形成技術はデュアルダマシン法およびシングルダマシン法である。次に来るとされる2028年のA14ノードでは、最小ピッチが20nm~22nmに縮まる。基本的にはN2ノードの改良で実現する。

2031年のA10ノードになると、配線の最小ピッチは18nm~20nmとさらに短くなる。配線金属の有力候補はルテニウム(Ru)、隣接配線間絶縁の有力候補はエアギャップ(空隙)である。Ru配線だと、配線形成技術はサブトラクティブ法に変わる。ビア(層間を繋ぐ孔)の加工には自己整合技術を駆使する。

続く2034年のA7ノードでは、最小ピッチを16nm~18nmに縮める。Ru金属とエアギャップ、自己整合ビアの組み合わせと改良によって最小ピッチを詰める。2037年のA5ノードでは配線の最小ピッチを12nm~16nmとさらに縮めたい。実現技術については、現時点では流動的だ。

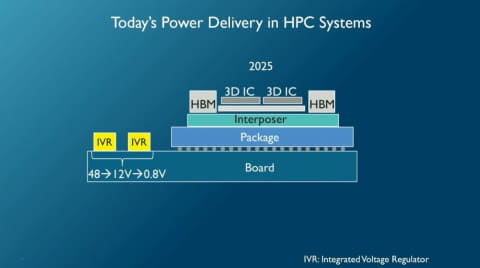

2025年~2032年の電源供給技術ロードマップ

imecはさらに、HPC向けの先進パッケージを搭載したボード(プリント回路基板)の電源供給技術についても将来を展望した。現在の電源供給技術は、プリント回路基板の表面に複数の「統合化定電圧回路(IVR: Integrated Voltage Regulator)」モジュールを搭載して電源電圧を直流48Vから直流12V、さらには直流0.8Vへと降圧する。

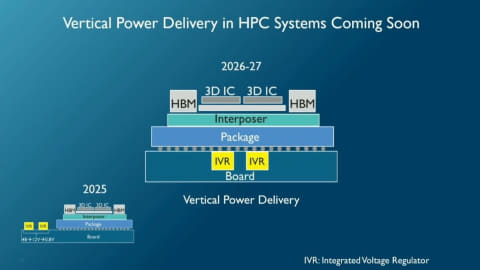

2026年~2027年には複数のIVRをボード内部に埋め込んだ電源供給技術が登場する。ボードの面積が減るともに、IVRと半導体チップ(3D ICおよびHBM)の距離が縮まる。電源回路の電気抵抗と静電容量が減ることで電源供給の効率向上と雑音抑制が見込める。

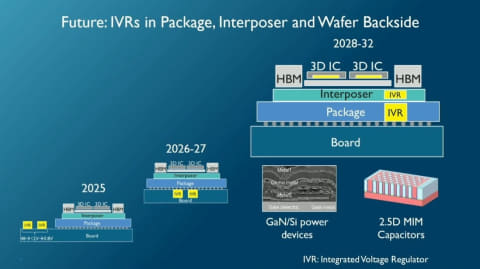

将来は、パッケージ基板と中間基板(インターポーザ)、半導体チップ(3D IC)裏面にIVRを埋め込む。2028年~2032年にはこのような、次々世代の電源供給技術を選択したHPCモジュールが実現すると予測する。また窒化ガリウム(GaN)オンシリコン(Si)技術によるパワーデバイスのモノリシック集積技術、金属(Metal)と高誘電率絶縁膜(Insulator)、金属による2.5次元(2.5D)大容量MIMキャパシタ技術が効率向上と雑音低減のために採用される可能性がある。

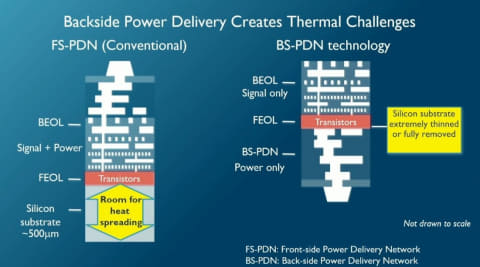

裏面電源供給網(BS-PDN)は放熱性が低下

2028年~2032年の電源供給技術として注目されるのが、シリコンダイの「裏面電源供給網(BS-PDN: Back-side Power Delivery Network)」技術である。従来はウェハの表面側に信号配線と電源配線(接地含む)をレイアウトしてきた。BS-PDNと区別するため、「FS-PDN(Front-side Power Delivery Network)」と呼ぶ。

従来のFS-PDN技術では表面側に信号配線と電源配線が混在していた。信号配線に比べると電源配線は最大電流が極めて高い。水平方向の微細化によって信号配線は細くできる。しかし電源配線は電流密度の増加によるエレクトロマイグレーション寿命の懸念があり、あまり細くできない。その結果、信号配線のレイアウトが阻害される。

そこで電源供給網を裏面側に移転させたのがBD-PDNである。表面側は信号配線層だけとなり、レイアウトが容易になるとともに信号配線の密度が高まる。

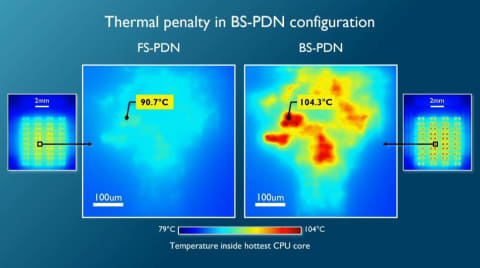

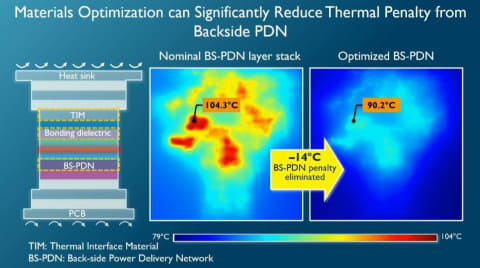

BS-PDNの弱点は、放熱性能が著しく悪化することだ。FS-PDNでは裏面側の基板が熱拡散の経路として機能していた。BS-PDNでは電源配線を除くと裏面側の厚みはないに等しい。電源系を除くと熱拡散の経路が消失し、放熱性が低下する。

CPUコアアレイで動作時の最高温度を比較すると、FS-PDNでは90.7℃に留まっていたのに対し、BS-PDNだと104.3℃に上昇する。温度上昇の幅は14℃弱に達する。

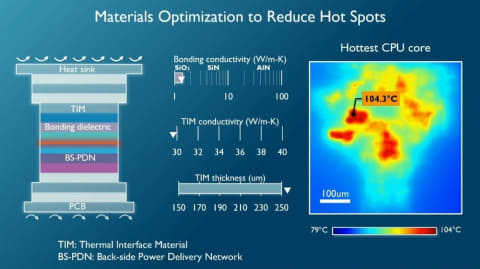

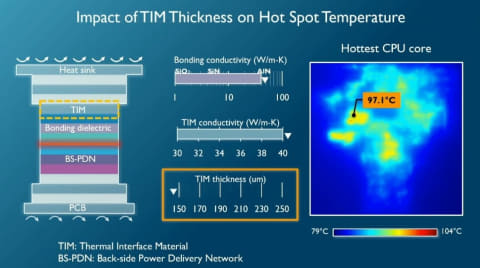

裏面電源供給網(BS-PDN)の放熱性能を高める

そこで放熱性能の向上を試みた。表面側と裏面側を接合する誘電体材料を熱伝導率の高い材料に変更するとともに、熱伝導材料(TIM: Thermal Interface Material)も熱伝導率のより高い材料に変更する。さらにTIMは、厚みを減らす。これらの対策によって最高温度は97.1℃まで下がった。

具体的には、接合部の誘電体材料を従来の二酸化シリコンから窒化アルミニウムに変更することで、熱伝導率を40倍に高めた。TIMの熱伝導率は材料変更によって1.33倍に向上させた。TIMの厚みは当初の6割に薄くした。

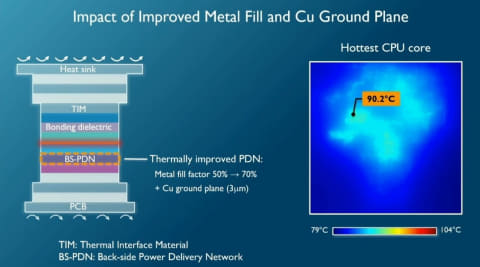

さらに、裏面電源供給網の金属比率を従来の50%から70%に高めるとともに、銅の接地層を3μmの厚みで設けた。この結果、最高温度は90.2℃にまで低下した。対策を施すことにより、FS-PDNの最高温度90.7℃よりも低い温度を達成できた。

当然ながら、これらの放熱対策はコストの上昇を招く。妥協点を見出すことが量産では重要になるだろう。

![HP Elite Mini 800 G9(Win11x64) 中古 Core i5-2.0GHz(12500T)/メモリ8GB/SSD256GB [C:並品] 2022年頃購入 製品画像:8位](https://thumbnail.image.rakuten.co.jp/@0_mall/usedpc/cabinet/url1/5725918c.jpg?_ex=128x128)

![DELL デル スリム ECS1250 [モニター無し / Win11 Home / intel Core i3 / メモリ8GB / SSD512GB / 2026年春モデル] ブラック SD20-GH 製品画像:5位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001729/4573661276412_1.jpg?_ex=128x128)

![[★ケーブルセット価格] EIZO FlexScan EV2451 23.8インチ ワイド 液晶モニター ブラック フルHD フレームレス IPSパネル フリッカーフリー 非光沢 ノングレア HDMI DisplayPort DVI VGA 縦置き可 フレームレス スイーベル機能 高さ調整 23.8型 PCモニター 中古モニター 中古 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-shinjyo/cabinet/monitor/pc-ev2451.jpg?_ex=128x128)

![液晶ディスプレイ アイ・オー・データ LCD-A241DB [液晶ディスプレイ 23.8型/ブラック/5Y/3辺フレームレス] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage28/1264173.jpg?_ex=128x128)

![LENOVO|レノボジャパン PCモニター L24-4C クラウドグレー 67DDKAC6JP [23.8型 /フルHD(1920×1080) /ワイド /144Hz] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/16440/00000014962075_a01.jpg?_ex=128x128)

![棺桶まで歩こう (幻冬舎新書) [ 萬田緑平 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7937/9784344987937_1_5.jpg?_ex=128x128)

![[新品]金色のガッシュ!! 完全版(1-16巻 全巻) + 20周年記念オリジナル収納BOX付セット 全巻セット 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0052/m0019400091-spbox_01.jpg?_ex=128x128)

![角川まんが学習シリーズ 日本の歴史 5大特典つき全16巻+別巻5冊セット [ 山本 博文 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3680/9784041153680_1_17.jpg?_ex=128x128)

![第一生命最大たるより、「最良」たれ 「人」と「経営品質」で挑む変革の物語 [ 高橋利雄 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0520/9784820120520.jpg?_ex=128x128)

![FINEBOYS+plus Share vol.4 [ 日之出出版 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5154/9784838795154.gif?_ex=128x128)

![【楽天ブックス限定特典】KEITA MACHIDA 15th Anniversary Photobook 「sign」(限定トレカ) [ 町田啓太 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1991/2100014771991_1_3.jpg?_ex=128x128)

![おいしい!イラストレッスン クレパスで描きました [ momo ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1558/9784522441558_1_2.jpg?_ex=128x128)

![カイシャがなくなる日 組織と働き方の進化論 (BOW BOOKS 036) [ 名和 高司 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6418/9784502556418_1_6.jpg?_ex=128x128)

![角川まんが学習シリーズ 世界の歴史 3大特典つき全20巻+別巻2冊セット [ 羽田 正 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3710/9784041153710_1_9.jpg?_ex=128x128)