福田昭のセミコン業界最前線

過渡不良や間欠不良の脅威。AMDが解説するデータセンターの信頼性と最新対策

2026年4月9日 06:07

半導体デバイスと電子システムの信頼性技術に関する世界最大の国際会議「国際信頼性物理シンポジウム(IRPS: IEEE International Reliability Physics Symposium)」が3月26日に閉幕した。開催地は米国アリゾナ州ツーソンのリゾートホテル「Loews Ventana Canyon Resort」である。

最終日である26日の夕方には一般講演セッションの完了後に、IRPS 2026のまとめと次回の予告を兼ねた閉会挨拶が実施された。セレモニーの前半では、開催の準備から開催中の会場内までをスナップ写真で紹介していた。

セレモニーの後半では、次回の開催日と開催場所が告知された。IRPS 2027の開催予定日は2027年3月21日~25日、開催場所は米国カリフォルニア州サンディエゴのリゾートホテル「Town & Country Resort」である。サンディエゴの平均的な気温は3月に最高が19℃、最低が12℃で、酷暑だった今年のツーソン開催に比べ、はるかに過ごしやすそうだ。

データセンター全体の不良率を決める3つの要素

ここからは、最終日の始めに実施されたキーノート講演の概要を紹介していこう。AMDのVilas Sridharan氏が「Data Center Reliability: What Have We Learned?(データセンターの信頼性: われわれは何を学んできたか?)」のタイトルで、最新データセンターのハードウェア不良とその対策を解説した。

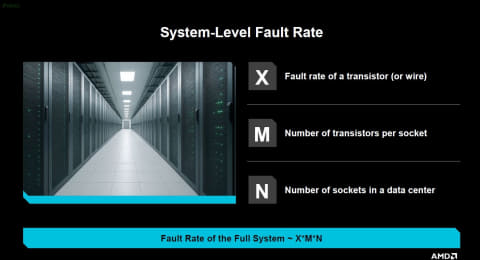

データセンターに代表されるコンピューティングシステムの不良率は、以下のように定義される。トランジスタ(あるいは配線接続)の不良率を「X」、1個のソケット(あるいは部品)が内蔵するトランジスタ(あるいは配線接続)の数を「Y」、データセンターシステムが搭載するソケット(あるいは部品)の数を「N」と仮定する。

システム全体の不良率はXとY、Nをかけ合わせたものになる。粗くまとめてしまうと、トランジスタや配線接続などの不良率Xが一定の条件下では、トランジスタや配線の数Y/Nが増えると不良率は比例して増加する。システムの不良率を一定に維持するためには、トランジスタや配線などの不良率を継続的に下げる必要がある。

システムの規模を拡大しつつ、信頼性を維持する、あるいは、不良率を一定以下に保つには、システムを構成する要素(スタック)での改良とスタック間の連携が欠かせない。プロセス、設計、アーキテクチャ、ソフトウェアが協調して回路規模の拡大とトランジスタ数の増加による悪影響の緩和に取り組むことが求められる。

コストの増加を抑えつつ信頼性を高める、それがECC

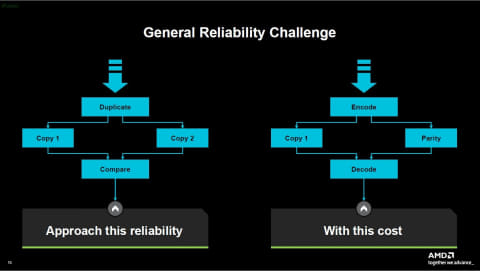

コンピューティングシステムの信頼性を高める単純な手法は「多重化」だろう。その中でも基本的な手法は「二重化」である。同じ回路を2つ用意し、同じ入力データに対する2つの出力結果を比較する。何らかの不具合が生じていれば、2つの出力結果が違ってくる。このことから、不良を検出する。

ただし二重化は同じ回路を2つ用意するので、単純計算では回路のコストが2倍になってしまう。大規模なシステムで許容可能な手法とは言えない。

そこで通常は、誤り検出/訂正用の符号データを追加する手法を採用している。元のデータを符号化(エンコード)して誤り検出/訂正用のデータを追加してから入力する。出力データを復号(デコード)すると、不良発生の有無が分かる。

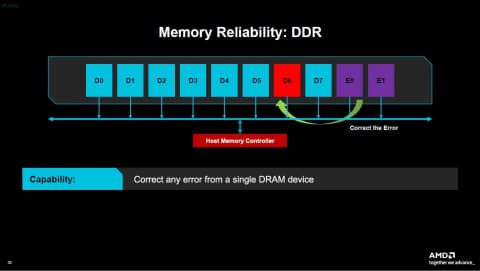

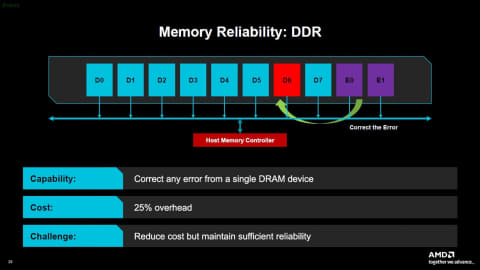

誤り検出/訂正(ECC: Error Check and Correct)用の符号データを追加する手法の標準的な事例が、DDR系DRAMの主記憶である。ECC機能を備えた主記憶は「ECCメモリ」と呼ばれることが少なくない(なお誤り訂正符号を「ECC(Error Correction Code)」と呼ぶこともあるので注意されたい)。

ここでは「D0」~「D7」までのDRAMデバイスと、「E0」および「E1」の誤り検出/訂正用DRAMデバイスで構成されたサブシステムを考える。D0~D7までのDRAMデバイスの中でどれか1個にデータ不良が発生した場合はE0とE1のデータ(誤り訂正符号)を使ってデータを訂正できる。

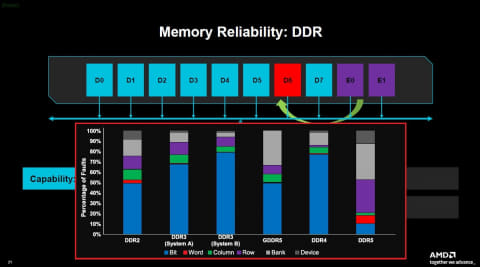

DRAMユーザーであるAMDの実績データでは、過去にDDR2世代からDDR4世代のDRAMで発生した不良(修正前不良)の50%~80%はビット不良(マルチビットの不良を含む)だった。ECC機能を備えたDDR系DRAM主記憶は、不良率の低減に大きく寄与したことが分かる。

オンダイECC機能を備えるDDR5世代の影響と、HBMのECC機能の強化

ECCメモリのサブシステムは8個のデバイスに2個の誤り訂正用デバイスを追加している。メモリコスト(デバイスのみ)は誤り訂正なしに比べると25%増加する。システムの部品コストに占めるDRAMコストの比率はかなり大きく、25%の増分は無視しづらい。

しかも最新世代のDDR5 DRAMは、オンダイECC機能を備える。サブシステムが備えるECC機能は1デバイスのビット誤りを対象とする。2デバイスが同時に誤りを生じた場合や、周辺回路の不具合などには対応していない。DDR5 DRAMの不良は90%がビット以外の不良なので、ECCメモリの意義が薄れている。

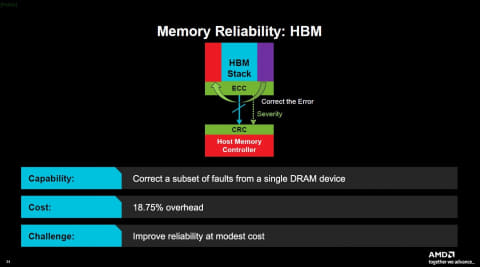

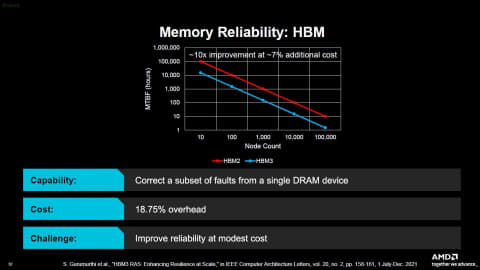

誤り訂正機能を備えながらもコスト増分がDDR系DRAMサブシステムよりも低い広帯域DRAM製品が、HBM(High Bandwidth Memory)である。HBMはオンダイECC機能を搭載しており、誤りが発生するとデータを修正するとともに誤りの重要度(Severity)をメモリコントローラに送信する。コスト増分は18.75%で、DDR系DRAMサブシステムのECC機能よりも少ない。

そしてHBM2世代からHBM3世代への改良では、可用性を強化した。平均故障間隔(MTBF: Mean Time Between Failure)を10倍に延ばすとともに、コストの増分を7%前後に抑えた。

プロセッサの厄介な不良である「過渡不良」と、さらに厄介な不良の「間欠不良」

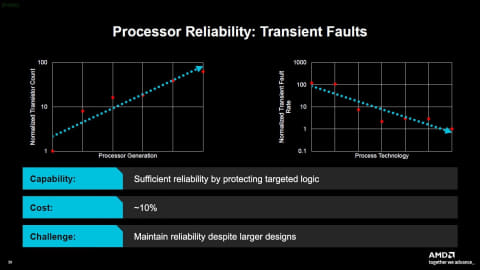

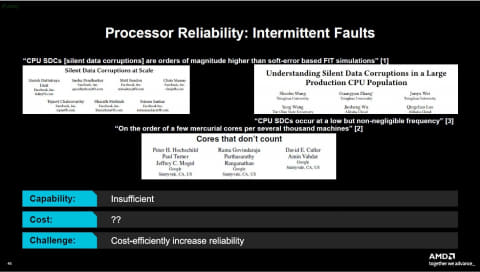

ビット反転が主体であるメモリの不具合に比べると、プロセッサで発生する不具合の様相は複雑かつ厄介に見える。講演では、主に2つの不良モードについて説明した。1つは「Transient Faults(過渡不良)」、もう1つは「Intermittent Faults(間欠不良)」である。

過渡不良は一過性の不良あるいは不具合であり、論理値が反転したり、信号波形が揺らいだりする。リセット動作や電源の再投入動作などによって正常な動作に戻る。ハードウェアは故障していない。このため「ソフトエラー」とも呼ばれる。

過渡不良の要因には、放射線(宇宙由来の高速中性子や熱中性子、パッケージ樹脂由来のアルファ粒子など)、電磁干渉、クロストークなどがある。1970年代末にアルファ粒子がDRAMのビット不良を引き起こすことが判明してから、DRAMでは放射線耐性が標準仕様の1つとなった。プロセッサでソフトエラーが問題になり始めたのは、ここ25年ほどだ。

プロセッサや大規模ロジックなどでは、クリティカルパスを放射線から保護する対策が採られる。コストの増分は10%ほどだという。

間欠不良はさらに厄介だ。間欠的に発生することから、このように総称される。放射線ソフトエラーと同様に、いつ発生するかは予測できない。不良の発生が把握しにくいにもかかわらず、その発生率は放射線ソフトエラーの発生率予測を超えるとされる。「無兆候データ破壊(SDC: Silent Data Corruptions)」、「無兆候データ破損」などと呼ばれることが多い。

SDCの最も重大な問題は、データが破壊されたことをシステムが認識していない可能性にある。論理値やデータ値などの反転や化けなどが起こっても、異常とは検出されない。こうなると、誤った論理値やデータ値などをシステムが利用することになってしまう。

無兆候データ破壊の影響と対策、およびその効果については不明な点がまだ少なくない。今後の研究に期待したい。

![★☆エイスース / ASUS Chromebook CX1 CX1102CKA-N00010 [トランスペアレントシルバー]【ノートパソコン】【送料無料】 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/e-cutestyle/cabinet/img042/p000000831518_1.jpg?_ex=128x128)

![デスクトップパソコン LAVIE A23 [23.8型 /intel Core i5 /メモリ:16GB /SSD:512GB] ファインブラック NEC PC-A2355JAB 母の日 ギフト 2026 贈り物 プレゼント 母 父 父の日 ペアギフト 製品画像:3位](https://thumbnail.image.rakuten.co.jp/@0_mall/b-surprise2/cabinet/cm168/4589796419846.jpg?_ex=128x128)

![INNOCN 25G1H [24.5型ゲーミングモニター/240Hz/Display Portx2、HDMIx2] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage33/1289757.jpg?_ex=128x128)

![ASUS エイスース 液晶ディスプレイ Eye Care [ 27型 / フルHD(1920×1080) / ワイド ] VA279HG 製品画像:20位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001484/4711387813294_1.jpg?_ex=128x128)

![公共建築改修工事標準仕様書(建築工事編)(令和7年版) [ 国土交通省大臣官房官庁営繕部 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2773/9784907762773_1_2.jpg?_ex=128x128)

![永年雇用は可能でしょうか(6) 【電子書籍】[ 梨川リサ ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/1808/2000020391808.jpg?_ex=128x128)

![ボンボンドロップシール パーフェクトBOOK 公式ファンブック (アサヒオリジナル) [ 朝日新聞出版 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7671/9784022727671_1_4.jpg?_ex=128x128)

![百姓貴族(9) (ウィングス・コミックス・デラックス) [ 荒川 弘 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1951/9784403671951_1_2.jpg?_ex=128x128)

![住みにごり(10) 【電子書籍】[ たかたけし ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9499/2000020239499.jpg?_ex=128x128)

![小学新漢字辞典三訂版 (光村の辞典) [ 甲斐睦朗 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0175/9784895720175.jpg?_ex=128x128)

![[新品]サザエさん (1-68巻 全巻) 全巻セット 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0051/m5220421088_01.jpg?_ex=128x128)

![異世界のんびり農家 20.5 【電子書籍】[ 内藤 騎之介 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0725/2000020390725.jpg?_ex=128x128)