福田昭のセミコン業界最前線

サブナノメートル時代のAIチップを支えるトランジスタ技術

2025年10月29日 06:20

FET誕生100周年が今年のメインテーマ

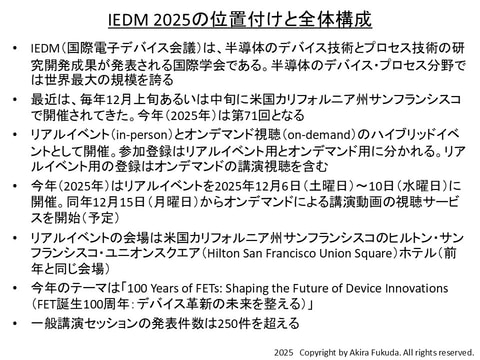

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)(通常の呼称は「アイイーディーエム」、日本語の通称は「国際電子デバイス会議」)」が、米国カリフォルニア州サンフランシスコで2025年12月6日(土曜日)~10日(水曜日)に開催される。昨年に続き、リアル(in-person)とバーチャル(on-demand)のハイブリッド形式となる。通称は「IEDM 2025」である。

リアルイベントの会場はヒルトン・サンフランシスコ・ユニオン・スクエア(Hilton San Francisco Union Square)ホテルで、最近は変わっていない。バーチャル(on-demand)イベントはリアルイベントの閉幕後となる。12月15日(月曜日)に講演の動画配信を始める。なお一部のイベント(パネル討論会など)は動画配信に含まれない。

IEDM 2025の基本的なスケジュールは、前年と変わらない。始めの2日間(12月6日~7日)は、プレイベントとなる。6日(土曜日)は「チュートリアル」と呼ぶ1件ずつのテーマ別講演、7日(日曜日)は「ショートコース」と呼ぶ共通テーマに基づく複数の講演を予定する。

続く3日間が、メインイベントの技術講演会(テクニカルカンファレンス)となる。技術講演会の初日午前は、開会挨拶とプレナリー講演(基調講演)を予定する。初日午後からは、一般講演セッションとなる。3日目の午後までに250件を超える数多くの研究成果が披露される。

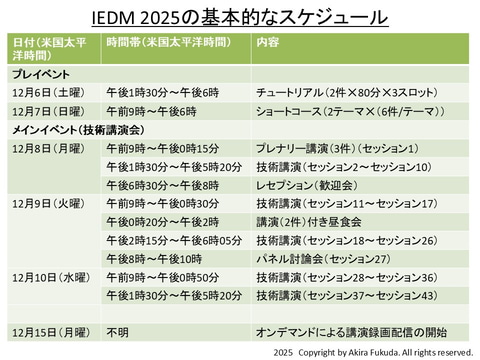

11月10日(米国太平洋時間)までは早期割引料金で登録可能

テクニカルカンファレンスの参加登録料金は参加形態によらない。リアル参加とバーチャル参加は同じ料金であり、リアル参加登録者はオンデマンドの動画配信を視聴できる。2025年11月10日までは早期割引料金が適用される。IEEE正会員の登録料金は早期割引期間が635ドル、通常(11月11日以降)が745ドルとなる。

ショートコース(別料金)は2つのコースから1つを選択する。登録料金はIEEE正会員が475ドルであり、早期割引はない。チュートリアル(別料金)は参加件数によって料金が異なる。6件のチュートリアルすべてを登録したときの料金はIEEE正会員が420ドルとなる。こちらも早期割引はない。

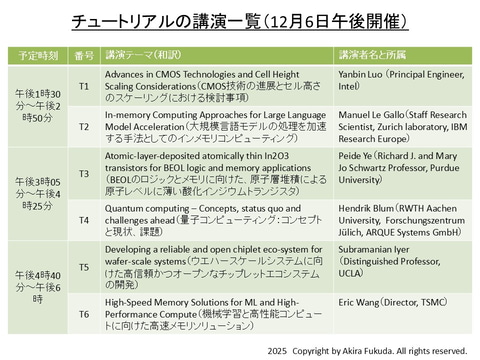

12月6日午後: CMOS微細化や量子計算など6件の技術講座を予定

それでは、IEDM 2025の概要を日程順にご紹介していこう。始めは12月6日(土曜日)である。同日は午後に、チュートリアル(1件ずつのテーマ別技術講座、時間は80分)を予定する。3つの時間枠(タイムスロット)があり、1つのタイムスロットで2件の講座を同時並行で実施する。

チュートリアルのテーマは、最初のスロット(午後1時30分開始)が「CMOSと論理セル高さの微細化」と「大規模言語モデル処理を高速化するインメモリコンピューティング」、2番目のスロット(午後3時05分開始)が「多層配線工程で作る酸化インジウムトランジスタ」と「量子コンピューティング」、最後のスロット(午後4時40分開始)が「ウェハスケールシステムに向けたチップレット」と「機械学習と高性能コンピューティングに向けた高速メモリ」となっている。

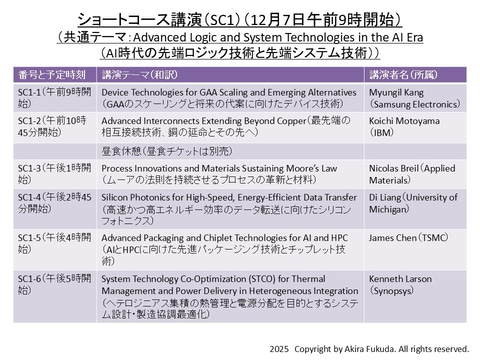

12月7日: 1日間の技術講座をロジック分野とメモリ分野で用意

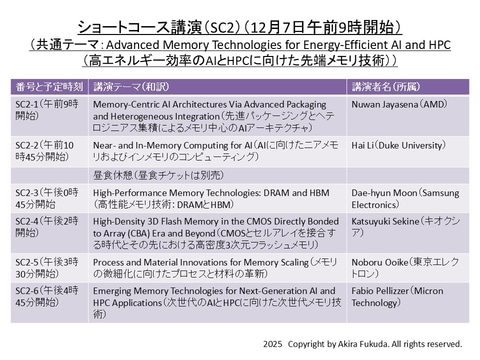

翌12月7日(日曜日)は、2つのショートコース(テーマ別に複数の講演で構成した1日間の技術講座)を予定する。最近のショートコースでは、1つをロジック分野、もう1つをメモリ分野にすることが多い。今年は1つ目(記号はSC1)の共通テーマが「Advanced Logic and System Technologies in the AI Era(AI時代の先端ロジック技術と先端システム技術)」、2つ目(記号はSC2)の共通テーマが「Advanced Memory Technologies for Energy-Efficient AI and HPC(高エネルギー効率のAIとHPCに向けた先端メモリ技術)」である。いずれもAI(人工知能)と絡めたテーマとなった。

ロジック分野の講演は6件。「トランジスタのスケーリング(微細化)」「多層金属配線」「プロセスと材料」「シリコンフォトニクス」「先進パッケージング」「熱と電源のシステム設計・製造最適化」に関する講演を用意した。

メモリ分野の講演も6件ある。「メモリ中心のAIアーキテクチャ」「AI向けの計算機能付きメモリ」「DRAMとHBM」「NANDフラッシュメモリ」「メモリ向けプロセスと材料」「次世代メモリ」に関する講演を予定する。

12月8日午前: エッジAI、メインフレーム、特化型半導体を基調講演で展望

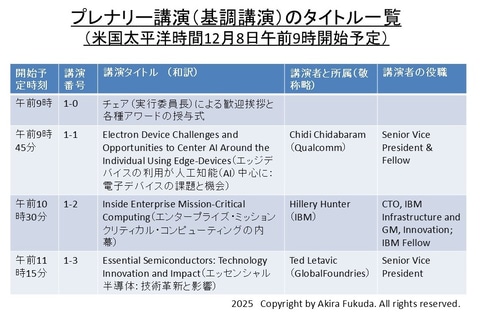

続く12月8日(月曜日)から10日(水曜日)までは、テクニカルカンファレンス(技術講演会)を予定する。8日午前は恒例の開会挨拶および表彰式、それからプレナリー講演(基調講演)セッションと続く。プレナリー講演セッションでは3件の招待講演を予定する。

始めはQualcommのChidi Chidabaram氏が、「Electron Device Challenges and Opportunities to Center AI Around the Individual Using Edge-Devices(人工知能(AI)を中心としたエッジデバイスの利用がもたらす電子デバイスの課題と機会)」と題して講演する。クラウドAIシステムに比べるとエッジAIシステムは制約が厳しい。たとえば消費電力の低さ、ネット接続の堅牢さ、コストの低さ、一定規模の生産数量だとする。最適なエッジシステムの実現には、先進パッケージング技術やメモリ帯域幅拡張などの最近の技術成果を取り込む必要があるとする。

次にIBMのHillery Hunter氏が「Inside Enterprise Mission-Critical Computing(エンタープライズ・ミッションクリティカル・コンピューティングの内幕)」と題してメインフレームやエンタープライズサーバーなどの内部構造を解説する。システムレベルで99.999999%の稼働率を実現する、シリコンダイ技術とパッケージング技術を述べる。

最後にGlobalFoundriesのTed Letavic氏が「Essential Semiconductors: Technology Innovation and Impact(エッセンシャル半導体: 技術革新と影響)」と題してエッセンシャル半導体(トランジスタ密度の向上ではなく、性能あるいは電力効率、信頼性に特化した半導体)の技術革新を展望する。今後10年を左右する要素技術、すなわちRF(無線周波数)、超低消費電力、SOI(Silicon On Insulator)、埋め込み不揮発性メモリ、相互接続、シリコンフォトニクス、新材料が古典的なコンピューティングと量子コンピューティングの双方に与える影響を議論する。

12月8日午後: 9個の一般講演セッションを同時並列に進行

12月8日(月曜日)の午後からは、一般講演セッションが始まる。時間枠(タイムスロット)は同日午後のほか、9日(火曜日)午前、9日午後、10日(水曜日)午前、10日午後の合計5つ。5つの時間枠で41個のテーマ別講演セッションを実施する。当然ながら、数多く(平均すると約8個)の講演セッションを同時並行で進めることになる。

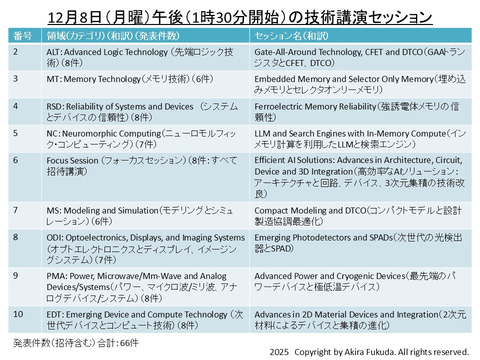

最初の時間枠(タイムスロット)である8日午後は、「セッション2」から「セッション10」までの9個の講演セッションが並行に進む。先端ロジック、埋め込みメモリ、強誘電体メモリの信頼性、インメモリ計算による大規模言語モデル処理、光検出器などのセッションを予定する。

同日夕方(午後6時30分)には、レセプション(歓迎会)が催される。近年と同じであれば、立食形式になると思われる。

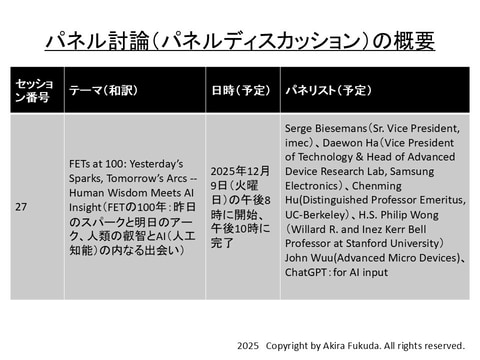

12月9日: パネル討論会に生成AIがパネリストとして登場

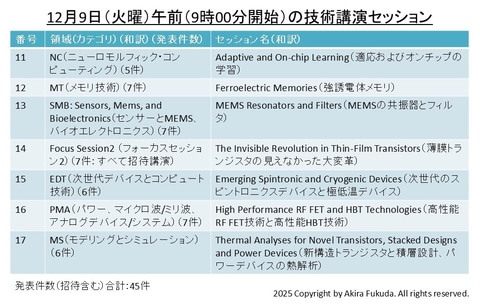

翌12月9日(火曜日)の午前は、「セッション11」から「セッション17」までの7個の講演セッションが同時進行する。オンチップの機械学習、強誘電体メモリ、スピントロニクス、高周波FETなどのセッションを予定する。

その後は昼食会(ランチ)が用意される(ランチの参加登録は別料金)。昼食会では2件の講演を予定する。1件の講演者はHiroshi Iwai氏(台湾国立交通大学および東京科学大学)、講演タイトルは「A Century of Miracles: From the FET’s Inception to the Horizons Ahead(奇跡の世紀: 電界効果トランジスタ(FET)の誕生と未来への展望)」である。もう1件の講演者はBob Johnson氏(ガートナー)、講演タイトルは「Semiconductor Market Outlook: Speedbumps on the Road to a Terrabuck?(半導体市場の将来動向: テラバックに至る道への障害は?)」である。

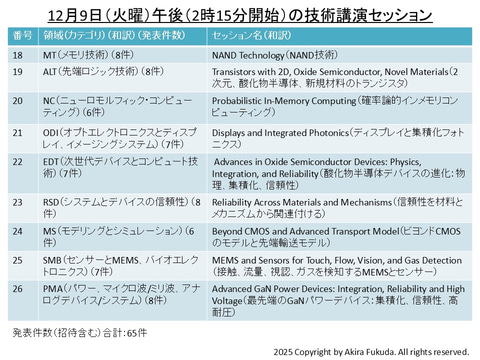

同日午後は、「セッション18」から「セッション26」までの9個のセッションが並列に進む。NAND技術、2次元材料トランジスタ、確率論的インメモリコンピューティング、集積化フォトニクス、酸化物半導体デバイス、MEMSセンサー、GaNパワーデバイスなどのセッションがある。

同日夜(午後8時開始予定)には、パネル討論(パネルディスカッション)を予定する。テーマは「FETs at 100: Yesterday’s Sparks, Tomorrow’s Arcs -- Human Wisdom Meets AI Insight(FETの100年: 昨日のスパークと明日のアーク、人類の叡智とAI(人工知能)の内なる出会い」。パネリストはimec、Samsung Electronics、UC Berkeley、Stanford University、AMDの研究者あるいは技術者である。興味深いのは、生成AI技術の代表である「ChatGPT」がパネリストに名前を連ねていることだろう。ChatGPTへの入力と回答が、討論の一部を構成するものとみられる。

12月10日: 最終日は昼食時間を削るほどの厳しいスケジュール

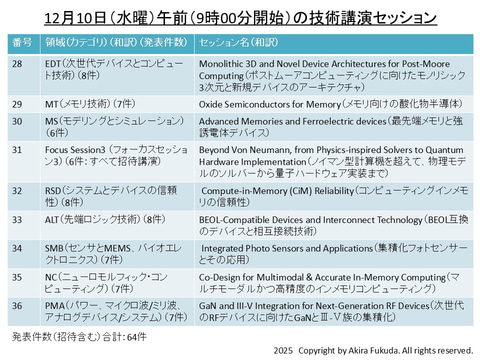

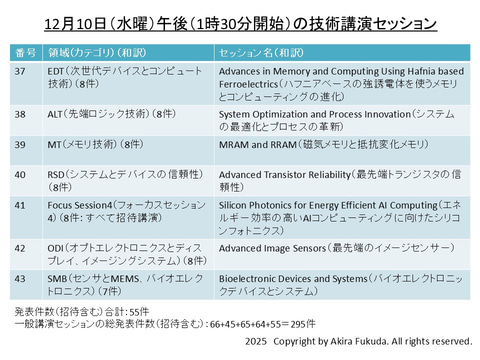

技術講演会(テクニカルカンファレンス)の最終日である12月10日は午前に9個、午後に7個の講演セッションを進める。しかも午前は件数の多いセッションだと完了予定が12時50分とかなり遅く、午後のセッションは一律に午後1時30分から始まる。午前のセッションが予定時刻通りに完了しても、午後までの休憩時間が40分しかない。厳しいスケジュールが最後まで続く。

10日午前のセッションテーマはポストムーアコンピューティング、酸化物半導体メモリ、多層配線プロセス互換のデバイス、集積化フォトセンサー、次世代高周波デバイス、などである。そして同日午後のセッションテーマは不揮発性メモリ(磁気メモリと抵抗変化メモリ)、最先端トランジスタの信頼性、イメージセンサー、バイオエレクトロニクス、などとなる。

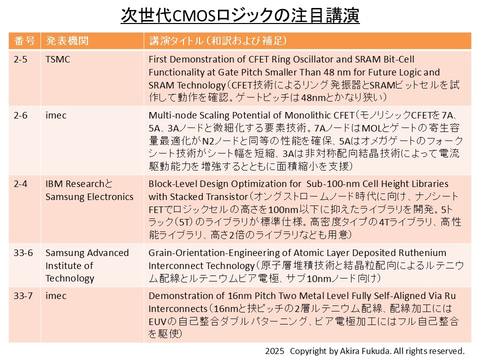

相補型FET技術によるリング発振器とSRAMセルをTSMCが試作

ここからは、注目すべき発表(研究開発成果)を紹介しよう。始めはCMOSロジックに関連する研究開発成果である。TSMCは、CFET(相補型FET)技術によるリング発振器とSRAMビットセルを試作して動作を確認した(講演番号2-5)。ゲートピッチは48nmとかなり狭い。TSMCは前年のIEDM(IEDM 2024)でCFET技術(ゲートピッチは同じ48nm)によるインバータを試作しており、さらに複雑な回路の研究成果を今回は披露することになる。

imecは、モノリシックCFETを7A(Aはオングストローム(0.1nm)の意味)、5A、3Aノードと微細化する要素技術を発表する(同2-6)。7AノードはMOL(Middle Of the Line)とゲートの寄生容量最適化がN2(2nm)ノードと同等の性能を確保、5Aノードはオメガゲートのフォークシート技術がシート幅を短縮、3Aノードは非対称配向結晶技術によって電流駆動能力を増強するとともに面積縮小を支援する。

IBM ResearchとSamsung Electronicsはオングストロームノード時代に向け、ナノシートFETでロジックセルの高さを100nm以下に抑えたライブラリを共同で開発した(同2-4)。5トラック(5T)のライブラリが標準仕様である。高密度タイプの4Tライブラリ、高性能ライブラリ、高さ2倍のライブラリなども用意する。

Samsung Advanced Institute of Technologyは、原子層堆積技術と結晶粒配向によるルテニウム配線とルテニウムのビア電極を発表する(同33-6)。サブ10nmノード向けである。imecは、16nmと狭ピッチの2層ルテニウム配線技術を開発した(同33-7)。配線加工にはEUV露光の自己整合ダブルパターニング、ビア電極加工にはフル自己整合を駆使している。

「メモリ」「センサー」「パワーデバイス」「新規デバイス」などの注目講演は、機会を改めて本コラムでご紹介する。しばらくお待ちいただけるとありがたい。

![【Amazon.co.jp限定】 伊藤園 磨かれて、澄みきった日本の水 2L 8本 ラベルレス [ ケース ] [ 水 ] [ 軟水 ] [ ペットボトル ] [ 箱買い ] [ ストック ] [ 水分補給 ] 製品画像:3位](https://m.media-amazon.com/images/I/41n0o65dSkL._SL160_.jpg)

![[新品]サカモトデイズ SAKAMOTO DAYS (1-27巻 最新刊) 全巻セット 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0034/m8880487562_01.jpg?_ex=128x128)

![Suicaのペンギンファンブック [ さかざきちはる ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8593/9784865938593_1_2.jpg?_ex=128x128)

![キングダム 79 (ヤングジャンプコミックス) [ 原 泰久 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1967/9784088941967_1_22.jpg?_ex=128x128)

![オレンジページ 2026年 8/2号増刊 [雑誌] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0869/4912210260869.jpg?_ex=128x128)

![ヤングジャンプ 2026 No.25 【電子書籍】[ ヤングジャンプ編集部 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7354/2000020407354.jpg?_ex=128x128)

![片田舎のおっさん、剣聖になる〜ただの田舎の剣術師範だったのに、大成した弟子たちが俺を放ってくれない件〜 9 【電子書籍】[ 佐賀崎しげる ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/3026/2000020673026.jpg?_ex=128x128)

![引きこもり令嬢は皇妃になんてなりたくない!〜強面皇帝の溺愛が駄々漏れで困ります〜5巻 【電子書籍】[ 直江亜季子 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2291/2000020632291.jpg?_ex=128x128)