福田昭のセミコン業界最前線

8層の3次元DRAMセルや2,000万fpsの超高速CISなど、IEDMで日本の研究成果を誇示

2025年12月15日 06:03

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting、日本語の通称は「国際電子デバイス会議」)」が、米国カリフォルニア州サンフランシスコで始まった。採択論文(一般講演)の件数は295件である。2025年12月8日午後から10日夕方までの2日半、時間枠としては5つで、295件の一般講演に10件を超えるとみられる招待講演を加えた、300件を超える講演が実施される。

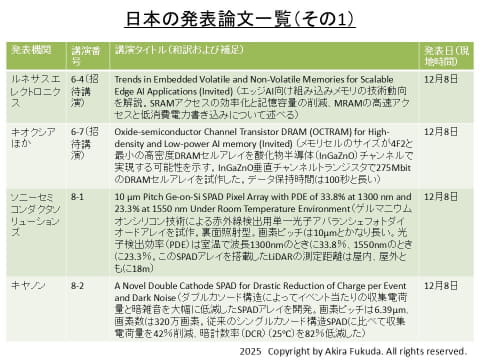

本コラムの前回で述べたように、アジア地域の採択論文は177件である。プログラムを筆者が調査した結果では、日本(第1著者ベース)からの一般講演は13件、招待講演は6件あった。以下は、日本の講演概要をセッション番号および講演番号の順番でご報告する。

酸化物半導体DRAMとGe on SiのSPADアレイ

始めはセッション6(フォーカスセッション: 高エネルギー効率のAIソリューション)で、2件の招待講演が実施される。

ルネサス エレクトロニクスは、エッジAI向け組み込みメモリの技術動向を解説する(講演番号6-4)。SRAMアクセスの効率化と記憶容量の削減、MRAM(磁気抵抗メモリ)の高速アクセスと低消費電力の書き込みについて述べる。同じセッションではキオクシアなどの研究グループが、メモリセルのサイズが4F^2と最小の高密度DRAMセルアレイを酸化物半導体(InGaZnO)チャンネルで実現する可能性を示す(同6-7)。InGaZnO垂直チャンネルトランジスタで275MbitのDRAMセルアレイを試作した。データ保持時間は100秒と長い。

それからセッション8(光検出器)で、ソニーグループとキヤノンがそれぞれ、単一光子アバランシェフォトダイオード(SPAD)のアレイを開発した成果を発表する。ソニーグループは、ゲルマニウムオンシリコン(Ge on Si)技術による赤外線検出用単一光子アバランシェフォトダイオードアレイを試作した(講演番号8-1)。裏面照射型である。画素ピッチは10μmとかなり長い。光子検出効率(PDE)は室温で波長1,300nmの時に33.8%、1,550nmのときに23.3%。このSPADアレイを搭載したLiDARの測定距離は屋内、屋外ともに18mと長い。

キヤノンは、ダブルカソード構造によってイベント当たりの収集電荷量と暗雑音を大幅に低減したSPADアレイを開発した(講演番号8-2)。画素ピッチは6.39μm、画素数は320万画素。従来のシングルカソード構造SPADに比べて収集電荷量を42%削減するとともに、暗計数率(DCR)(25℃)を82%低減した。

1.2kV、500Aの高耐圧低オン抵抗SiC FinFET

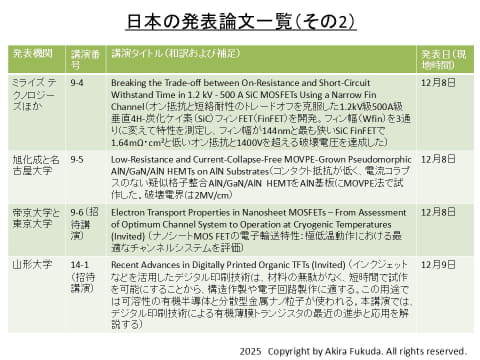

続くセッション9の最先端パワーデバイスでは、日本から3件の発表がある。最初の2件は一般講演で、ミライズテクノロジーズほかの共同研究グループと、旭化成と名古屋大学の共同研究チームがそれぞれ、研究成果を発表する。

ミライズテクノロジーズほかのグループは、オン抵抗と短絡耐性のトレードオフを克服した1.2kV級500A級垂直4H炭化ケイ素(SiC)FinFETを開発した(講演番号9-4)。フィン幅(Wfin)を3通りに変えて特性を測定し、フィン幅が144nmと最も狭いSiC FinFETで1.64mΩ・平方cmと低いオン抵抗と1,400Vを超える破壊電圧を達成した。

旭化成と名古屋大学の共同チームは、コンタクト抵抗が低く、電流コラプスのない疑似格子整合AlN/GaN/AlN HEMTをAlN基板にMOVPE法で試作した(同9-5)。破壊電界は2MV/cm。

最後の1件は招待講演となる。帝京大学と東京大学の共同研究チームが、ナノシートMOS FETの電子輸送特性について述べる(講演番号9-6)。極低温動作における最適なチャネルシステムを評価した。

それからセッション14(フォーカスセッション: 薄膜トランジスタ)で、山形大学がデジタル印刷技術による有機薄膜トランジスタの最近の進歩と応用を解説する(講演番号14-1、招待講演)。インクジェットなどを活用したデジタル印刷技術は、材料の無駄がなく、短時間で試作が可能なことから、電子回路製作や構造製作などに適するとされる。

酸化物半導体の次世代ロジックと次世代メモリ

セッション21の集積化フォトニクスでは、東京大学などの共同研究グループが、III–V/Si ハイブリッドMOS光位相シフタによる超低消費高速シリコンフォトニクススイッチを試作した(講演番号21-5)。スイッチの待機時消費電力は数百fW(フェムトワット)と低い。スイッチング時間はナノ秒オーダー。光変調効率(半波長電圧)は0.13Vcmと高い。

続くセッション22の酸化物半導体デバイスの進化では、東京大学などの共同研究グループが多結晶InGaOxナノシート酸化物半導体FETの統計的なばらつきをゲート長60nmのFETアレイを試作して分析した(講演番号22-7)。オン電流と相互コンダクタンスはアモルファスInGaOxナノシートFETよりも高いが、しきい電圧とサブスレッショルド特性はばらつきが大きくなりやすい。

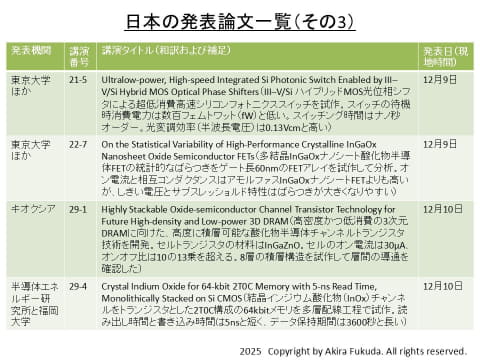

セッション29のメモリ向けの酸化物半導体では2件の研究成果が日本から発表される。キオクシアは、高密度かつ低消費電力の3次元DRAMに向けた、高度に積層可能な酸化物半導体チャンネルトランジスタ技術を開発した(講演番号29-1)。セルトランジスタの材料はInGaZnO。セルのオン電流は30μA、オンオフ比は10の13乗を超える。8層の積層構造を試作して層間の導通を確認した。

半導体エネルギー研究所などの共同研究グループは、結晶インジウム酸化物(InOx)チャンネルをトランジスタとした2T0C構成の64kbitメモリを多層配線工程で試作した(講演番号29-4)。読み出し時間と書き込み時間は5nsと短く、データ保持期間は3,600秒と長い。

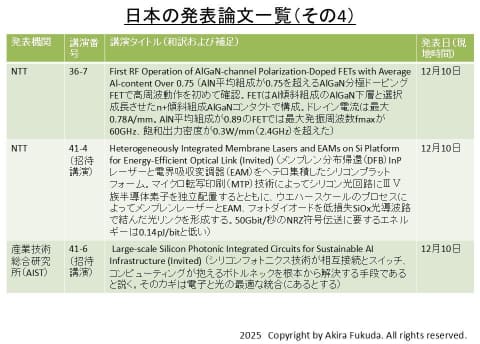

分極ドーピングのワイドギャップ化合物FETで高周波動作を確認

セッション36の化合物RFデバイスでは、AlN平均組成が0.75を超えるAlGaN分極ドーピングFETによる高周波動作をNTTが初めて確認した(講演番号36-7)。FETはAl傾斜組成のAlGaN下層と、選択成長させたn+傾斜組成AlGaNコンタクトで構成している。ドレイン電流は最大0.78A/mm。AlN平均組成が0.89のFETでは最大発振周波数fmaxが60GHz、飽和出力密度が0.3W/mm(2.4GHz)を超えた。

セッション41のフォーカスセッション: シリコンフォトニクスでは、2件の招待講演を予定する。NTTは、メンブレン分布帰還(DFB)InPレーザーと電界吸収型光変調器(EAM)をヘテロ集積したシリコンプラットフォームを報告する(講演番号41-4)。マイクロ転写印刷(MTP)技術によってシリコン光回路にIIIV族半導体素子を独立配置するとともに、ウェハスケールのプロセスによってメンブレンレーザーとEAM、フォトダイオードを低損失SiOx光導波路で結んだ光リンクを形成した。50GbpsのNRZ符号伝送に要するエネルギーは0.14pJ/bitと低い。

産業技術総合研究所(AIST)は、シリコンフォトニクス技術が相互接続とスイッチ、コンピューティングが抱えるボトルネックを根本から解決する手段であると説く(講演番号41-6)。そのカギは電子と光の最適な統合にあるとする。

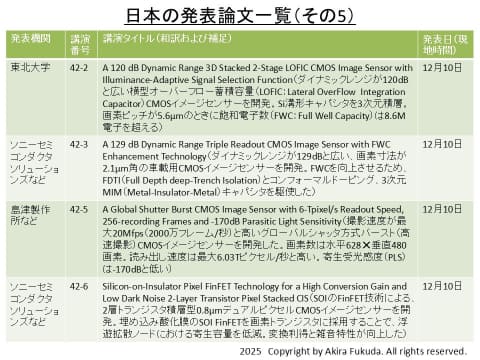

撮影速度が2,000万fpsの超高速イメージセンサー

セッション42(最先端のイメージセンサー)では、4件と多くの研究成果が日本から続出する。東北大学は、ダイナミックレンジが120dBと広い横型オーバーフロー蓄積容量(LOFIC: Lateral OverFlow Integration Capacitor)CMOSイメージセンサー(CIS: CMOS Image Sensor)を開発した(講演番号42-2)。Si溝形キャパシタを3次元積層している。画素ピッチが5.6μmのときに飽和電子数(FWC: Full Well Capacity)は8.6M電子を超える。

ソニーセミコンダクタソリューションズなどの研究グループは、ダイナミックレンジが129dBと広い、画素寸法が2.1μm角の車載用CMOSイメージセンサー(CIS)を開発した(講演番号42-3)。FWCを向上させるため、FDTI(Full Depth deep-Trench Isolation)とコンフォーマルドーピング、3次元MIM(Metal-Insulator-Metal)キャパシタを駆使した。

島津製作所などの共同研究グループは、撮影速度が最大20Mfps(2,000万fps)と高いグローバルシャッタ方式バースト(高速撮影)CMOSイメージセンサー(CIS)を開発した(講演番号42-5)。画素数は628×480ドット(水平×垂直)。読み出し速度は最大6.03Tピクセル/sと高い。寄生受光感度(PLS)は-170dBと低い。

ソニーセミコンダクタソリューションズなどの研究グループはSOI(Silicon On Insulator)のFinFET技術による、2層トランジスタ積層型0.8μmデュアルピクセルCMOSイメージセンサー(CIS)を開発した(講演番号42-6)。埋め込み酸化膜のSOI FinFETを画素トランジスタに採用することで、浮遊拡散ノードにおける寄生容量を減らした。この結果、変換利得と雑音特性が向上した。

発表件数はそれほど多くないものの、酸化物半導体やワイドギャップ化合物デバイス、CMOSイメージセンサーなどでは日本の研究成果が目立つ。さらなる発展を期待したい。

![HP Elite Mini 800 G9(Win11x64) 中古 Core i5-2.0GHz(12500T)/メモリ8GB/SSD256GB [C:並品] 2022年頃購入 製品画像:8位](https://thumbnail.image.rakuten.co.jp/@0_mall/usedpc/cabinet/url1/5725918c.jpg?_ex=128x128)

![DELL デル スリム ECS1250 [モニター無し / Win11 Home / intel Core i3 / メモリ8GB / SSD512GB / 2026年春モデル] ブラック SD20-GH 製品画像:5位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001729/4573661276412_1.jpg?_ex=128x128)

![[★ケーブルセット価格] EIZO FlexScan EV2451 23.8インチ ワイド 液晶モニター ブラック フルHD フレームレス IPSパネル フリッカーフリー 非光沢 ノングレア HDMI DisplayPort DVI VGA 縦置き可 フレームレス スイーベル機能 高さ調整 23.8型 PCモニター 中古モニター 中古 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-shinjyo/cabinet/monitor/pc-ev2451.jpg?_ex=128x128)

![液晶ディスプレイ アイ・オー・データ LCD-A241DB [液晶ディスプレイ 23.8型/ブラック/5Y/3辺フレームレス] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage28/1264173.jpg?_ex=128x128)

![LENOVO|レノボジャパン PCモニター L24-4C クラウドグレー 67DDKAC6JP [23.8型 /フルHD(1920×1080) /ワイド /144Hz] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/16440/00000014962075_a01.jpg?_ex=128x128)

![棺桶まで歩こう (幻冬舎新書) [ 萬田緑平 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7937/9784344987937_1_5.jpg?_ex=128x128)

![[新品]金色のガッシュ!! 完全版(1-16巻 全巻) + 20周年記念オリジナル収納BOX付セット 全巻セット 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0052/m0019400091-spbox_01.jpg?_ex=128x128)

![角川まんが学習シリーズ 日本の歴史 5大特典つき全16巻+別巻5冊セット [ 山本 博文 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3680/9784041153680_1_17.jpg?_ex=128x128)

![第一生命最大たるより、「最良」たれ 「人」と「経営品質」で挑む変革の物語 [ 高橋利雄 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0520/9784820120520.jpg?_ex=128x128)

![FINEBOYS+plus Share vol.4 [ 日之出出版 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5154/9784838795154.gif?_ex=128x128)

![【楽天ブックス限定特典】KEITA MACHIDA 15th Anniversary Photobook 「sign」(限定トレカ) [ 町田啓太 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1991/2100014771991_1_3.jpg?_ex=128x128)

![おいしい!イラストレッスン クレパスで描きました [ momo ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1558/9784522441558_1_2.jpg?_ex=128x128)

![カイシャがなくなる日 組織と働き方の進化論 (BOW BOOKS 036) [ 名和 高司 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6418/9784502556418_1_6.jpg?_ex=128x128)

![角川まんが学習シリーズ 世界の歴史 3大特典つき全20巻+別巻2冊セット [ 羽田 正 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3710/9784041153710_1_9.jpg?_ex=128x128)