福田昭のセミコン業界最前線

HBMの記憶容量を10倍超に拡大する「フラッシュHBM」

2025年10月15日 09:03

超広帯域DRAMモジュール技術「HBM(High Bandwidth Memory)」の派生品がテック系メディアで最近、話題となっている。「モバイルHBM」と「フラッシュHBM」である。「モバイルHBM」の正体と技術については過去の本コラムで2回に渡って報告した。

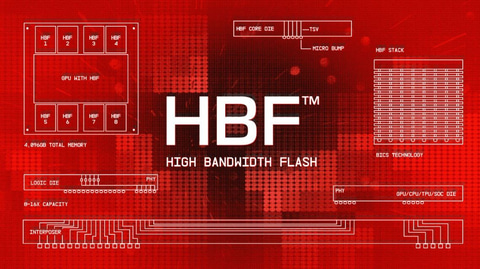

今回は「フラッシュHBM」こと「高バンド幅フラッシュ(HBF: High Bandwidth Flash)」の概要を解説したい。「フラッシュHBM」こと「HBF」の考え方は非常に単純だ。まずは従来技術である「HBM(High Bandwidth Memory)」から始めよう。

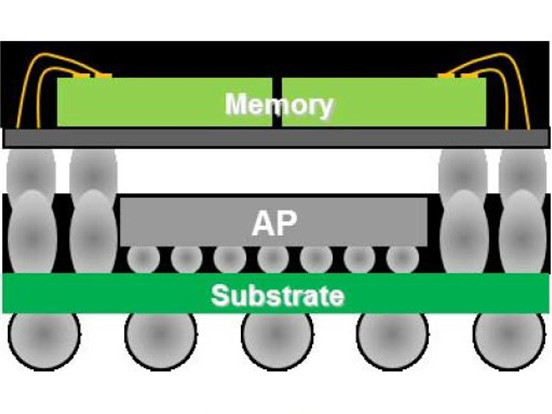

HBMは、HBM規格に準拠した専用DRAMダイを「シリコン貫通電極(TSV: Through Silicon Via)」技術によって3次元積層した記憶部(DRAMダイは「コアダイ」と呼ばれる)と、最下段の「ベースダイ」(ロジックダイ)によって構成される。

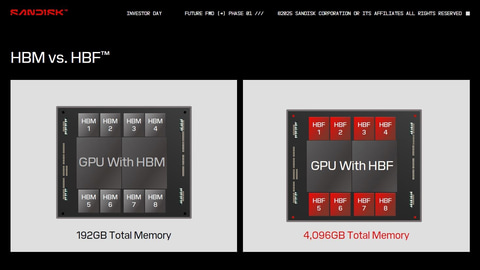

DRAMダイ(コアダイ)の枚数はHBMの世代によって異なり、たとえば第5世代の「HBM3E」では12枚あるいは16枚のコアダイを積層する。コアダイの記憶容量は16Gbitあるいは24Gbitである。コアダイの記憶容量を16Gbit(2GB)、積層枚数を12枚と仮定すると、HBMモジュール1個の記憶容量は24GB(192Gbit)となる。

そしてGPUあるいはSoCといった最先端大規模ロジックと同じインターポーザに、8個のHBMモジュールを搭載する。HBM全体の記憶容量は192GBとなる。HBMは、GPUから見たメモリ階層では主記憶に相当する。

またDRAMダイの記憶容量を24Gbit(3GB)、積層枚数を16枚に拡大する。インターポーザに載せるHBMジュールの数を8個と仮定すると、HBM全体の記憶容量は48GBモジュール✕8個で384GBとなる。

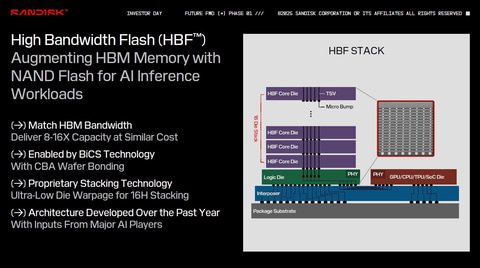

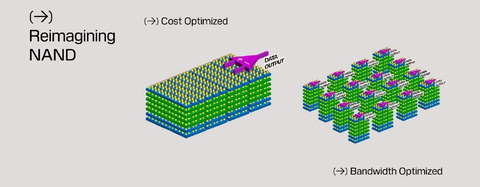

ここでコアダイをDRAMではなく、NANDフラッシュメモリに変更しよう。NANDフラッシュダイ(コアダイ)の記憶容量を256Gbitとやや控えめにし、コアダイの積層枚数を16枚と仮定すると、モジュール(HBFモジュール)当たりの記憶容量は512GBとなる。512/48=10.7、512/24=21.3なので、モジュール当たりの記憶容量はDRAMのコアダイと比べて10倍~20倍に拡大する。これが「HBF(High Bandwidth Flash)」である。8個のHBFをGPUと同じ中間基板に載せれば、4,096GBと大きな主記憶を得られることになる。

HBFを考案したのは、NANDフラッシュメモリおよびフラッシュストレージのサプライヤであるSandiskだ。入出力帯域はDRAMコアダイのHBMとほぼ同じであり、HBMに近いコストで記憶容量を8倍~16倍に拡大し、消費電力を大幅に減らせるとする。512GBモジュールの入出力データ速度は1.6TB/sと高く、DRAMコアダイの「HBM4」に近い。また外形寸法(平面サイズと高さ)は、「HBM4」モジュールとほぼ同じだとする。

HBM用DRAMの高コスト化がAIサーバーの性能向上を制限

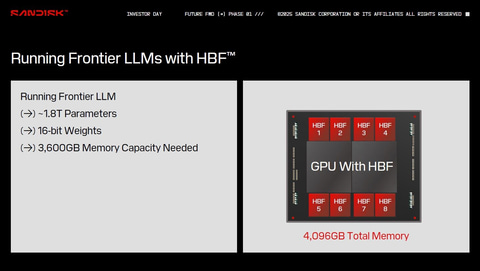

Sandiskは、人工知能(AI)関連の大手企業複数社から情報を収集してHBFのアーキテクチャを考案したとする。大規模言語モデル(LLM: Large Language Model)に代表される大規模なマシンラーニングモデルは、パラメータの数が極めて多い。たとえば16bitの重みで1.8兆(1.8T)のパラメータを格納するためには、3,600GBのメモリが必要となると同社は述べる。

HBMモジュールは192GB~384GBが現在の最大容量であり、3,600GBのデータを格納することは難しい。原理的には可能だが、DRAMのコストが非実用的な水準に跳ね上がってしまう。

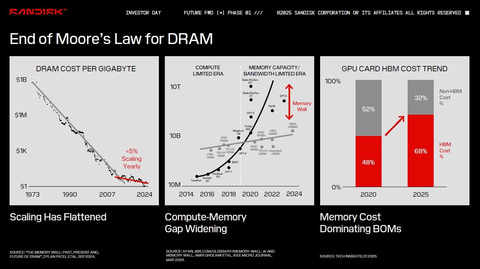

そして近年、DRAMの記憶容量当たりコストは以前とは異なり、あまり下がらなくなっている。年率では5%くらいの値下がりしか期待できない。にもかかわらず、2020年代に入ってから大規模なマシンラーニングモデルが要求するメモリ容量は急速に増加している。 GPUモジュール製品の主記憶容量はHBMの容量拡大によって増加しつつあるものの、要求する記憶容量とのギャップは広がる一方なのだ。

またGPUモジュールの製品コストに占めるHBMコストは2020年に半分弱(48%)だったのが、2025年には3分の2強(68%)へと上昇した。DRAMベースの広帯域メモリであるHBMは、低コストを重視するエッジのAIサーバーにとって性能向上、すなわち主記憶容量(HBM容量)の拡大を難しくしつつある。

NANDフラッシュ広帯域モジュールの長所と短所

そこでDRAMに比べ、記憶容量当たりのコストが低いNANDフラッシュメモリを広帯域メモリモジュール(HBF)とすることで、メモリコストの上昇を抑えながら、主記憶容量を大幅に拡大する。ただしNANDフラッシュメモリは、読み出しと書き込みの性能が非対称だという問題点を抱える。読み出しはDRAM並みに高速であり、原理的には寿命がない(無限に読み出し可能)。書き込みはDRAMに比べると低速で、書き換えの回数に制限がある(多くても1万回程度)。

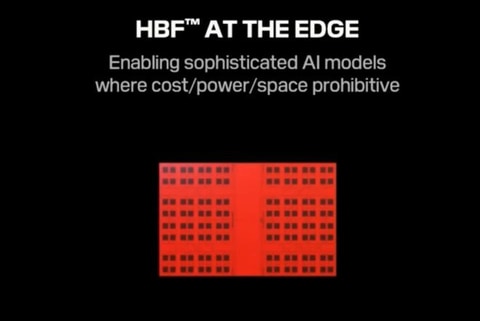

このため、AI用途でも学習用サーバーでは、モデルの調整に伴うパラメータの書き換えが頻繁に発生するので、NANDフラッシュメモリは適さない。パラメータの書き換えがあまり発生しない推論主体のサーバーに適する。Sandiskは、コストと消費電力、設置スペースの低減を重視するエッジの推論サーバーに向くと主張する。

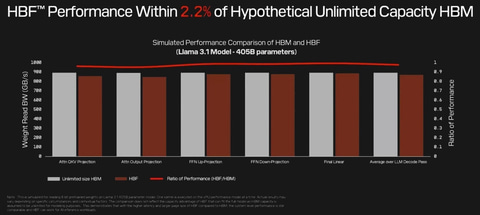

無限大容量のHBMと比較したHBFの推論性能はほぼ同等

DRAMコアダイのHBMをNANDフラッシュメモリコアダイのHBFに置き換えた場合、推論性能はどの程度の低下に収まるだろうか。SandiskがLLM「Llama 3.1(4,050億パラメータ)」を例に推論処理のいくつかのステップで比較した結果、HBFはHBM(記憶容量は無限に大きいと仮定)に比べて2.2%未満の性能低下に留まったとする(GPUは同じ)。

HBFとGPUの組み合わせによる推論性能は、HBMにかなり近い。実際にはHBMの記憶容量が無限大ということはありえないので、性能差はさらに縮まると予想される。

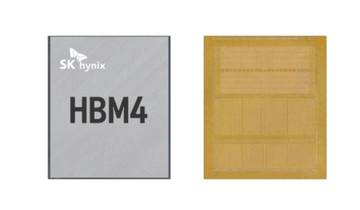

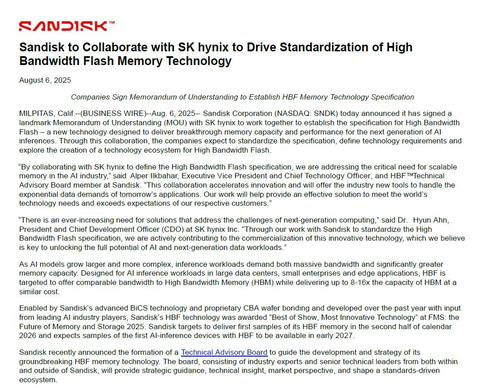

HBM最大手のSK hynixが開発に協力

HBFの開発と仕様策定にあたっては、SK hynixがSandiskに協力する。SK hynixはDRAM大手であるとともにNANDフラッシュメモリ大手でもあり、HBMの最大手サプライヤでもある。HBFにはTSV技術が欠かせない。SandiskはTSV技術の量産実績を持たないので、同じくTSV技術を採用するHBMの量産実績があり、なおかつNANDフラッシュメモリに明るいSK hynixは最適なパートナーだとも言える。

HBFモジュールのサンプルは、2026年下半期に出荷する予定である。そして2027年始めには、HBFモジュールを搭載したAI推論サーバーが登場する見込みだとする。

![【Amazon.co.jp限定】 伊藤園 磨かれて、澄みきった日本の水 2L 8本 ラベルレス [ ケース ] [ 水 ] [ 軟水 ] [ ペットボトル ] [ 箱買い ] [ ストック ] [ 水分補給 ] 製品画像:3位](https://m.media-amazon.com/images/I/41n0o65dSkL._SL160_.jpg)

ThinkPad L13 GEN2 20VJS33K00 製品画像:14位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-bomber-shop/cabinet/mastertool87/251051002293800.jpg?_ex=128x128)

![内視鏡下鼻副鼻腔・頭蓋底手術 [手術動画・3DCT画像データDVD-ROM付] 第2版 CT読影と基本手技 [ 中川 隆之 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8393/9784260038393.jpg?_ex=128x128)

![盾の勇者の成り上がり 30 【電子書籍】[ 藍屋球 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7729/2000020477729.jpg?_ex=128x128)

![ゴールデンカムイ 全巻セット(1-31巻) (ヤングジャンプコミックス) [ 野田サトル ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7713/2100013057713.jpg?_ex=128x128)

![チャイロイコグマの10th Anniversary BOOK (生活シリーズ) [ サンエックス ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5606/9784391645606.jpg?_ex=128x128)

![テレビマガジン特別編集 仮面ライダー 昭和46年~48年 講談社所蔵写真集 究極 [ 講談社 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1309/9784065401309_1_3.jpg?_ex=128x128)

![頭頸部の臨床画像診断学(改訂第4版) [ 尾尻博也 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6610/9784524226610.jpg?_ex=128x128)

![ヤングジャンプ 2026 No.25 【電子書籍】[ ヤングジャンプ編集部 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7354/2000020407354.jpg?_ex=128x128)