笠原一輝のユビキタス情報局

チップレットになった「第4世代Xeon SP」、性能向上の鍵はAMXと4つのアクセラレータ

2023年1月11日 03:00

Intelは1月10日(現地時間、日本時間1月11日)に報道発表を行ない、同社が「Sapphire Rapids」(サファイアラピッズ)の開発コードネームで開発してきたデータセンター向けCPUを、「第4世代Xeonスケーラブル・プロセッサー」(英語名:4th Gen Xeon Scalable Processors、以下第4世代Xeon SP)として発表したことを明らかにした。

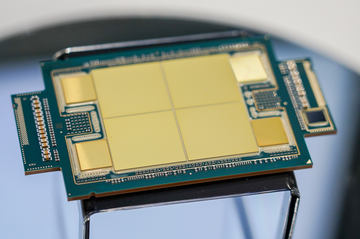

新しい第4世代Xeon SPは、4つのCPUダイを1つのパッケージに統合しているというチップレット技術を採用しており、Intelが独自開発したEMIBを利用して4つダイが1つの巨大CPUとして動作する仕組みになっている。これにより従来製品では最大40コアだったCPUコア数は、最大60コアへと強化されている。

また、アーキテクチャ面での大きな強化点としては、QAT(QuickAssist Technology)、DLB(Dynamic Load Blancer)、DSA(Data Streaming Accelerator)、IAA(In-Memory Analytics Accelerator)といった4つのハードウェアアクセラレータがCPUに統合されており、それらを利用することでCPUの処理をオフロードして電力効率を大きく改善している。

そうした第4世代Xeon SPのハードウェアに関して、Intelへの取材などを通じて分かったことを踏まえながら解説していきたい。

チップレットのXCC、モノリシックMCCという2つの種類のパッケージが用意されている第4世代Xeon SP

今回の第4世代Xeon SPは、CPUの内部構造(マイクロアーキテクチャ)、パッケージ、そしてプラットホームに至るまで、ほとんど総取り替えと言って良いほどの大きな改良になっている。

その1番の目玉はCPUのパッケージング技術として、チップレットを採用したことだ。チップレットとは複数のダイをパッケージ上で混載する技術で、第4世代Xeon SPではIntelが自社開発したEMIB(イーミブ、Embedded Multi-die Interconnect Bridge)と呼ばれるチップレット技術が利用されている。EMIBはサブ基板の内部にブリッジ用のチップ(Embedded Silicon Bridge)でチップ同士を接続しており、通常のチップレットなどに比べてより高速にデータ通信を可能にしている。

第4世代Xeon SPでは、CPUパッケージのサブ基板上に4つのCPUタイル(Intelではチップレットでのダイのことをタイルと呼んでいる)をEMIBで接続する構造になっている。第4世代Xeon SPでは正方形に近いCPUタイルが4つサブ基板上に実装されているのがCPUの実物を見ると見てとれる。

Intelによれば、この4つのCPUタイルを基板上に実装しているのはXCC(eXtreme Core Count)と呼んでいる構成で、もう1つのMCC(Medium Core Count)は従来と同じモノリシック(単体)なダイになっている。Intelが公表した資料などを基に、XCC、MCCの構造をブロック図にしたものが以下の図になる。

既に述べたとおり、XCCは4つのCPUタイルから構成されており、1つのタイルにはGolden Coveコア(後述するが、第12世代Core、第13世代CoreのPコアとして採用されているCPUのマイクロアーキテクチャ)のCPUが15個あり、それぞれに2チャンネルのDDR5メモリコントローラ、さらに2つのPCI Express Gen 5のコントローラ、1つのUPIコントローラ、そしてHBM2eのメモリコントローラも用意されている(ただし、HBM2eのメモリコントローラはMaxシリーズのみで利用され、通常版の第4世代Xeonでは無効にされている)。

また、CPUタイル1つにはそれぞれにQAT、DLB、DSA、IAAといったハードウェアアクセラレータが用意されている(ハードウェアアクセラレータに関しては後述する)。

まとめると、CPUタイル、そしてCPUパッケージ全体でCPUコア、PCI Expressコントローラ、UPIコントローラ、アクセラレータなどをまとめると、以下のような数があることになる。

| CPUタイル | XCC全体 | |

|---|---|---|

| CPUコア数 | 15 | 60 |

| メモリコントローラ | DDR5(2)/HBM(1) | DDR5(8)/HBM(4) |

| PCI Express Gen 5 | 2 | 8 |

| UPI | 1 | 4 |

| QAT | 1 | 4 |

| DLB | 1 | 4 |

| DSA | 1 | 4 |

| IAA | 1 | 4 |

CPUタイルそれぞれにメモリコントローラやアクセラレータ、PCI Expressコントローラなどを搭載していることで、それぞれ複数が使えるようになっており、CPUタイル同士をCPUタイル内部とメッシュインターコネクトで接続することで、性能を大きく低下させることなくチップレットの仕組みを実現している。

MCCはアーキテクチャ的には34コア、製品レベルでは32コアという構成に

MCCの方は、32コア以下のSKUで利用され、アーキテクチャ的には34コアのCPUが用意されている。しかし、MCCで最上位構成のSKUは32コアで、2コアは標準状態で無効になっている。8チャンネルDDR5メモリコントーラという仕様は同じだが、PCI Express Gen 5コントローラは6つとXCCに比べて2つ少ないことになる。

また、アクセラレータは、XCCではCPUタイル1つに4種類のアクセラレータが搭載されており、それぞれが4つ搭載されていた。MCCではQATとDLBが2つあることになっており、DSAとIAAについては1つとなっている。

こうしたMCCの構成を見ていると、同じ30コア前後の構成であれば、XCCに採用されているCPUタイルを2つ利用して30コア製品としてMCCにすれば良いのではと考えたくなるだろう。しかし、その場合CPUタイル1つにはメモリコントローラは2チャンネルしかないので、CPUタイル2つではメモリは4チャンネルになってしまい、データセンター向けCPUとしてはメモリ帯域が十分ではなくなってしまう。

これを避けるためには、AMDがEPYCで採用しているように、メモリコントローラは別ダイにしてCPUと分離しないといけなくなるだろう。今回のXCCではそのデザインを採用しなかったので、MCCをモノリシックのダイにしたのは論理的な選択といえる。

Xeon Maxシリーズは、既に11月に概要が発表されている通り、第4世代Xeon SPに、64GBのHBM2eメモリを追加したバージョンになる(このため、Sapphire Rapids with High Bandwidth Memoryと別の開発コードネームが与えられてきた)。

Xeon MaxではCPUコアは最大56コアになり、標準状態で4つのコアが無効にされているほか、アクセラレータはDSAのみが有効にされておりmQATなどほかの3つは無効にされている。

CPUはGolden Coveに強化されSTで15%性能向上、AMXに対応したAI推論性能が大幅アップ

CPUコアは、クライアントPC向けの第12世代/第13世代CoreのPコアで採用されているGolden Coveコアになっている。前世代となる第3世代Xeon SP(Ice Lake-SP)ではCoveシリーズの最初の世代となるSunny Coveから、クライアントPC向けでいえば2世代進化したことになる。

採用されているGolden Coveは第12世代Core向けのL2キャッシュが1.25MB版ではなく、第13世代Coreに採用されているL2キャッシュが2MBになっているバージョンになっている(クライアントPCではそれをRaptor Coveと呼んでいる)。

Golden Coveでは、Sunny Coveに比べるとフロントエンド(デコーダや分岐予測など)が大きく強化されているほか、L2キャッシュもL3キャッシュも増やされており、世代間のIPC(Instruction Per Clock-cycle、1周波数あたりに実行できる命令数のこと、数字が大きければ大きいほどCPUの実行効率が良いことを意味する)が15%向上している。つまり、シングルスレッドで処理を行なうと15%性能が向上するということを意味する。

それと同時に、ソケット1つあたりのCPUコア数が増えている。第3世代Xeon SPではモノリシックダイだったため、1ソケットで40コアが最大構成になっていた。それに対して第4世代Xeon SPのXCCでは最大60コアになっており、CPUコア数が約1.5倍になっている。それにより、1ソケットあたりのマルチスレッド性能も向上している。

また、第4世代Xeon SPではx86の拡張命令セットとして2つの拡張命令セットが追加されている。1つはAMX(Advanced Matrix eXtensions)で、AMXはCPUに搭載された新しい演算器「TMUL(Tile Matrix multiply Unit)」を利用して効率よく行列演算を行なう仕組みになる。こうした拡張命令は、最近のAI推論処理を行なうプロセッサー(CPU/GPU)で搭載されることがトレンドになっていて、AMXもそうした拡張命令の1つと考えてよい。

AMXに対応したCPUでは、2つのTMULエンジンが内蔵されており、それを利用して行列演算を効率よく行なうことができる。これにより、BF16を利用してAI推論を行う時により高効率で演算することができる。

また、AVX512の拡張として用意される「Advanced Vector Extensions for vRAN」は、5GのRAN(Radio Access Network)を汎用プロセッサで構築するアプリケーション(vRAN)に利用する場合に、FP16を利用して複雑な乗算をAVX512で行なうことが可能になる。Advanced Vector Extensions for vRANではAVX512に42の新しい命令が追加され、FP16の演算時のスループットが2倍になり、vRANの性能を大きく引き上げることができる。

QAT、DLB、DSA、IAAという4つの種類のHWアクセラレータをそれぞれ4つ搭載

第4世代Xeon SPではそうした追加の拡張命令だけでなく、4つのハードウェアアクセラレータがCPUタイル(XCC)、CPUダイ(MCC)に統合されている。具体的にはQAT、DLB、DSA、IAAの4つになる。

QATはもともと初代Xeon SPの世代で暗号化/復号化のアクセラレータとしてチップセット側に統合されたアクセセラレータだが、今回の第4世代Xeon SPではそれがCPU側に統合されている。

DLBは、CPUにデータを読み込んで処理する際に、データを実行効率の良い順序に並べ替えてキューに入れて実行するためのアクセラレータになる。それによりCPUに負荷をかけることなく順序を入れ替えることができるので、CPUの利用効率を上げることができる。

DSAはメモリにデータを書き込む際に、その書き込みをDSAにより最適化することで、より効率よくメモリに書き込むことが可能になる。IAAは圧縮、解凍、スキャン/フィルタという3つのエンジンを内蔵しており、データを圧縮して読み込むことでメモリの帯域を節約することを可能にする。

こうしたアクセラレータはそれぞれCPUにかかる負荷をオフロードすることを目的としており、CPUのリソースを演算にだけ振り向けることができるだけでなく、CPUの電力効率を改善することを可能にする。さらに、「Optimized Power Mode」という電力効率優先のモードが用意されており、マザーボードのBIOS設定で有効にすることができ、5%程度の性能低下と引き換えに20%消費電力を下げることが可能になっている。

Intelによれば、こうしたアクセラレータやそうした電力効率優先モードを活用することで、電力効率は前世代に比べて2.9倍改善しているということだ。

XCCではこうしたアクセラレータがCPUタイルに1つずつ搭載される。このため、4つのタイルから構成されるソケット全体でそれぞれ4つのアクセラレータが搭載されていることになる。ただし、すべてのSKUでこうしたアクセラレータが有効になっているのかと言えばそうではなく、例えば最上位SKUとなるXeon Platinum 8490Hでは4種類4つ(合計16個)のアクセラレータすべてが有効になっているが、ほかのSKUでは4種類1つずつ(合計4つ)のアクセラレータが有効になっているなど、どの種類のアクセラレータと何個が使えるかはSKUに依存する(後述するSKU表を参照)。

Intelは今回の第4世代Xeon SPで新しい仕組みとして「Intel OnDemand」が導入される。これは、CPUに対して専用APIを介して無効になっているアクセラレータやCPUコアなどを有効にする仕組みで、OEMベンダーやCSPなどを経由して提供される有料サービスだ。

Intel OnDemandに対応したSKUだけで有効だが、ユーザーにすれば購入後にアクセラレータやCPUコアが追加で必要になった場合に購入することができる。購入後に機能を拡張できる仕組みはユニークで、CPUを交換しなくても機能を拡張できることは、OEMベンダーやCSPにとっても新しいビジネスとなる可能性を秘めている。

CPUソケットはLGA4189に、DDR5メモリ、80レーンのPCI Express Gen 5/CXL 1.1に対応

今回の第4世代Xeon SPでは、プラットホーム側も大きな拡張が入る。CPUソケットは従来のSocket P+(LGA4189)に代わって、Socket E(LGA4677)が導入される。ソケットが変更されるのは、PCI Expressのレーン数の増加やDDR5という新しいメモリに対応するためで、ピン数が違うことからも分かるように、ソケットの互換性はない。なお、チップセットも強化されており、新しくC741がチップセットとして提供される。

第3世代Xeon SPでは、1-2ソケットが開発コードネームIce Lake-SP、4-8ソケットが開発コードネームCooper Lakeと2つのラインアップに分割されていたが、第4世代Xeonでは1ソケットから8ソケットまで1つの製品でサポートすることができる。これはXCCでUPIが3つから4つに増やされ、新しい接続トポロジーが導入されたからだ。なお、UPIは第3世代Xeon SPでの12GT/sから転送速度は引き上げられて、16GT/sと強化されている。

UPIが4コントローラなのはXCCだけあり、MCCは3コントローラであるため4ソケットまでの対応となる。XCCでも8ソケットで利用する場合には、8ソケットまでをサポートするSKUを選ぶ必要がある。

| ブランド名 | Xeon 5600番台 | Xeon E5 | Xeon E5 v2 | Xeon E5 v3 | Xeon E5 v4 | Xeon SP | 第2世代Xeon SP | 第3世代Xeon SP(4-8S) | 第3世代Xeon SP(1-2S) | 第4世代Xeon SP |

|---|---|---|---|---|---|---|---|---|---|---|

| 開発コードネーム | Westmere-EP | Sandy Bridge-EP | Ivy Bridge-EP | Haswell-EP | Broadwell-EP | Skylake-SP | Cascade Lake-SP | Cooper Lake | Ice Lake | Sapphire Rapids |

| リリース年 | 2010年 | 2012年 | 2013年 | 2014年 | 2016年 | 2017年 | 2019年 | 2020年 | 2021年 | 2023年 |

| 製造プロセスルール | 32nm | 32nm | 22nm | 22nm | 14nm | 14nm | 14nm | 14nm | 10nm | Intel 7(10nm Enhanced Superfin) |

| CPUコア(ソケットあたり最大) | 6 | 8 | 12 | 18 | 22 | 28 | 56 | 28 | 40 | 60 |

| ダイ構成(HCC、MCC、LCC) | 6 | 8 | 15、10、6 | 18、12、8 | 24、15、10 | 28、18、10 | 28、18、10 | 28、18、10 | 非公表 | 60、32、LCCなし |

| パッケージあたりのダイ数 | 1 | 1 | 1 | 1 | 1 | 1 | 1(パッケージ)/2(BGA) | 1 | 1 | 4(HCC版)/1(MCC) |

| L2キャッシュ(コアあたり) | 256KB | 256KB | 256KB | 256KB | 256KB | 1MB | 1MB | 1MB | 1.25MB | 2MB |

| LLCキャッシュ(コアあたり) | 2MB | 2.5MB | 2.5MB | 2.5MB | 2.5MB | 1.375MB | 1.375MB | 1.375MB | 1.5MB | 1.875MB |

| LLCキャッシュ(ダイあたり最大) | 12MB | 20MB | 30MB/20MB/15MB | 45MB/30MB/20MB | 55MB/37.5MB/25MB | 38.5MB/24.75MB/13.75MB | 38.5MB/24.75MB/13.75MB | 38.5MB/24.75MB/13.75MB | 最大60MB | 最大112.5 |

| コアマイクロアーキテクチャ | Nehalem世代 | Sandy Bridge世代 | Sandy Bridge世代(改良版) | Haswell世代 | Haswell世代(改良版) | Skylake世代 | Skylake世代 | Skylake世代 | Sunny Cove | Golden Cove |

| コア間インターコネクト | - | リング | リング | リング | リング | メッシュ | メッシュ | メッシュ | メッシュ | メッシュ |

| CPUソケット | Socket B(LGA1366) | Socket R(LGA2011) | Socket R(LGA2011) | Socket R3(LGA2011v3) | Socket R3(LGA2011v3) | Socket P(LGA3647) | Socket P(LGA3647)/BGA(5903ball、2ダイ構成) | Socket P+(LGA4189) | Socket P+(LGA4189) | Socket E(LGA4677) |

| 最大ソケット | 2 | 2 | 2 | 2 | 2 | 2/4/8 | 2/4/8 | 4/8 | 2 | 2/4/8 |

| 最大メモリ容量(ソケットあたり) | 288GB | 384GB | 768GB | 1.5TB | 1.5TB | 1.5TB | 4.5TB(Optane DCPM利用時) | 4.5TB(Optane DCPM利用時) | 4TB(DDRのみ)/6TB(DDR+Optane) | 4TB(DDR5)/6TB(DDR+Optane) |

| メモリ | DDR3-1333 | DDR3-1600 | DDR3-1866 | DDR4-2133 | DDR4-2400 | DDR4-2666 | DDR4-2933 | DDR4-3200 | DDR4-3200 | DDR5-4800(1DPC)/4400(2DPC) |

| Optane DC Persistent Memory対応 | - | - | - | - | - | - | ○ | ○(200シリーズ) | ○(200シリーズ) | ○(300シリーズ) |

| メモリチャネル数(CPUソケットあたり) | 3 | 4 | 4 | 4 | 4 | 6 | 6/12 | 6 | 8 | 8 |

| 拡張命令:AVX | - | - | AVX | AVX2 | AVX2/TSX | AVX512 | AVX512 /w Intel DL Boost(VNNI) | AVX512 /w Intel DL Boost(VNNI) | AVX512 /w Intel DL Boost(VNNI) | AVX512 /w Intel DL Boost(VNNI) |

| 拡張命令:AMX | - | - | - | - | - | - | - | - | - | 対応 |

| QPI/UPI(ダイあたり) | 2x最大6.4GT/s | 2x最大8GT/s | 2x最大8GT/s | 2x最大9.6GT/s | 2x最大9.6GT/s | 3x最大10.4GT/s | 3x最大10.4GT/s | 6x最大10.4GT/s | 3x最大11.2GT/s | 4x最大16GT/s |

| PCI Express(CPU側) | PCI Express Gen2(チップセット側) | PCI Express Gen 3 | PCI Express Gen 3 | PCI Express Gen 3 | PCI Express Gen 3 | PCI Express Gen 3 | PCI Express Gen 3 | PCI Express Gen 3 | PCI Express Gen 4 | PCI Express Gen 5 |

| PCI Expressレーン数(CPU側/ソケットあたり) | 36(チップセット側) | 40 | 40 | 40 | 40 | 64(MCC/LCCは48) | 48 | 48 | 64 | 80 |

| CXL | - | - | - | - | - | - | - | - | - | 1.1(最大4デバイス) |

| DMI | - | DMI/Gen2(4レーン) | DMI/Gen2(4レーン) | DMI/Gen2(4レーン) | DMI/Gen2(4レーン) | DMI/Gen3(4レーン) | DMI/Gen3(4レーン) | DMI/Gen3(4レーン) | DMI/Gen3(4レーン) | DMI/Gen4(8レーン) |

| チップセット | 5500(Tyrusburg) | C600(Patsburg) | C600(Patsburg) | C610(Wellsburg) | C610(Wellsburg) | C620(Lewisburg) | C620(Lewisburg) | C620A(Lewisburg R) | C620A(Lewisburg R) | C741 |

メモリはDDR5に変更されている。メモリチャンネルは第3世代Xeon SPと同じ8チャンネルで、1DPC(1DIMM per Channel)であればDDR5-4800、2DPCであればDDR5-4400で利用することができる。256GBのDDR5のR-DIMMを2DPCで利用した場合、1ソケットあたり最大4TBのメモリを実装することができる。

なお、既にIntelはビジネスのクローズを明らかにしているOptane Persistent Memoryも引き続きサポートされており、最新のOptane Persistent Memory 300シリーズを利用することができる。DDR5とOptaneを組み合わせた場合は1ソケットあたり最大6TBのメモリ容量を利用することができる。

PCI ExpressはGen 5に強化され、最大80レーンを利用することができる。PCI Expressにコヒーレントの機能を追加したCXL(Compute eXpress Link)のバージョン1.1にも対応しており、Type1とType2デバイスを最大4デバイスまで利用することができる。

TDPは最大350Wに引き上げられる、真価を発揮するにはAMX/HWアクセラレータへの対応が必須

今回発表された第4世代Xeon SPのSKU構成と価格(参考価格、税別)は以下のようになっている

| 対象市場 | シリーズ | SKU | コア数 | ベースクロック(GHz) | ターボ時最大クロック(マルチコア/GHz) | ターボ時最大クロック(シングルコア/GHz) | L3キャッシュ(MB) | TDP(W) | 最大ソケット数 | DDR5速度 | UPIリンク数 | DSA | QAT | DLB | IAA | SGX Enclave容量(GB) | Intel OnDemand対応 | ダイ | 奨励顧客価格(RCP/米ドル) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 2Sパフォーマンス汎用 | Platinum | 8480+ | 56 | 2 | 3 | 3.8 | 105 | 350 | 2 | 4800 | 4 | 1 | 1 | 1 | 1 | 512 | ○ | XCC | 10710 |

| Platinum | 8470 | 52 | 2 | 3 | 3.8 | 105 | 350 | 2 | 4800 | 4 | 1 | 0 | 0 | 0 | 512 | ○ | XCC | 9359 | |

| Platinum | 8468 | 48 | 2.1 | 3.1 | 3.8 | 105 | 350 | 2 | 4800 | 4 | 1 | 0 | 0 | 0 | 512 | ○ | XCC | 7214 | |

| Platinum | 8486Y+ | 40 | 2 | 2.8 | 3.7 | 105 | 300 | 2 | 4800 | 4 | 1 | 1 | 1 | 1 | 128 | ○ | XCC | 5558 | |

| Platinum | 8462Y+ | 32 | 2.8 | 3.6 | 4.1 | 60 | 300 | 2 | 4800 | 3 | 1 | 1 | 1 | 1 | 128 | ○ | XCC | 5945 | |

| Gold | 6448Y | 32 | 2.1 | 3 | 4.1 | 60 | 225 | 2 | 4800 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 3583 | |

| Gold | 6442Y | 24 | 2.6 | 3.3 | 4 | 60 | 225 | 2 | 4800 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 2878 | |

| Gold | 6444Y | 16 | 3.6 | 4 | 4.1 | 45 | 270 | 2 | 4800 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 3622 | |

| Gold | 6426Y | 16 | 2.3 | 3.3 | 4.1 | 37.5 | 185 | 2 | 4800 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 1517 | |

| Gold | 6434 | 8 | 3.7 | 4.1 | 4.1 | 22.5 | 195 | 2 | 4800 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 2607 | |

| Gold | 5415+ | 8 | 2.9 | 3.6 | 4.1 | 22.5 | 150 | 2 | 4400 | 3 | 1 | 1 | 1 | 1 | 128 | ○ | MCC | 1066 | |

| 2Sメインストリーム汎用 | Platinum | 8452Y | 36 | 2 | 2.8 | 3.2 | 67.5 | 300 | 2 | 4800 | 4 | 1 | 0 | 0 | 0 | 128 | ○ | XCC | 3995 |

| Gold | 6438Y+ | 32 | 2 | 2.8 | 4 | 60 | 205 | 2 | 4800 | 3 | 1 | 1 | 1 | 1 | 128 | ○ | MCC | 3141 | |

| Gold | 6430 | 32 | 2.1 | 2.6 | 3.4 | 60 | 270 | 2 | 4400 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | XCC | 2128 | |

| Gold | 5420+ | 28 | 2 | 2.7 | 4.1 | 52.5 | 205 | 2 | 4400 | 3 | 1 | 1 | 1 | 1 | 128 | ○ | MCC | 1848 | |

| Gold | 5418Y | 24 | 2 | 2.8 | 3.8 | 45 | 185 | 2 | 4400 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 1483 | |

| Silver | 4416+ | 20 | 2 | 2.9 | 3.9 | 37.5 | 165 | 2 | 4400 | 2 | 1 | 1 | 1 | 1 | 64 | ○ | MCC | 1176 | |

| Silver | 4410Y | 12 | 2 | 2.8 | 3.9 | 30 | 150 | 2 | 4000 | 2 | 1 | 0 | 0 | 0 | 64 | ○ | MCC | 563 | |

| 液冷汎用 | Platinum | 8470Q | 52 | 2.1 | 3.2 | 3.8 | 105 | 350 | 2 | 4800 | 4 | 1 | 0 | 0 | 0 | 512 | ○ | XCC | 9410 |

| Gold | 6458Q | 32 | 3.1 | 4 | 4 | 60 | 350 | 2 | 4800 | 3 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 6416 | |

| 1S汎用 | Gold | 6414U | 32 | 2 | 2.6 | 3.4 | 60 | 250 | 1 | 4800 | 0 | 1 | 0 | 0 | 0 | 512 | ○ | XCC | 2296 |

| Gold | 5412U | 24 | 2.1 | 2.9 | 3.9 | 45 | 185 | 1 | 4400 | 0 | 1 | 0 | 0 | 0 | 128 | ○ | MCC | 1113 | |

| Bronze | 3408J | 8 | 1.8 | 1.9 | 1.9 | 22.5 | 125 | 1 | 4400 | 0 | 1 | 0 | 0 | 0 | 64 | - | MCC | 415 | |

| 長寿命(IOT)汎用 | Silver | 4410T | 10 | 2.7 | 3.4 | 4 | 26.25 | 150 | 2 | 4000 | 2 | 1 | 0 | 0 | 0 | 64 | ○ | MCC | 624 |

| IMDB/アナリティクス/仮想化最適(ソケット拡張可能) | Platinum | 8490H | 60 | 1.9 | 2.9 | 3.5 | 112.5 | 350 | 8 | 4800 | 4 | 4 | 4 | 4 | 4 | 512 | - | XCC | 17000 |

| Platinum | 8468H | 48 | 2.1 | 3 | 3.8 | 105 | 330 | 8 | 4800 | 4 | 4 | 4 | 4 | 4 | 512 | - | XCC | 13923 | |

| Platinum | 8460H | 40 | 2.2 | 3.1 | 3.8 | 105 | 330 | 8 | 4800 | 4 | 4 | 0 | 0 | 4 | 512 | - | XCC | 10710 | |

| Platinum | 8454H | 32 | 2.1 | 2.7 | 3.4 | 82.5 | 270 | 8 | 4800 | 4 | 4 | 4 | 4 | 4 | 512 | - | XCC | 6450 | |

| Platinum | 8450H | 28 | 2 | 2.6 | 3.5 | 75 | 250 | 8 | 4800 | 4 | 4 | 0 | 0 | 4 | 512 | - | XCC | 4708 | |

| Platinum | 8444H | 16 | 2.9 | 3.2 | 4 | 45 | 270 | 8 | 4800 | 4 | 4 | 0 | 0 | 4 | 512 | - | XCC | 4234 | |

| Gold | 6448H | 32 | 2.4 | 3.2 | 4.1 | 60 | 250 | 4 | 4800 | 3 | 1 | 2 | 2 | 1 | 512 | - | MCC | 3658 | |

| Gold | 6418H | 24 | 2.1 | 2.9 | 4 | 60 | 185 | 4 | 4800 | 3 | 1 | 0 | 0 | 1 | 512 | - | MCC | 2065 | |

| Gold | 6416H | 18 | 2.2 | 2.9 | 4.2 | 45 | 165 | 4 | 4800 | 3 | 1 | 0 | 0 | 1 | 512 | - | MCC | 1444 | |

| Gold | 6434H | 8 | 3.7 | 4.1 | 4.1 | 22.5 | 195 | 4 | 4800 | 3 | 1 | 0 | 0 | 1 | 512 | - | MCC | 3070 | |

| 5G/ネットワーキング最適 | Platinum | 8470N | 52 | 1.7 | 2.7 | 3.6 | 97.5 | 300 | 2 | 4800 | 4 | 4 | 4 | 4 | 0 | 128 | ○ | XCC | 9520 |

| Platinum | 8471N | 52 | 1.8 | 2.8 | 3.6 | 97.5 | 300 | 1 | 4800 | 4 | 4 | 4 | 4 | 0 | 128 | ○ | XCC | 5171 | |

| Gold | 6438N | 32 | 2 | 2.7 | 3.6 | 60 | 205 | 2 | 4800 | 3 | 1 | 2 | 2 | 0 | 128 | ○ | MCC | 3351 | |

| Gold | 6428N | 32 | 1.8 | 2.5 | 3.8 | 60 | 185 | 2 | 4000 | 3 | 1 | 2 | 2 | 0 | 128 | ○ | MCC | 3200 | |

| Gold | 6412N | 32 | 1.8 | 2.6 | 3.6 | 60 | 185 | 1 | 4400 | 3 | 1 | 2 | 2 | 0 | 128 | ○ | MCC | 2368 | |

| Gold | 5418N | 24 | 1.8 | 2.6 | 3.8 | 45 | 165 | 2 | 4000 | 3 | 1 | 2 | 2 | 0 | 128 | ○ | MCC | 1664 | |

| Gold | 5411N | 24 | 1.9 | 2.8 | 3.9 | 45 | 165 | 1 | 4400 | 3 | 1 | 2 | 2 | 0 | 128 | ○ | MCC | 1232 | |

| クラウド最適化(IaaS -P/SaaS -V/Media ーM) | Platinum | 8468V | 48 | 2.4 | 2.9 | 3.8 | 97.5 | 330 | 2 | 4800 | 3 | 1 | 1 | 1 | 1 | 128 | ○ | XCC | 7121 |

| Platinum | 8458P | 44 | 2.7 | 3.2 | 3.8 | 82.5 | 350 | 2 | 4800 | 3 | 1 | 1 | 1 | 1 | 512 | ○ | XCC | 6759 | |

| Platinum | 8461V | 48 | 2.2 | 2.8 | 3.7 | 97.5 | 300 | 1 | 4800 | 0 | 1 | 1 | 1 | 1 | 128 | ○ | XCC | 4491 | |

| Gold | 6438M | 32 | 2.2 | 2.8 | 3.9 | 60 | 205 | 2 | 4800 | 3 | 1 | 0 | 0 | 2 | 128 | ○ | MCC | 3273 | |

| ストレージ/HCI最適化 | Gold | 6454S | 32 | 2.2 | 2.8 | 3.4 | 60 | 270 | 2 | 4800 | 4 | 4 | 4 | 4 | 0 | 128 | ○ | XCC | 3157 |

| Gold | 5416S | 16 | 2 | 2.8 | 4 | 30 | 150 | 2 | 4400 | 3 | 1 | 2 | 2 | 0 | 128 | ○ | MCC | 944 | |

| HPC | Max | 9480 | 56 | 1.9 | 2.6 | 3.5 | 112.5 | 350 | 2 | 4800 | 4 | 4 | 0 | 0 | 0 | 512 | - | XCC | 12980 |

| Max | 9470 | 52 | 2 | 2.7 | 3.5 | 105 | 350 | 2 | 4800 | 4 | 4 | 0 | 0 | 0 | 512 | - | XCC | 11590 | |

| Max | 9468 | 48 | 2.1 | 2.6 | 3.5 | 105 | 350 | 2 | 4800 | 4 | 4 | 0 | 0 | 0 | 512 | - | XCC | 9900 | |

| Max | 9460 | 40 | 2.2 | 2.7 | 3.5 | 97.5 | 350 | 2 | 4800 | 3 | 4 | 0 | 0 | 0 | 128 | - | XCC | 8750 | |

| Max | 9462 | 32 | 2.7 | 3.1 | 3.5 | 75 | 350 | 2 | 4800 | 3 | 4 | 0 | 0 | 0 | 128 | - | XCC | 7995 |

今回の第4世代Xeon SPからIntelはSKU構成を、ターゲット市場別にして提供することにしている。2Sパフォーマンス汎用、2Sメインストリーム汎用、液冷汎用、1ソケット汎用、長寿命(IOT)汎用、IMDB/アナリティクス/仮想化最適(ソケット拡張可能)、5G/ネットワーキング最適、クラウド最適化、ストレージ/HCI最適化、HPC(Xeon Maxシリーズ)などのターゲット市場に向けてSKUが用意されている。

注意したいのはTDPで、従来の第3世代Xeon SPでは最大270Wになっていたが、第4世代Xeon SPではそれが最大350Wに拡張されている。こうした傾向にあるのは第4世代Xeonだけでなく、競合となるAMDの第4世代EPYCも、最上位SKUでは標準で360W、cTDPでは400Wが可能になっており、それだけのTDPの電力量で発生する熱を確実に放熱すると考えると、従来のヒートシンク+ファンという空冷では十分ではない可能性が高い。

このため、OEMメーカーはヒートシンクをより大型にして、ファンの数を増やして対応するというところが多い。場合によっては液冷、液浸(専用の油に漬けてシステム全体で冷やす冷却方法)などのさらに高効率な冷却システムを検討する場合も出てくるだろう。

最後に第4世代Xeon SPの性能について説明しておきたい。Intelが公表した第3世代Xeon SPと第4世代Xeon SPとの比較データは以下の通りだ。

データベースやWeb、メディアなどではおおむね1.5~2倍程度の性能を発揮し、大きな性能向上が発揮されているのはインメモリデータベースのRockDBの2.93倍などで、この場合にはIAAアクセラレータを有効にした結果2.93倍という結果が得られていると考えることができる。同じことはAI推論のSSD-RN34(RT推論/BF16)の10倍という結果も同様で、こちらはAMXでBF16を利用して演算した場合の結果になっている。

こうした結果からも分かるように、第4世代Xeonの真価を発揮させるにはAMXなどの新しい拡張命令やハードウェアアクセラレータをソフトウェアが利用できるようにする必要がある。IntelはISV(独立系ソフトウェアベンダー)に対して、AMXやハードウェアアクセラレータを利用できる開発キットを合わせて提供している。第4世代Xeon SPの導入を検討しているのなら、同時に利用しているソフトウェアがAMXやQAT/DLB/DSA/IAAなどのアクセラレータに対応しているかどうかをチェックしておくと良いだろう。

![[アウトレット] ゲーミングモニター ホワイト パステル ブルー 200hz 24インチ pcモニター 144Hz 165Hz対応 モニター 白 フルHD IPS HDR ノングレア スピーカー搭載 VESA 23.8インチ 液晶ディスプレイ Pixio ピクシオ 公式 PX248WAVE 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/pixiogaming/cabinet/outlet/px248w-outlet.jpg?_ex=128x128)

![\数量限定★モニター台プレゼント~5/31まで/モニター 27インチ フルhd 高画質 100Hz VA ノングレア 非光沢 スピーカー内蔵 3年保証 ディスプレイ パソコンモニター PCモニター フルハイビジョン 液晶モニター DT-JF * 安心延長保証対象 [安心延長保証対象] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/irisplaza-r/cabinet/12113165/imgrc0119761485.jpg?_ex=128x128)

![I-O DATA|アイ・オー・データ USB-C接続 PCモニター ブラック KH-C242SDB [23.8型 /フルHD(1920×1080) /ワイド /100Hz] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/13736/00000014311266_a01.jpg?_ex=128x128)

![転生したらスライムだった件(32) (シリウスKC) [ 川上 泰樹 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7544/9784065437544.gif?_ex=128x128)

![わたしはこれでやせました [ MEGUMI ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4512/9784478124512_1_2.jpg?_ex=128x128)

![貴族転生 〜恵まれた生まれから最強の力を得る〜 11巻 【電子書籍】[ 三木なずな ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0537/2000020190537.jpg?_ex=128x128)

![神達に拾われた男 16巻 【電子書籍】[ Roy ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0541/2000020190541.jpg?_ex=128x128)

![例解学習国語辞典第十二版・漢字辞典新装版 名探偵コナンバッグ付きセット [ 小学館 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9581/9784095019581_1_2.jpg?_ex=128x128)

![例解学習国語辞典 第十二版 オールカラー [ 金田一 京助 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7129/9784095017129_1_14.jpg?_ex=128x128)

![改訂版 本当の自由を手に入れる お金の大学 [ 両@リベ大学長 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3780/9784023323780_1_5.jpg?_ex=128x128)

![辺境モブ貴族のウチに嫁いできた悪役令嬢が、めちゃくちゃできる良い嫁なんだが? 3 【電子書籍】[ tera ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9041/2000020419041.jpg?_ex=128x128)

![黄泉のツガイ(13) (ガンガンコミックス) [ 荒川弘 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6343/9784301006343.gif?_ex=128x128)