福田昭のセミコン業界最前線

3D XPointメモリの全体像、ようやく明らかに。Micronが第2世代の技術概要を公表

2023年12月26日 06:14

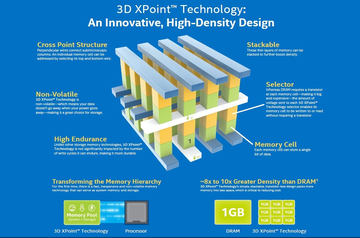

Micron Technologyが第2世代の「3D XPoint」メモリ技術を国際学会「IEDM 2023」で発表した(講演番号21-4)。3D XPointメモリ技術は、IntelとMicron Technology(以降はMicronと表記)が2015年7月28日(米国時間)に共同開発をアナウンスした大容量高速不揮発性メモリ技術として知られる。2017年3月にはサーバー向け高速SSD「Optane SSD DC P4800X」を、2017年4月にはHDDキャッシュ用のM2カード「Optane Memory Series」をIntelが製品化した。なお「Optane」はIntelが3D XPointメモリ搭載製品に名付けたブランド名である。

初代(第1世代)の3D XPointメモリは記憶容量が128Gbitと2017年当時のDRAM(最大8Gbit)よりもはるかに大きい。アクセス速度はNANDフラッシュメモリよりも大幅に高いとされたが、チップ単体の測定値は明らかにされなかった。それでもランダムアクセスが可能であることが、NANDフラッシュに対する優位性として高く評価された。ストレージ(SSD)で実測した比較値は、IntelとMicronのそれぞれが2016年に発表済みである。その内容は入出力速度(IOPS)がNANDフラッシュSSD(PCIeインターフェイス)の7.7倍~10倍、レイテンシがNANDフラッシュSSDの8.4分の1~10分の1というものだ。

製造技術は開発元よりも先に外部企業がチップを解析して公表

3D XPointメモリ技術は半導体メモリ業界の強い注目を集めたものの、開発元であるIntelとMicronは技術情報をほとんど公開しなかった。最初の発表から2年半を経過した2017年末の段階でも、IntelとMicronによって公表された技術情報は、ごく限定的なものだった。第1世代の3D XPointメモリ技術(2層の3次元クロスポイント構造)によって記憶容量が128Gbitのシリコンダイを開発したこと、メモリセルは記憶素子とセル選択素子(セレクタ)を垂直に積層した構造であること、シリコンダイとウェハを撮影した画像データ、試作したSSDの性能をNANDフラッシュのSSDと比較した結果、それから第2世代の3D XPointメモリ技術(4層の3次元クロスポイント構造)を開発する計画があること、などに過ぎない。

逆に、以下のような詳細が「公式には」不明だった。設計ルール(製造技術ノード)、記憶素子の原理と材料、セレクタの原理と材料、メモリセルの電極材料、メモリセルの面積(あるいは寸法)、シリコンダイの面積(あるいは寸法)、記憶密度、メモリセルアレイの面積効率(シリコンダイ全体に占めるメモリセルアレイの割合)、データ保持期間、書き換えサイクル寿命、シリコンダイのレイアウト(フロアプラン)、シリコンダイのメモリセルアレイと周辺回路の構造、読み出しアクセス時間、書き込みアクセス時間、待機時および動作時の消費電力、などである。

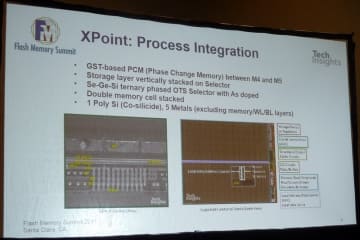

さらに、3D XPointメモリは単体では販売されず、HDDキャッシュやSSDといったモジュール製品として販売された。このため、シリコンダイの解析サービス企業TechInsightsがモジュール製品を入手して第1世代のメモリチップを取り出し、内部を解析した結果が、半導体メモリのコミュニティでは貴重な技術情報となった(参考記事)。2017年8月に米国で開催されたフラッシュメモリと応用品に関するイベント「FMS(Flash Memory Summit)」でTechInsightsは、HDDキャッシュから取り出したメモリチップを解析した結果の一部を公表した。

Intelが2020年12月に第1世代の技術概要を国際学会IEDMで公表

チップ解析サービス企業TechInsightsのおかけで、サイズ、プロセス技術、材料に関する、いわゆる物理的な情報はかなり明らかになった。ただし、アクセス時間や動作周波数などの電気的な特性は、チップ解析によって取り出すことは難しい。チップ解析は半導体チップをパッケージレベルからシリコンダイレベル、さらにはダイの内部へと構造を破壊しながら解析する手法だからだ。

あらかじめパッケージのピン配列が分かっていれば、プロービングによって電気的な特性を探ることは可能だろう。しかし3D XPointメモリ単体は市販されておらず、従ってデータシートがない。パッケージのどの端子がどの信号に対応するかが不明であるから、電気的な特性の解析はほぼ不可能だ。

そんな中、2020年12月に開催された国際学会IEDMでIntelが、初代3D XPointメモリ技術を一部、公表した(講演番号24.1)。ここで初めて、電気的な特性が公式に明らかになった。

読み出し遅延時間は100ns、書き込み遅延時間は500nsと、いずれもかなり短い。特に書き込み遅延時間はNANDフラッシュメモリの数十分の1~数百分の1しかない。そして書き込みスループットは約3.4Gbpsとこれも非常に高い。長期信頼性に関するデータは公表されなかった。

そして製造技術に関する部分は、TechInsightsが2017年8月にFMSで公表した内容と完全に一致していた。厳密には、Intelが公表した製造技術に関する内容は、TechInsightsが公表した内容に劣っていた。公表した範囲が狭かった。それでもTechInsightsが公表していなかった、いくつかの要素技術がIntelの公式発表からはもたらされた。

たとえば、メモリセルの構造である。前述のように、TechInsightsが公表したメモリセルの構造と材料にはいくつか、空欄がある。トップ電極層や中間電極層、ボトム電極層などだ。Intelはこれらの電極層が炭素(カーボン)電極であることを明らかにした。

「バルク的な相変化」によって書き込みを高速化

また相変化型記憶(PCM)素子の相変化は、従来とは異なる原理によって引き起こされていることが説明された。相変化型記憶素子では、カルコゲナイド合金が結晶相(低抵抗状態あるいはセット状態)とアモルファス相(高抵抗状態あるいはリセット状態)の2つの相状態を行き来する性質を利用して1bitの論理値を記憶させる。

従来の相変化型記憶素子では、電極(上部電極あるいは下部電極)とカルコゲナイド合金層の間に設けたヒーターによって結晶状態のカルコゲナイド合金層を加熱し、その一部をアモルファス相に変化させることで素子の電気抵抗を変化させていた。

ところがIntelのIEDM論文によると、3D XPointメモリの相変化型記憶素子は、素子領域全体の原子間結合が変化することで材料全体が一気に相変化する。2015年7月の開発当初から「バルク的な相変化」とIntelが表現していたのは、このことだと理解できる。また一部ではなく全体の結晶構造を一気に変化させるので、検証(ベリファイ)作業が不要になったとする。これは書き込み時間の短縮に寄与する、大きな利点だ。ただし残念ながら、どのようにして「バルク的な相変化」を起こしているかは明らかにしていない。

第2世代3D XPointメモリではデータ保持期間が初めて明らかに

画期的な技術と将来性を備えた高速大容量不揮発性メモリとして将来が期待された3D XPointメモリだが、ご存知のように商業的にはあまり上手くいかなかった。2021年3月にMicronは、同メモリの開発休止と製造拠点の売却を公式に発表する。残るIntelは2022年7月28日付けの同年第2四半期業績発表資料に「Optane事業を段階的に縮小する」ことと、「Optaneメモリの在庫を減損処理した」ことを記述した。事実上の撤退である。3D XPointメモリの歴史は7年で途絶えた。

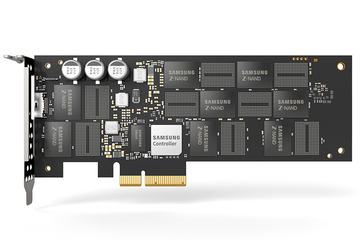

MicronがIEDM 2023で発表した第2世代の3D XPointメモリ技術(論文番号21-4)は、64Gbitのクロスポイント構造セルアレイを4枚積層した、記憶容量が256Gbitの不揮発性メモリである。すでにこのことは、チップ解析サービス企業TechInsightsが第2世代チップの解析結果として2021年6月に公表済みだ(参考記事を参照)。プロセス技術やメモリセル構造などが第1世代とほぼ変わらないことも、すでに同社のレポートによって分かっている。

重要なのはIntelの第1世代に関する発表と同様に、電気的な特性が公表されたことにある。読み出し遅延時間は100ns、書き込み遅延時間は500nsと第1世代と変わらない。データ保持期間は7年(40℃)と初めて公表された。しかもあまり長くない(通常の不揮発性メモリ製品はデータ保持期間が10年(85℃))。書き換えサイクル寿命はまたもや公表されなかった。消費電力も未公表に終わった。

またSSDに応用したときのランダムアクセス時間(遅延時間)をZ-NAND(SLC方式の3D NANDフラッシュによる高速メモリ)のSSDと比較したデータも公表した。Z-NANDと比較しても遅延時間は約20分の1以下と短い。

3D XPointメモリの開発休止をMicronがアナウンスしてから4年近くが経過した。IEDM 2023でのMicronによる発表は招待講演なので「そろそろ技術情報を公開しても良いでしょう」という意図が働いたことが伺える。それだけではなく、次世代の高速大容量クロスポイントメモリ技術についてもMicronは言及した。この次世代技術については機会を改めて述べたい。

![【Amazon.co.jp限定】 伊藤園 磨かれて、澄みきった日本の水 2L 8本 ラベルレス [ ケース ] [ 水 ] [ 軟水 ] [ ペットボトル ] [ 箱買い ] [ ストック ] [ 水分補給 ] 製品画像:3位](https://m.media-amazon.com/images/I/41n0o65dSkL._SL160_.jpg)

![[新品]サカモトデイズ SAKAMOTO DAYS (1-27巻 最新刊) 全巻セット 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0034/m8880487562_01.jpg?_ex=128x128)

![Suicaのペンギンファンブック [ さかざきちはる ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8593/9784865938593_1_2.jpg?_ex=128x128)

![キングダム 79 (ヤングジャンプコミックス) [ 原 泰久 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1967/9784088941967_1_22.jpg?_ex=128x128)

![オレンジページ 2026年 8/2号増刊 [雑誌] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0869/4912210260869.jpg?_ex=128x128)

![ヤングジャンプ 2026 No.25 【電子書籍】[ ヤングジャンプ編集部 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7354/2000020407354.jpg?_ex=128x128)

![片田舎のおっさん、剣聖になる〜ただの田舎の剣術師範だったのに、大成した弟子たちが俺を放ってくれない件〜 9 【電子書籍】[ 佐賀崎しげる ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/3026/2000020673026.jpg?_ex=128x128)

![引きこもり令嬢は皇妃になんてなりたくない!〜強面皇帝の溺愛が駄々漏れで困ります〜5巻 【電子書籍】[ 直江亜季子 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2291/2000020632291.jpg?_ex=128x128)