福田昭のセミコン業界最前線

Optaneメモリの挑戦と挫折。【第1部】華麗なるデビューと徹底した秘密主義

2022年8月26日 07:13

Intelが「Optane」メモリ事業を段階的に縮小すると、2022年7月28日(米国時間)に開催された「2022年第2四半期(4月~6月期)」の決算発表において明らかにした。

「Optane」は、IntelとMicron Technologyが2015年に共同開発した大容量不揮発性メモリ技術「3D XPoint(スリーディー・クロスポイント)」のIntel製品ブランド名だ。

Intelは、これまでメモリモジュール製品「Optane DC Persistent Memory(Optane DC PM)」シリーズ、高速ストレージ製品「Optane DC SSD」および「Optane SSD」シリーズ、OptaneメモリとQLC NANDフラッシュメモリを混載したストレージ製品「Optane DC Memory」シリーズなどを市場に投入してきた。

Micron Technology(以降はMicronと表記)は高速ストレージ製品「X100」を2019年10月にサンプル出荷したものの、本格的な商用化には至らなかった。Micronは昨年3月に「3D XPointメモリ」の開発を休止するとともに、製造拠点を売却すると公式に表明している。

そしてIntelによる「段階的縮小」への決断に至る。2015年7月28日に「NANDフラッシュメモリ以降、25年ぶりの革新的なメモリ」と両社が謳って技術開発を華々しく発表してから、ちょうど7年後の2022年7月28日に、Intelによって事実上の開発休止がアナウンスされたことになる。

そこで本コラムでは2015年7月から2022年7月までの7年間に、IntelとMicronが「3D XPointメモリ」とどのように関わってきたかを数回で振り返る。今回は2015年7月から2017年8月までの主な出来事を取り上げる。なお次回以降では期間の重複があるので、あらかじめご了承されたい。

平面(2次元)では最も高密度なクロスポイント構造

3D XPointメモリ技術は、メモリセルアレイにクロスポイント構造を採用することと、メモリセルアレイを3次元積層することを特徴とする。

半導体メモリの技術開発コミュニティでは、クロスポイント構造のメモリを3次元化して記憶容量を2倍以上に高めるアイデアそのものは、2015年7月当時もそれほどめずらしくはなかった。

クロスポイント構造(クロスバー構造とも呼ぶ)とは、将棋盤やチェス盤などの行列(2次元マトリクス)状にメモリセルを物理的にレイアウトした構造を指す。

メモリセルアレイは論理的には通常、行列(2次元マトリクス)状をしている。行アドレスと列アドレスを指定することによって1個のメモリセルを選択する。ただし物理的には通常、将棋盤のような2次元マトリクス状のレイアウトは極めて難しい。半導体メモリのセルは少なくとも、1個のトランジスタ(セル選択と記憶を兼ねるトランジスタ)を必要とするからだ。

トランジスタ(MOS FET)は3端子素子なので、行アドレス線(ワード線)と列アドレス線(ビット線)のほかにもう1本、配線(接地線あるいはプレート線)が必要になる。平面の行列状レイアウトでは、3本目の配線を配置する余地がない(厳密には3本目の配線を基板に埋め込めるが、セルトランジスタの間隔を広げなければならない)。

クロスポイント構造では、平行なワード線群と平行なビット線群を直交するように配置し、ワード線とビット線の交差領域に2端子素子のセル選択素子と記憶素子を縦に積んで埋め込む。3D NANDフラッシュを除くと、原理的にはメモリセルを最も小さくできる。設計ルール(F)の2乗(F2)を基準にすると、メモリセルの面積は「F2の4倍」になる。

ちなみにDRAMのメモリセルは「F2の6倍あるいは8倍」であり、クロスポイント構造に比べると1.5倍~2倍の大きさがある。

セルアレイの3次元積層が比較的容易なクロスポイント構造

クロスポイント構造には、メモリセルアレイの3次元積層による大容量化が比較的容易だという特徴もある。

例えば2層構造にすると、メモリの記憶容量は2倍になる。4層構造にすると当然ながら記憶容量は4倍に増える。垂直にメモリセルをつなげる構造の3D NAND技術に比べ、3次元クロスポイントは製造の難度は低いと考えられていた。

IntelとMicronが共同開発した3D XPointメモリ技術に戻ろう。2015年7月に発表した3D XPointメモリ技術は後に「第1世代」と呼ばれるようになる。第1世代品では、1層が64Gbitのメモリセルアレイを2つ、積み重ねた。128GbitとDRAMよりもはるかに多くのデータを1枚のシリコンダイに収容してみせた。

さらに、スイッチング動作が高速かつ書き換えサイクル寿命が長いセル選択素子と記憶素子を開発した。この結果、NANDフラッシュメモリよりも大幅に短い書き込み時間と大幅に長い書き換えサイクル寿命を達成したとする。

アイデアは元からあるというものの、ここまで大容量かつ高性能な不揮発性メモリを商品化した事例はなかった。「革新的」との表現は製品としては適切に見える。

一方で3D XPointメモリ技術には、「DRAMに比べると読み書きの速度は遅く、読み出し速度はNANDフラッシュメモリとあまり変わらない」、「DRAMに比べると書き換えサイクル寿命が短い」、「3D NANDフラッシュメモリに比べると記憶密度が低い」といった短所がある。

もちろんこれらの短所をIntelとMicronは承知しており、メモリ階層ではDRAMとNANDフラッシュの間に3D XPointメモリを位置付けていた。DRAM階層とNANDフラッシュメモリ階層(SSD階層)の間には性能と記憶密度に極めて大きな開き(ギャップ)があり、このギャップを埋めるメモリあるいはストレージには、市場機会が十分にあると見込んでいた。

大容量メモリ、高速SSD、キャッシュの開発を予定

Intelは当初から、3D XPointメモリ技術によって3種類の応用製品を開発することを言明していた。大容量メモリ、高速SSD、キャッシュである。製品ブランドは「Optane」と名付けた。そして実際にこれらすべての応用製品を開発し、商品化してきた。

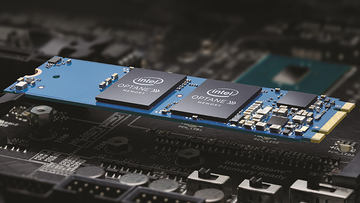

2017年4月24日にIntelは、HDDキャッシュ「Optane Memory Series」を一般消費者向けに発売した。

記憶容量は16GBと32GBであり、フォームファクタがM.2 2280のボードに1個(16GB品)あるいは2個(32GB品)の第1世代Optaneメモリを搭載していた。一般消費者向け製品を発売したことは、重要な意味を持つ。誰でも製品を入手して、分解できる。設備があれば、Optaneメモリの中身を探れる。

シリコンダイの解析サービス企業がOptaneメモリの詳細を公表

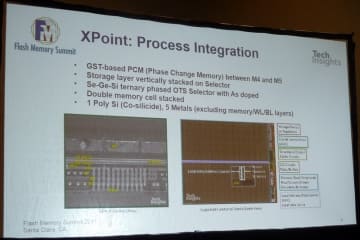

実際にOptaneメモリの中身を探ったのは、シリコンダイの解析サービス企業として半導体業界では良く知られているTechInsightsである。

同社が「Optane Memory Series」の16GB品を入手し、搭載している3D XPointメモリダイを分析した。TechInsightsは分析の結果を2017年8月にイベント「フラッシュメモリサミット(FMS : Flash Memory Summit)」で発表した

この発表には重要な意義があった。その背景にはIntelとMicronが技術の詳細をほとんど公表しなかったことがある。徹底した秘密主義が現在に至るまで貫かれた。

3D XPointメモリは単体メモリの販売がなく、モジュールやSSDなどの応用製品として販売された。応用製品はメモリのほかにコントローラを載せているので、メモリ単体の性能は隠された状態になる。

現在すなわち3D XPointメモリ開発の縮小が決まった時点においても、IntelとMicronは製造技術や回路技術などの詳細を公表していない。

公表されているのは第1世代の3D XPointメモリ技術(2層の3次元クロスポイント構造)によって記憶容量が128Gbitのシリコンダイを開発したこと、メモリセルは記憶素子とセル選択素子(セレクタ)を垂直に積層した構造であること、シリコンダイとウェハを撮影した写真、試作したSSDの性能をNANDフラッシュのSSDと比較した結果、それから第2世代の3D XPointメモリ技術の概要(4層のメモリセルアレイであること)、くらいだろう。

逆に、以下のような詳細が「公式には」不明なままだ。設計ルール(製造技術ノード)、記憶素子の原理と材料、セレクタの原理と材料、メモリセルの電極材料、メモリセルの面積(あるいは寸法)、シリコンダイの面積(あるいは寸法)、記憶密度、メモリセルアレイの面積効率(シリコンダイ全体に占めるメモリセルアレイの割合)、データ保持期間、書き換えサイクル寿命、シリコンダイのレイアウト(フロアプラン)、シリコンダイのメモリセルアレイと周辺回路の構造、読み出しアクセス時間、書き込みアクセス時間、消費電力(待機時および動作時)、などである。

相変化の記憶素子とOTSのセレクタでメモリセルを構成

TechInsightsの解析によって明らかになった技術は少なくない。設計ルール(技術ノード)は20nmのCMOSロジック技術(ロジックの配線技術は1層多結晶シリコン配線と5層金属配線(4層が銅、1層がアルミニウム)である。

メモリセルは上からトップ電極、相変化メモリ(PCM)の記憶素子、中間電極、OTS(Ovonic Threshold Switch、オボニックスレッショルドスイッチ)のセレクタ、ボトム電極の5層構造。

メモリセルアレイは試作シリコンダイと同じ2層のクロスポイント構造(ワード線(トップ)群/メモリセルアレイ/ビット線群/メモリセルアレイ/ワード線(ボトム)群)である。

応用製品「Optane Memory M10」に搭載したチップの記憶容量は試作シリコンダイと同じ128Gbit(16GB)だった。パッケージはBGAタイプ(81パッド)で大きさは18.0×14.0mm、シリコンダイの大きさは16.16×12.78mm(206.5平方mm)である。

クロスポイント構造のメモリセルアレイは、第4層金属配線と第5層金属配線の間に作り込んだ。メモリセルアレイ直下の基板には周辺回路が形成してあり、シリコンダイ面積の拡大を抑えようとしている(ただし実際のシリコンダイ面積は上述のように200平方mmを超えており、半導体メモリとしては巨大である)。

リソグラフィにはArF液浸露光技術を採用し、メモリセルアレイ部分(ワード線とビット線)はダブルパターニング(SADP)技術を追加した。メモリセル面積は0.0015平方μmである。

記憶素子とセレクタの材料組成も明らかになった。記憶素子である相変化メモリは、ゲルマニウム(Ge)(0.12 : 数値は組成比)、アンチモン(Sb)(0.29)、テルル(Te)(0.54)の合金に微量のシリコン(Si)(0.05)を加えたカルコゲナイド合金で、相変化メモリとして標準的なGST(Ge2Sb2Te5)合金とは組成がなり異なる。残念ながら、組成の違いがどのような意味を持つのかは不明だった。

セレクタであるOTSは、セレン(Se)(0.44)、ヒ素(As)(0.29)、ゲルマニウム(Ge)(0.1)、シリコン(0.17)のカルコゲナイド合金である。セレクタの候補技術はいくつもあり、その中でOTSはオンとオフの境界となるしきい電圧(Vth)を適切な値にしやすいとされる。

サーバー向けと一般向けのSSD、一般向けのHDDキャッシュを市場に投入

2017年はIntelが「Optane」ブランドの3D XPointメモリ応用品を相次いで製品化した年だった。製品開発を積極的に進め、Optaneブランドの普及を図った時期だとも言える。

2017年3月19日にはサーバー向け高速SSD「Optane SSD DC P4800X」の特定顧客向け出荷を始めた。

記憶容量は375GBとかなり大きく、当時としてはNANDフラッシュのSSDとあまり変わらない。同年4月24日には前述のように一般向けHDDキャッシュ「Optane Memory Series」を発売した。記憶容量は16GBと32GBで、キャッシュとしては大容量だ。

同年10月27日には、一般向け高速SSD「Optane SSD 900P」を発表する。記憶容量は480GB/280GB/240GBで、サーバー向けSSDと同程度の容量を提供した。

2017年末の時点では、Intelが2016年4月に開発を明らかにした応用品の中で「大容量メモリ」はまだ登場していない。またIntelの共同開発相手であるMicronはSSDを試作したものの、製品はまだ発表していない。Intelの積極さとMicronの消極さが浮き彫りになりつつある。その背景と2018年以降の出来事については、次回でご説明したい。

![【Amazon.co.jp限定】 伊藤園 磨かれて、澄みきった日本の水 2L 8本 ラベルレス [ ケース ] [ 水 ] [ 軟水 ] [ ペットボトル ] [ 箱買い ] [ ストック ] [ 水分補給 ] 製品画像:3位](https://m.media-amazon.com/images/I/41n0o65dSkL._SL160_.jpg)

ThinkPad L13 GEN2 20VJS33K00 製品画像:14位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-bomber-shop/cabinet/mastertool87/251051002293800.jpg?_ex=128x128)

![内視鏡下鼻副鼻腔・頭蓋底手術 [手術動画・3DCT画像データDVD-ROM付] 第2版 CT読影と基本手技 [ 中川 隆之 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8393/9784260038393.jpg?_ex=128x128)

![盾の勇者の成り上がり 30 【電子書籍】[ 藍屋球 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7729/2000020477729.jpg?_ex=128x128)

![ゴールデンカムイ 全巻セット(1-31巻) (ヤングジャンプコミックス) [ 野田サトル ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7713/2100013057713.jpg?_ex=128x128)

![チャイロイコグマの10th Anniversary BOOK (生活シリーズ) [ サンエックス ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5606/9784391645606.jpg?_ex=128x128)

![テレビマガジン特別編集 仮面ライダー 昭和46年~48年 講談社所蔵写真集 究極 [ 講談社 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1309/9784065401309_1_3.jpg?_ex=128x128)

![頭頸部の臨床画像診断学(改訂第4版) [ 尾尻博也 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6610/9784524226610.jpg?_ex=128x128)

![ヤングジャンプ 2026 No.25 【電子書籍】[ ヤングジャンプ編集部 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7354/2000020407354.jpg?_ex=128x128)