福田昭のセミコン業界最前線

20TBのSSD、2028年には300ドル前後に。その鍵は?

2024年5月24日 09:35

過去2番目に多い参加登録者を集めたソウル開催

半導体メモリ技術の研究開発に関する国際学会「国際メモリワークショップ(IMW 2024))」が、韓国ソウル特別市で5月12日~15日(現地時間)に開催された。最終日の技術講演会の最後には、チェアパーソンによる恒例の閉会挨拶が実施された。

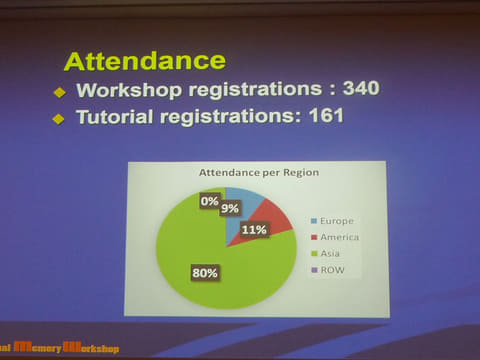

閉会挨拶では参加登録者数と、次回の開催地を公表することが恒例となっている。参加登録者数は340名で、前年(米国モントレー開催)の158名から2倍強と大幅に増えた。過去最高の人数を集めたのは2018年の京都開催で、このときは345名だった。今回のソウル開催では過去最高に近い参加者を集めたことになる。

参加登録者を地域別にみると、アジア(日本を含む)が80%と大半を占めた。米州は11%、欧州は9%である。2018年の京都開催ではアジアが74%、米州が18%、欧州が8%だった。6年前と比べて米州(そのほとんどは北米とみられる)の割合が減少し、アジアの割合が増加したことが分かる。チュートリアルの参加者は161名で、こちらも前年の74名から2倍強に増えた。

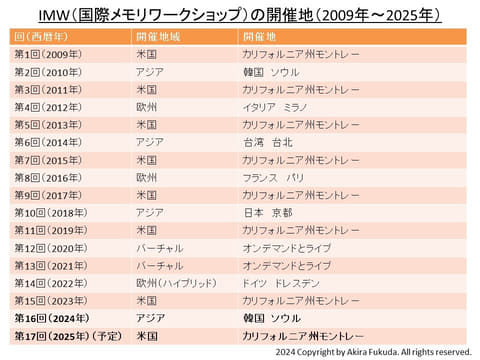

過去、国際メモリワークショップは初回(2009年)の米国から、アジア、米国、欧州、米国、アジア、米国という順番で開催されてきた。隔年で米国開催、隔年でアジアまたは欧州で開催、という順序である。前年は米国開催、今年はアジア開催だったので、次回は米国開催となる。

100Gbit/平方mmの記憶密度を2027年に達成へ

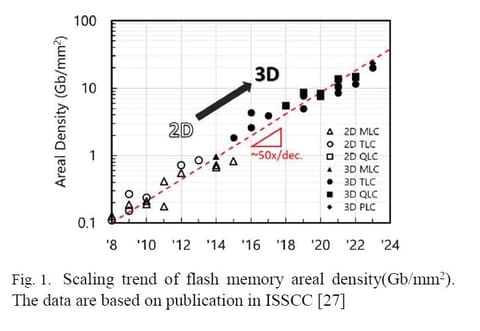

ここからは技術講演会(テクニカルカンファレンス)の注目講演を紹介しよう。初日の基調講演では、キオクシアが3D NANDフラッシュメモリの記憶密度をさらに高める技術と課題を展望した(講演番号および論文番号1.3)。記憶密度の向上に対して非常に積極的な内容だったので、講演および論文の概要をご報告したい。

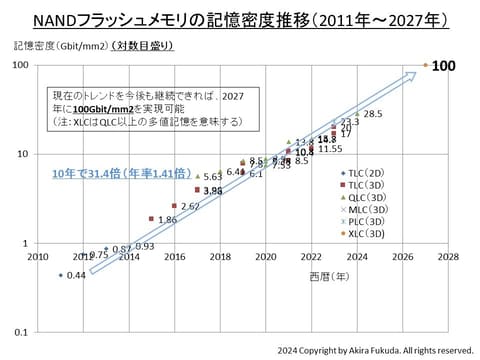

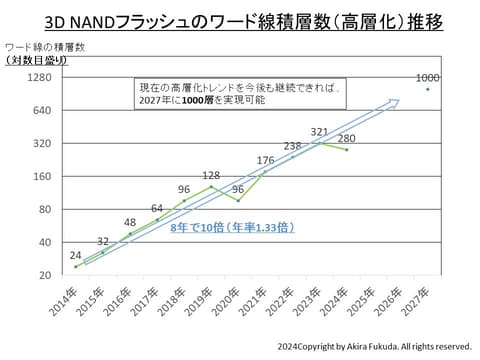

将来の重要なポイントとなる年次は2027年、今から約3年後だとする。記憶密度は100Gbit/平方mm、ワード線の積層数(メモリセルの積層数)は1,000層に達するとキオクシアは予測する。最先端半導体回路技術の国際学会として知られるISSCCの発表を基点にすると、記憶密度と積層数はいずれも、2023年~2024年の3倍を超える。

100Gbit/平方mmの記憶密度は、シリコンダイではどの程度の記憶容量を意味するのだろうか。仮にシリコンダイ面積を64平方mm(量産すると原理的には十分安価になる面積)とすると、シリコンダイの記憶容量は6.4Tbit(800GB)となる。8枚のシリコンダイを積層したパッケージの記憶容量は6,400GB、4個のパッケージを搭載したフラッシュストレージの記憶容量は25.6TBに達する。

2028年には20TBのSSDを300ドル前後に提供可能に

このストレージを記憶容量20TB(5.6TBは予備領域)のSSD製品として2028年に販売した場合、コストはどのくらいになるだろうか。

シリコンダイは合計で32枚なので、1枚の製造コストを2.5ドルとやや高めに見積もると、合計で80ドルとなる。パッケージコスト、プリント基板コスト、実装コスト、SSDコントローラのコスト、筐体のコスト、コネクタのコストなどを加えると、合計で120ドル~150ドルと推定する(コストに幅があるのは、主にインターフェイスの違いによるもの)。販売価格は250ドル~350ドルと見積もれる。

ちなみに記憶容量20TBの3.5インチ型HDD製品は米国Amazonだと400ドル前後で販売されている。3年後もHDDが同じ価格とは限らないが、4年後の20TB SSDは十分に競争力を備えていると言えそうだ。

100Gbit/平方mmと同時期に1,000層の「高層化」を目指す

「2027年に100Gbit/平方mm」を具現化するときに大きく寄与するのは、ワード線積層数の増加、すなわち「高層化」だ。同じ2027年に、ワード線積層数を1,000層に高層化するとの予測をキオクシアは示していた。

昨年12月に開催された半導体デバイス・プロセス技術の国際会議IEDMで、NANDフラッシュメモリ最大手のSamsung Electronics(以降はSamsung)は、招待講演で「2030年に1,000層」との予測を述べている。キオクシアの予測、あるいは開発目標は、Samsungと比べて3年も早い。

2014年から2024年まで、国際学会ISSCCで発表された3D NANDフラッシュ(シリコンダイレベル)のワード線積層数は、8年で10倍(年率1.33倍)の割合で増加してきた。この増加ペースを今後も維持できれば、「2027年で1,000層」は不可能ではない。

メモリセルアレイの高層化を阻む要因とその対策

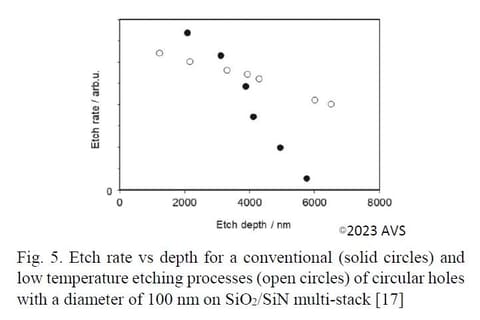

もちろん、ワード線の積層数は単純に増やせるわけではない。まず、積層したワード線を貫通するチャンネルホール(チャンネル孔)の形成が難しくなる。1,000層をいくつかのスタック(ティアとも呼ぶ)に分割するものの、直径0.1μmで深さ5μm以上、すなわちアスペクト比(AR)で50を超えるチャンネルホールがごく普通に出現する。

こういった高いARのエッチング(HARC:High Aspect Ratio Contactエッチング)は従来の反応性イオンエッチング(RIE:Reactive Ion Etching)だと、孔が深くなるにつれてエッチング速度が急激に低下する。そこで深い孔には、深さに対するエッチング速度の低下が緩やかな低温RIEあるいは低温エッチングを活用する。

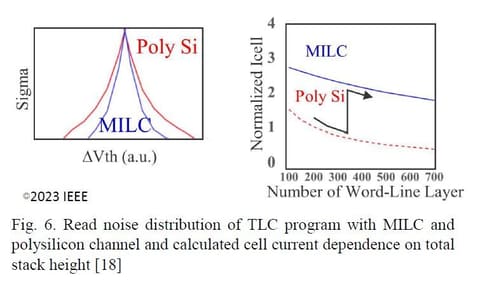

さらに、チャンネルホールの深さ(長さ)の増加はチャンネル抵抗と信号雑音の増大をもたらす。そこでチャンネル材料を現在の多結晶シリコン(ポリシリコン)から、単結晶シリコンに変更することが考えられている。

厳密には変更ではなく、多結晶シリコンあるいはアモルファスシリコンのチャンネルを形成してから熱処理によって単結晶化する。この技術は「MILC(Metal Induced Lateral Crystallization)」と呼ばれる。

ワード線の積層数が300層~400層になると従来の多結晶シリコンではセル電流の低下が厳しくなる。ここでMILCによる単結晶シリコンチャンネルに切り換えると、セル電流が2倍強に上昇することが見込める。

高層化による記憶密度向上を妨げる要因とその対策

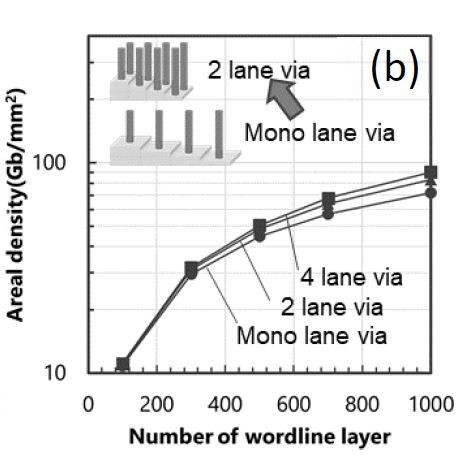

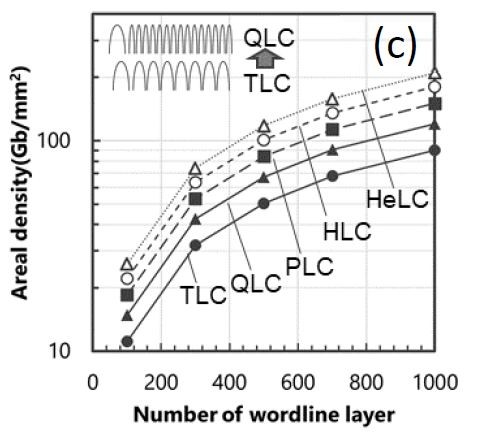

ワード線の積層数を増やしても、シリコンダイの記憶密度が向上するとは限らない。ワード線から垂直方向に電極を引き出すための領域「ステアケース(階段)」が増加するからだ。ステアケースの面積が拡大することにより、300層を超えるとワード線の積層数を増やしたときの記憶密度の向上ペースが鈍化する。

TLC(3bit/セル)方式のメモリセルアレイだと、1,000層になっても記憶密度は目標の100Gbit/平方mmに達せず、70Gbit/平方mmにとどまってしまう。そこで2個さらには4個の垂直電極をまとめることでステアケースの領域を削減し、記憶密度を上げる。後者の工夫によって、1,000層の記憶密度は90Gbit/平方mmと目標にかなり近づく。

ステアケース領域を削減する工夫に加え、多値記憶方式をTLC(3bit/セル)方式からQLC(4bit/セル)方式に変更すると、1,000層の記憶密度は目標の100Gbit/平方mmを超える。1個のセルが記憶できるデータを増やすことが、記憶密度の向上にはきわめて重要になる。

ワード線の金属はタングステンからモリブデンへ

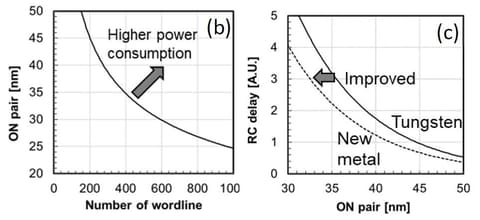

ワード線の積層数を増加させるときの課題としてはほかに、ワード線抵抗および容量の増加による遅延時間の増加がある。ワード線の積層数を増やすときには、並行してワード線の積層ピッチをなるべく縮めたい。チャンネルホールのエッチング深さを短く抑えるとともに、消費電力の増加を緩和するためである。

ワード線の積層ピッチはワード線金属層の厚みと絶縁層の厚みの合計値であり、高層化とともに金属層と絶縁層を薄くする。するとワード線抵抗が増加するとともに、ワード線の静電容量が増加する。こうなるとメモリの動作速度が下がってしまう。

対策として考えられているのが、ワード線金属材料の変更である。現在のワード線金属材料には、タングステン(W)が標準的に使われている。将来は材料をモリブデン(Mo)に変更して抵抗値を下げ、遅延時間を短縮する、あるいは遅延時間の増大を抑える。

3D NANDフラッシュメモリの記憶密度は過去、さまざまな工夫を重ねながら一定のペースで向上してきた。ここにきて従来技術の改良では、今後の継続的な密度向上はかなり難しいことが明らかになっている。新たな要素技術を開発し、3D NANDフラッシュを構成するフレームワークの中に埋め込んでいくことが求められる。

![■air-J NEW カラビナコイルストラップ 太型ロングタイプBK〔品番:ASR10BK〕【3928897:0】[店頭受取不可] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/hcvalor-eshop/cabinet/trusco/3928/trusco-3928897.jpg?_ex=128x128)

![北北西に曇と往け 続の1 [ 入江 亜季 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8024/9784911278024_1_56.jpg?_ex=128x128)

![JISハンドブック 59 製図(2025) [ 日本規格協会 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1488/9784542191488_1_3.jpg?_ex=128x128)

![【特典】メロとタビ(【初回限定シールB付】) [ まめきちまめこ ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6482/2100014936482_1_2.jpg?_ex=128x128)

![糖毒脳 いつまでも「冴えた頭」でいるために知っておきたいこと [ 下村 健寿 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1757/9784478121757_1_2.jpg?_ex=128x128)

![駆動システムの高性能・高効率化技術を完全習得 モーター・インバーター制御 【電子書籍】[ 高橋 久 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0328/2000019200328.jpg?_ex=128x128)

![CBT対応版 QC検定3級 対策問題集 2026年版 [ 仁科 健 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5384/9784542505384_1_4.jpg?_ex=128x128)

![リンネル 2026年 7月号 [雑誌] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0769/4912193070769_1_2.jpg?_ex=128x128)