福田昭のセミコン業界最前線

高性能半導体の実現に不可欠となった先進パッケージング技術

2024年5月29日 09:50

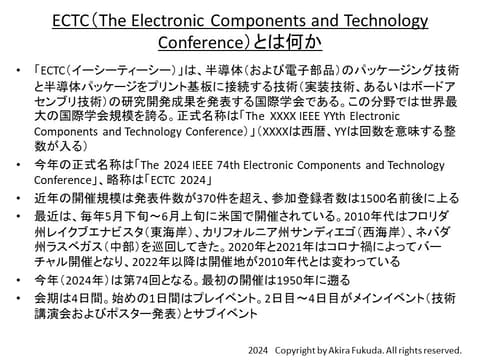

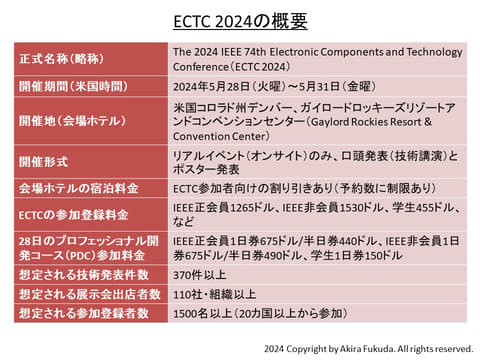

半導体(および電子部品)のパッケージング技術と半導体パッケージをプリント基板に接続する技術(実装技術、あるいはボードアセンブリ技術)の研究開発成果を発表する世界最大の国際学会「The 2024 IEEE 74th Electronic Components and Technology Conference」(略称は「ECTC 2024」)が2024年5月28日に米国コロラド州デンバーのガイロードロッキーズリゾートアンドコンベンションセンター(Gaylord Rockies Resort & Convention Center)で始まった。

ECTCは、半導体パッケージング技術と実装技術の研究開発コミュニティでは、最も良く知られた国際学会である。特に最近の10年は研究活動の活発化を反映し、規模が拡大しつつある。ここ5年の開催規模は発表件数が370件強、参加登録者数は1,500名前後に上る。

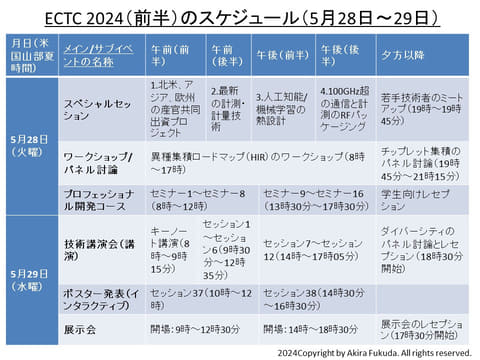

ECTCの会期は4日間。始めの1日間はプレイベント。2日目~4日目がメインイベント(技術講演会およびポスター発表)とサブイベントというスケジュールとなっている。今年(2024年)のECTCすなわち「ECTC 2024」は、5月28日の初日がプレイベント、5月29日~31日がメインイベント(技術講演会)である。

メインイベント前日には技術講座やワークショップ、パネル討論などを用意

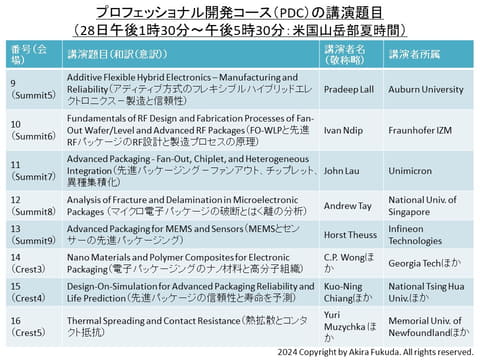

国際学会の技術講演会前日に実施するサブイベントと言えば、「技術講座(チュートリアル)」だろう。国際学会の収支健全化に寄与する重要な収入源でもある。ECTCでも、「プロフェッショナル開発コース(PDC)」と呼ぶ技術講座を予定する。

ECTCではさらに、「スペシャルセッション」と呼ぶ、話題のテーマに関するワークショップや討論会などのサブイベント群を28日に設けている。

28日はプレイベントの技術講座とスペシャルセッションを開催

28日の「プロフェッショナル開発コース」では、午前と午後にそれぞれ8つの講座を用意した。8つの講座は並行して実施するので、午前と午後にそれぞれ1本の講座しか選べない。悩ましいところだ。

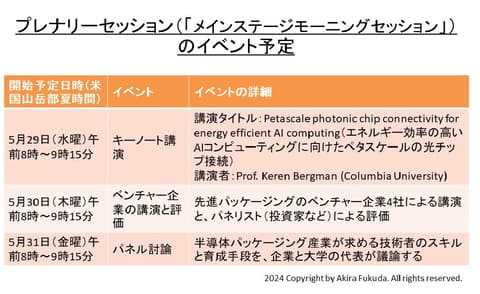

少し変わっているのが「スペシャルセッション」だ。28日のワークショップやパネル討論会などのほか、29日~31日の最初に実施する全体イベント(「メインステージモーニングセッション」と呼んでいる)と29日夜のパネル討論もスペシャルセッションに含まれる。

技術講演会の3日間はすべて全体セッションから始まる

5月29日~31日の技術講演会は、全体セッション(プレナリーセッション)である「メインステージモーニングセッション」(午前8時~9時15分)から1日が始まる。29日は基調講演、30日は4社のベンチャー企業によるプレゼンテーションと投資家による評価(パネル討論)、31日は人材育成に関するパネル討論会を予定する。

ウェアラブル向けのマルチチップ内蔵用FO-PLP技術

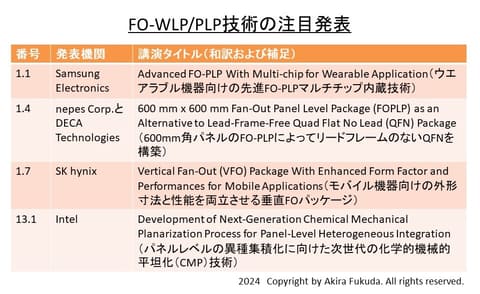

ここからは、技術講演会の注目発表を紹介していこう。発表テーマは便宜上、「FO-WLP/PLP(Fan-Out Wafer Level Package/Panel Level Package)」、「2.5Dのパッケージ技術(CoWoSなど)」、「チップレット技術」、「ガラス基板」、「ハイブリッド接合」に分けた。あらかじめご了承されたい。

「FO-WLP/PLP」技術では、Samsung Electronics(以降はSamsungと表記)がウェアラブル機器向けにマルチチップ搭載を前提とする先進FO-PLP技術を発表する(発表番号1.1)。nepes Corp.とDECA Technologiesは、600mm角パネルのFO-PLPによってリードフレームのないQFNパッケージを構築する技術を共同開発した(同1.4)。SK hynixは、モバイル機器向けの外形寸法と性能を両立させる垂直FO(Fan-Out)パッケージを発表する(同1.7)。

このほかIntelが、パネルレベルの異種集積化に向けた次世代の化学的機械的平坦化(CMP)技術を開発した(発表番号13.1)。

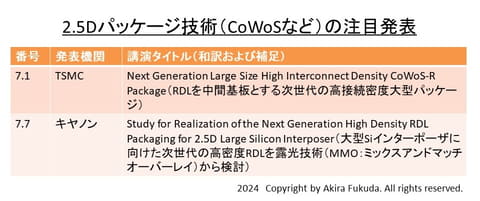

RDLを中間基板とする次世代の高密度パッケージ「CoWoS-R」

「2.5Dのパッケージ技術(CoWoSなど)」では、TSMCがRDL(再配線層)を中間基板とする次世代の高接続密度大型パッケージ「CoWoS-R」を発表する(発表番号7.1)。キヤノンは、大型Siインターポーザに向けた次世代の高密度RDLを露光技術(MMO:ミックスアンドマッチオーバーレイ)から検討した結果を述べる(同7.7)。

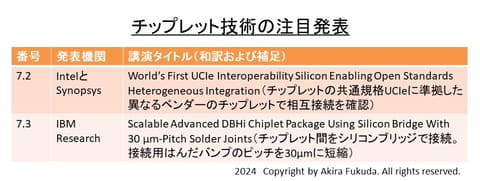

「チップレット技術」では、IntelとSynopsysがチップレットの共通規格「UCIe」に準拠した異なるベンダーのチップレットで相互接続を共同で確認してみせた(発表番号7.2)。開発コード名「Pike Creak」に相当する成果だとみられる。IBM Researchは、複数のチップレット間をシリコンブリッジで接続する技術で、接続用はんだバンプのピッチを30μmと短くしてみせた(同7.3)。

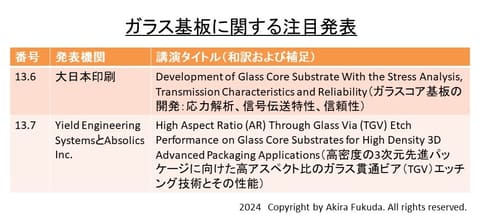

「ガラス基板」技術では、大日本印刷が同社が開発したガラスコア基板の応力解析、信号伝送特性、信頼性などを評価した結果を報告する(発表番号13.6)。Yield Engineering SystemsとAbsolicsは、高密度の3次元先進パッケージに向けた高アスペクト比のガラス貫通ビア(TGV)エッチング技術を開発した(同13.7)。

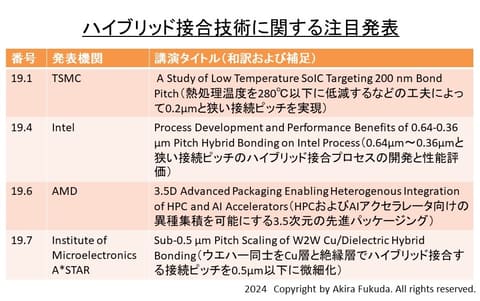

接続ピッチをサブミクロンに微細化したハイブリッド接合

「ハイブリッド接合」技術では、接続ピッチを1μm以下に狭くした技術の発表が相次ぐ。TSMCは、熱処理温度を280℃以下に低減するなどの工夫によって0.2μmと狭い接続ピッチを実現するハイブリッド接合技術を発表する(発表番号19.1)。

Intelは、0.64μm~0.36μmと狭い接続ピッチのハイブリッド接合プロセスを開発した(同19.4)。AMDは、HPCおよびAIアクセラレータ向けに異種ダイの集積を可能にする3.5次元の先進パッケージング技術を報告する(同19.6)。Institute of Microelectronics A*STARは、接続ピッチを0.5μm以下に微細化したウェハ間Cu層/絶縁層接続のハイブリッド接合技術を開発した(同19.7)。

このほかにも興味深い発表が少なくない。詳細は現地取材によるレポートでお届けする予定である。ご期待されたい。

![ASUS(エイスース) VG249QM5A ゲーミングモニター TUF Gaming ブラック [23.8型 /フルHD(1920×1080) /ワイド /240Hz] VG249QM5A 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/dtc/cabinet/mc5108/2554451.jpg?_ex=128x128)

![I-O DATA|アイ・オー・データ ゲーミングモニター GigaCrysta 3年保証 ブラック KH-GDQ271JA [27型 /WQHD(2560×1440) /ワイド /180Hz] 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/8883/00000012108334_a01.jpg?_ex=128x128)

![GOAT Summer 2026 [ 宮島 未奈 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1215/9784098021215_1_2.jpg?_ex=128x128)

![【楽天ブックス限定特典】すしらーめん りく1st写真集 さいごのふたり(限定カバー) [ すしらーめん りく ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9547/2100014909547_1_2.jpg?_ex=128x128)

![ダンダダン 23【電子書籍】[ 龍幸伸 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0120/2000019910120.jpg?_ex=128x128)

![當真あみ ファースト写真集 Ami[本/雑誌] / 屋山和樹/撮影 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/neowing-r/cabinet/item_img_1974/neobk-3058780.jpg?_ex=128x128)

![悲劇のヒロインぶる妹のせいで婚約破棄したのですが、何故か正義感の強い王太子に絡まれるようになりました 5 【電子書籍】[ 真綿マスケ ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0575/2000020430575.jpg?_ex=128x128)

![【電子版】ドラゴンエイジ 2026年6月号 【電子書籍】[ ドラゴンエイジ編集部 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7719/2000020567719.jpg?_ex=128x128)

![悪役令嬢転生おじさん(10) 【電子書籍】[ 上山道郎 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0539/2000020190539.jpg?_ex=128x128)

![Only Sense Online 23 ーオンリーセンス・オンラインー 【電子書籍】[ 羽仁 倉雲 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9038/2000020419038.jpg?_ex=128x128)

![辺境モブ貴族のウチに嫁いできた悪役令嬢が、めちゃくちゃできる良い嫁なんだが? 3 【電子書籍】[ tera ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9041/2000020419041.jpg?_ex=128x128)