笠原一輝のユビキタス情報局

「Intel 18A」はTSMCの2nmに追いつく秘策。Intelの未来がかかった新プロセスノードは何がすごいのか?

2024年2月26日 06:02

Intelは2月21日(現地時間)に、ファウンドリ(半導体受託製造)事業「Intel Foundry Services(IFS)」向けイベントとなる「Intel Foundry Direct Connect 2024」を、米国カリフォルニア州サンノゼ市にあるサンノゼ・コンベンションセンターにおいて開催した。

この中でIntelは、高NA EUVを初めて採用するIntel 14Aなどの新しい製造技術(プロセスノード)のロードマップを明らかにしたほか、新たなファウンドリ事業の顧客としてMicrosoftと契約したことなどを明らかにした。

だが、本当の意味でIntelにとって重要だったのは、詰めかけた潜在顧客に同社が2025年にIFSの顧客向けに提供を開始するプロセスノード「Intel 18A」の着実な進展をアピールできたことだ。というのも、この「Intel 18A」こそ、同社の自社事業や自社製品の今後を左右する重要なプロセスノードであるからだ。

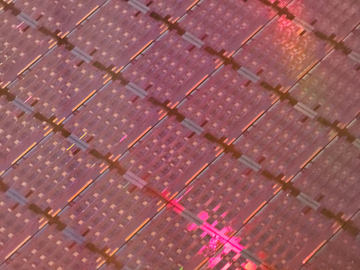

プロセスノードとは前工程でウェハを製造するときに使われる製造技術のこと

Intel 18AがIntelにとって、そしてIFSの顧客となるファブレス半導体メーカーにとって死活的に重要なのかを説明する前に、Intelのプロセスノードの戦略に関して復習しておこう。

半導体がどう製造されるのかは、以下の関連記事を参照してほしいが、簡単に言えば前工程でウェハ上に配線を作りトランジスタと呼ばれるスイッチを構成していく形になり、後工程では前工程で製造したウェハからチップに切り出して、それをパッケージに封入していくという形で製造されている。

プロセスノードとは、その前工程でトランジスタを構築していく際に活用される製造技術の世代のこと。トランジスタのゲート長と呼ばれるトランジスタのスイッチに相当するゲートの長さをもって世代を示している。

たとえば、22nmであればそのゲート長が22nm、14nmであればゲート長が14nmであることを示しており、そのゲート長が小さくなれば、トランジスタ自体のサイズが小さくなり(微細化と呼ばれる)、同じ面積に詰め込めるトランジスタ数が増えることになる。

その結果、トランジスタ数が増えるのに比例して概ね半導体の性能は向上する。そうした微細化を繰り返すことで、1つのチップに詰め込めるトランジスタ数が増えてきて、半導体の性能はずっと向上してきた、それが半導体産業の歴史だ。

それを象徴する言葉が、Intel創業者の1人である故ゴードン・ムーア氏が提唱した「ムーアの法則」だ。1~2年の間に製造技術を新しくしていくことが、経済的合理性があるというのがムーアの法則で、実際、過去数十年に渡って概ねそうした進化を遂げてきた(ここ数年はそこまでうまくいっていないが)。

そのプロセスノードだが、以前は名称とゲート長が一致していた。しかし、近年はそもそもゲート長と性能が比例しなくなってきている。

特に、Intelにとっては同じゲート長であっても、PPAC(Performance・Power・Area・Cost)という半導体産業で使われている指標で見ると、Intelの現行世代と他社の一世代先のノードがそんなに変わらないという状況が発生していた。

そこで、Intelは10nm世代の改良版世代から、ゲート長を名称にするのをやめて、他社(具体的にはTSMCとSamsung)の世代でどれに相当するのかをプロセスノード世代の名称にすることにしている。

10nm Enhanced SuperFinは他社の7nm相当という意味でIntel 7に、7nm世代は他社の4nm/3nm相当という意味でIntel 4/Intel 3という名称にしている。

そして、他社の2nmに相当するのがIntel 20AとIntel 18Aとなる。このIntel 20A/18AでIntelは2つの新しい技術を投入する。

1つはIntelがRibbonFET、業界ではGAA(Gate All Around)と呼んでいるゲートの形状が3Dから4Dに進化する、新しい形状のゲートを導入する(すでに他社は導入済み)。

もう1つはPowerViaと呼ばれるチップの底面に電源層を設けることで、チップに安定して電力を供給できる仕組みを導入する。これはIntelによる業界初の技術になる。

では、Intel 20AとIntel 18Aの違いは何かというと、基本的には同じゲート長、同じRibbonFETの構造になる。しかし、マイナーバージョンアップで性能は向上しているというものになる。

そもそもIntelにとってノードの定義は何かと問われたパット・ゲルシンガーCEOは、「ノードというのは性能の観点で概ね10%程度を超える向上があるものと定義している。それに対して5%程度の性能向上の場合には名称にPをつける形のマイナーバージョンアップという扱いにしている」と説明している。

つまり、性能向上が5%前後であれば「Intel 18A-P」のように後ろにPがつき、5%~10%程度であれば新しいノード名がつくということになる。

その定義を使うと、Intel 18AはIntel 20Aから10%程度の性能向上が見られるバージョンとなる。いずれも本年の末頃に製造開始とIntelは説明しており、それならIntel 20AをスキップしてIntel 18Aを使うというのが合理的な判断ということになるだろう。

Intel 18AはLunar Lake、Clearwater Forest、そしてDiamond Rapidsで利用

実際、Intelが自社製品に採用しているのはいずれもIntel 18Aのほうが、今のところIntel 20Aを利用した製品というのは見当たらないのが現状だ。

Intelが昨年の9月のInnovation 2023で動作させてみせたノートPC向けのLunar Lake、そして今回のイベントで初めて公開したClearwater Forest(Eコアだけから構成されているXeonの第2世代)という、25年に本格的に登場する製品はいずれもIntel 18Aを採用している。

さらに、実はIntelがまだ存在を公開していない製品もIntel 18Aベースだという。Intelは本年の前半に、第5世代Xeon Scalable Processor(開発コードネーム : Emerald Rapids)の後継としてGranite Rapidsを投入すると明らかにしている。

IntelはそのGranite Rapidsの後継製品をまだ明らかにしておらず、なんの公式発表もしていないが、情報筋によればDiamond Rapidsなるものを計画しているという。このDiamond Rapidsも、Intel 18Aで製造される見通しだと噂されている。

実はLunar Lakeにせよ、Diamond Rapidsともに、Intelにとっては戦略製品になる。この2製品ともなにがしかの新しいPコアのデザインが導入される。

その2つが同じPコアなのかは分からないが、1つだけ分かっていることは、どちらもIPC(1クロックで実行できる命令数、IPCが高ければ高いほど実行効率が増す)が大きく向上するということだ。

その向上したIPCを、電力効率を改善する方向に使うのがLunar Lakeで、性能を上げる方向に使うのがDiamond Rapidsということになる。言い換えれば、Lunar LakeはQualcommのSnapdragonキラーであり、Diamond RapidsはAMDのEPYCキラーというゲームチェンジャーの製品になると考えられている。

その戦略的な製品がいずれもIntel 18Aに基づいて製造される形になる。それだけでもIntel 18AがIntel(の製品部門)にとって非常に重要なプロセスノードであることが分かるだろう。

Intel 18Aがブレークスルーに。MicrosoftもIntel 18Aを選択

Intel 18Aは、IFSのファウンドリを利用する顧客にとっても重要なプロセスノードになる。というのも、IFSの新規顧客の多くは、このIntel 18A以降でIFSでの製造を開始することを計画しているからだ。

すでに述べた通り、IntelはIntel 20Aを他社の2nm、そしてIntel 18Aは他社の2nm改良版と位置づけている。現在TSMCは最先端ノードとして3nmを、Apple製品を製造するのに利用しており、まもなく2nmの量産出荷を行なうと考えられている。Intel 20A/18Aはその直接の競合ということになる。

TSMCの代替としてIFSを検討している顧客にとっては、Intel 18AはTSMCと価格交渉を行なう際のカードとしても使えるし、あるいはTSMCで生産するのに工場のラインが足りない場合には、IFSで検討するということも当然視野に入ってくる。

また、そもそもIntel 18AのほうがTSMCの2nmよりも優れていると思えば、思い切ってIFSに移ってくるということも可能だ。

その最大の代表例は、今回のIntel Foundry Direct Connect 2024で発表されたMicrosoftのIFS利用計画だ。Microsoftのサティヤ・ナデラCEOは基調講演でビデオ出演し、同社がIFSと契約してIntel 18Aを自社の半導体製造に活用すると明らかにしたことだ。

かつては「Wintel」だと揶揄されるほど密接なパートナーだとされてきた両者だが、実際のところはお互いにメリットがあることでしか協業しないという、実にドライな関係であることは業界の関係者はよく知っている。

そんなMicrosoftが、Intel 18Aを選んだのは、シンプルにMicrosoft自身にとってそのほうが、メリットがあると考えたからだろう。こうして早期に採用を明らかにすれば、当然大きな価格のディスカウントを期待できるし、たとえば急にボリュームが必要になったときに優先的に割り当ててもらえるなどの契約結ぶことも可能と思われる。そういうメリットがあると判断して、Microsoftは契約したと考えるのが妥当だ。

IFAの顧客にとってIntel 18Aが重要なのはそれだけではない。ファブレスの半導体メーカーが半導体を設計する時に必要になる、EDA(Electronic Design Automation)ツールを提供するツールベンダーも、軒並みIntel 18AからIFSのプロセスノードに対応することも見逃せない重要なポイントだ。

EDAを利用すると、たとえばTSMCのプロセスノード向けに設計したデータがあれば、それを活用してIFSのプロセスノードに落とし込むことが可能になる。しかし、従来EDAツールはIntelのプロセスノードには対応していなかった(外部には解放されていなかったから当然だが)ので、それは不可能だった。

しかし、今回Ansys、Cadence、Siemens、SynopsysといったEDAツールを提供する大手ベンダーがIntel 18Aへの対応を明らかにしている。これにより、TSMCやSamsungからIFSへ移行するのがより容易になると考えられる。

同時にIntelは、Intel 18A向けのIP(知的所有権)の選択肢も広げている。ここで言うIPとは、IFSの顧客がSoCを設計する時に、CPUのIP(たとえばArm CPUとかx86 CPU)、GPUのIP、PCI Expressコントローラ、USBコントローラなどが、IPベンダーから提供されて、それを組み合わせて設計するのが一般的だ。

これまでそうしたIPベンダーはTSMCとSamsungのプロセスノードにだけ最適化してきた(それしか選択肢がなかったので当たり前だが)が、SynopsysのようなPCI ExpressやUSBコントローラなどを提供するIPベンダーはIntel 18Aへの最適化を明らかにしているし、Intel Foundry Direct Connect 2024の基調講演にはArm CPUのIPデザインを提供するArmのレネ・ハスCEOがゲストとして呼ばれ、Arm CPUをIntel 18Aに最適化していくと強調している。

Intel 18Aだけでなく、EMIBやFoverosといった後工程の技術もIntelファウンドリの顧客が利用可能

すでに述べた通り、IntelはIntel 18Aにおいて製造技術でTSMCの2nmに追い付くことになり、さらにTSMCなどに先駆けて高NA EUVを導入するIntel 14Aで追い越すことを狙っている。

では、半導体ベンダーがIntel 18A世代でIFSを選択することによってプロセスノード以外にもたらされるメリットはあるのだろうか?

実はある。Intelは今回IFSを「世界初のシステム・ファウンドリ」であると定義し、それがTSMCやSamsungなどに対しての明快なメリットだと表現した。

具体的にはどういうことかというと、IFSではウェハを製造するだけでなく、Intelが世界中に構築している後工程の工場(アメリカのニューメキシコ州、マレーシアのペナン、コスタリカ、中国の成都、そして現在建設中のポーランド)を利用してパッケージへの組み立てまでを一気通貫に行なうことが可能なのだ。これに対して従来のファウンドリの場合は、基本的にはウェハの製造までで、後工程は外部の工場に委託されることが通例だ。

Intelの後工程の工場を使えるメリットは何かと言えば、Intelのパッケージング技術を活用できることだ。

IntelのPC/データセンター向けで利用されているFCBGAの2D/2.5D、EMIBやFoverosといった2.5D/3DのチップレットなどといったAdvanced Packagingと呼ばれる先端パッケージ技術を利用して、IFSの顧客がIntelの後工程の工場で生産することが可能になる。

すでに半導体産業は、単に前工程の性能だけでなく、チップレットなどのパッケージング技術も活用して、性能を上げていくという時代に突入している。そうした競争環境の中で、ファブレス半導体ベンダーにとっては、前工程だけでなく、後工程にも魅力的な技術を持つIFSが、従来のファウンドリに比べて魅力的に見えてもおかしくない。

そうした観点からも、IntelがIFSの成功に十分自信を持っており、30年までにファウンドリで第2位を目指すという目標が現実的な目標だと言っていいのではないだろうか。

![中古美品 フルHD 13.3インチ Fujitsu LIFEBOOK U9311/F / Windows11/ 第11世代Core i5-1145G7/ 16GB メモリ[ 8GBモデルも選択可 ]/ 爆速NVMe式256GB-SSD/ カメラ/ 無線Wi-Fi6/ Office付/ Win11ノートパソコン 中古パソコン 中古PC Windows10も対応可/ Win10 税込送料無料 製品画像:19位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-one/cabinet/11670319/11857449/11857984/fujitsu11-xxx-1.jpg?_ex=128x128)

![マウスコンピューター 15.6型 IPS方式 フルHD モバイルモニター iiyama ブラック P1671HSC-B1J [P1671HSCB1J]【RNH】 製品画像:13位](https://thumbnail.image.rakuten.co.jp/@0_mall/edion/cabinet/goods/ll/img_560/4948570127375_1.jpg?_ex=128x128)

![大人の科学マガジン BESTSELECTION07 小さな活版印刷機 [ 大人の科学マガジン編集部 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9501/9784057509501_1_3.jpg?_ex=128x128)

![学校では教えてくれない大切なこと 48 働くってどういうこと? 今の自分が未来をつくる [ 旺文社 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5480/9784010115480_1_2.jpg?_ex=128x128)

![殺人の門 下 新装版 (角川文庫) [ 東野 圭吾 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8752/9784041168752_1_13.jpg?_ex=128x128)

![公共建築工事標準仕様書 建築工事編(令和7年版) [ 国土交通省大臣官房官庁営繕部 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1175/9784938421175_1_2.jpg?_ex=128x128)

![公共建築改修工事標準仕様書(建築工事編)(令和7年版) [ 国土交通省大臣官房官庁営繕部 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2773/9784907762773_1_2.jpg?_ex=128x128)

![イヤーノート 2027 内科・外科編 [ 岡庭 豊 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9681/9784896329681_1_6.jpg?_ex=128x128)

![ViVi (ヴィヴィ) 2026年7・8月合併号 増刊 [雑誌] 表紙:JI-DF ver. 與那城奨、白岩瑠姫、河野純喜(JO1)、後藤威尊、佐野雄大、池崎理人(INI)付録:JI BLUE フォトアルバム 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0866/4912013800866_1_3.jpg?_ex=128x128)