ニュース

ファウンドリ第2位を目指す。Intelが14Aなどを製造技術の新ロードマップを公開

2024年2月22日 01:30

Intelは、2月21日(現地時間)に、同社初のファウンドリ(半導体受託生産)事業向けイベントとなる「Intel Foundry Direct Connect 2024」を、米国カリフォルニア州サンノゼ市にあるサンノゼ・コンベンションセンターにおいて開催している。

午前中に行なわれる基調講演には、Intelのパット・ゲルシンガーCEOが登壇し、米国商務長官 ジーナ・レモンド氏、Arm CEO レネ・ハス氏、Microsoft CEO サティヤ・ナデラ氏、OpenAI CEO サム・アルトマン氏など政界、IT業界のキーリーダーなどがゲストとして参加して開催されている。

この中でIntelは、2030年までにファウンドリビジネスで第2位を目指すという意欲的な目標を明らかにしたほか、従来から説明してきた「4年で5ノード」の意欲的なロードマップが順調に実現されていること、さらには業界で初めて高NA EUV(High-NA EUV)に対応したIntel 14Aを計画しているという新しいロードマップを公開した。

IDM 2.0の根幹となるのがIntel Foundry Service

Intelは2021年にパット・ゲルシンガー氏がCEOに復帰して以来、新しい戦略を次々と打ち出し、従来のような製品や製造技術がロードマップ通りに実現できないという状態からの脱却を図り、着々と新製品や製造技術などをロードマップ通りに投入するように変わっているが、その根幹となる戦略が「IDM 2.0」だ。

これは従来からのIntelの製造施設だけでなく、外部ファウンドリの製造施設も適宜利用しつつ、Intelの製造施設を外部に公開するというファウンドリビジネスを展開するという、IDM(垂直統合型半導体メーカーのこと)と、ファウンドリの良いところを組み合わせた新しい半導体メーカーへの脱却を目指す意欲的な戦略となる。

IDM 2.0戦略に基づいて始めたファウンドリ事業が、IFS(Intel Foundry Service)だ。従来Intelの製造施設は、Intelの製品部門(CCG=クライアントコンピューティング事業本部やDCAI=データセンター・AI事業本部など)だけに半導体を製造していた。しかし、IFSはその製造施設をIntelの製品部門と競合する他社に対して解放し、他社がデザインした製品の受託製造を行なう。

半導体産業は「規模の経済」と呼ばれ、生産数などが製造効率に大きな影響を与えるとされている。既にApple、AMD、NVIDIA、Qualcommなどの高性能半導体を製造するメーカーのほとんど全てを受託製造するTSMCと、Intel向けだけの製造を行なっているIntelの製造部門を比較すると、TSMCの方が規模で上回っているというのが現状で、それを覆す意味でも、Intel社内と外部の需要を組み合わせることでTSMCに規模で追い付き、将来的には追い越すというのがIDM 2.0の肝になる部分だ。

実際、NVIDIAのジェンスン・フアンCEOは昨年の5月末に行なわれたCOMPUTEX 2023でIFSのテストチップを評価していることを明らかにしているし、Qualcommも評価を行なっていることを明らかにしているなど、Intelの競合メーカーもIFSでの委託製造に前向きなコメントを残している。こうしたファブレス半導体ベンダーにとっては、TSMCに加えて、Intelという選択肢が出てきたことは、2社に競争してもらうことで製造コストが下がる、あるいは製造キャパシティを増やすという観点で歓迎すべき動きと言える。

また、Intel幹部も製品部門と競合するような製品がIFSで製造されても構わないとしているなど、Intel自身もIFSが重要な事業であると度々コメントしている。

今回のIFSで、Intelはファンダリビジネスにおいて、2030年までにTSMCについで業界2位になると意欲的な目標を設定したことを明らかにしている。現在ファンダリビジネスでは、1位は台湾のTSMC、2位が韓国のSamsung Electronicsとなっている。つまり、今回のIntelの2位宣言は、2030年までにSamsungを抜いて2位になるということを目標としてセットしたということになる。

Intel 14Aを投入など新しいプロセスノードロードマップを公開

こうした、IFSのビジネスを確実にするために、IntelはIDM 2.0を発表した時点で、トップベンダーのTSMCに比べて遅れていた製造技術(プロセスノード)の開発を加速してきた。2021年にIntelが発表した「4年で5ノード」という戦略では、Intel 7、Intel 4、Intel 3、Intel 20A、Intel 18Aという5世代のプロセスノードを投入するという意欲的なプランが明らかにされている。

そこから3年が過ぎ、2024年は最後の1年になったのだが、既に2023年までに3ノード(Intel 7、Intel 4、Intel 3)を製品として投入済みないしは製造開始を行なっており、目標の5世代のうち3世代までは完了している。

2024年には、Intel 20AとIntel 18Aという2つのプロセスノードを投入する計画だ。

Intel 20AとIntel 18Aは、新しいRibbon FETと呼ばれる4D形状のトランジスタとパワービア(PowerVia)と呼ばれる構造が採用される。これは、電源層を裏面に集中させて半導体の性能向上させるものだ。Intel 20AとIntel 18Aは今年(2024年)中に製造開始が予定されており、2025年にはIFSの顧客が実際に製造に利用することが可能になる。

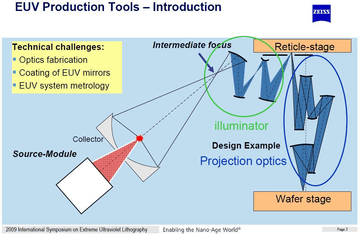

そして、今回のIFSでIntelは、そうした5N4Y(5Node4Years)の後のプロセスノードのロードマップを公開。それがIntel 14Aで、高NA EUV(High-NA EUV)と呼ばれる、さらに微細化されるEUV(Extreme Ultra-Violet、極端紫外線)を利用したプロセスノードになるという。

高NAとは光学系を改良してNA(開口数)を向上させることで回路を焼き付ける時の解像度を高める技術。詳しくは以下の記事の詳しいのでそちらをご参照いただきたい。

また、Intelは既に導入(あるいはこれから導入される)プロセスノードの拡張版の導入も進める。

具体的には、プロセスノードに「T」、「E」、「P」などのアルファベットを付加した拡張版が順次導入される。TはFoverosの3Dチップレットを利用する場合にTSV(Through Silicon Vias)を利用できることを意味し、Eは機能拡張、Pは性能向上版であることを意味する(PTもあり、それはPとTの両方を包含することを意味する)。

今年中にIntel 3-Tが投入され、2025年以降にIntel 18A-P、Intel 3-E、Intel 3-PT、そして2027年以降にIntel 15-Eが投入される計画だ。そのようにプロセスノードのバリエーションを増やすことで、IFSの顧客のさまざまなニーズに応える計画だ。

このほかにも、今回のイベントでIPパートナーやEDA(Electronic Design Automation)パートナーの拡大も明らかにしている。

既にIntelはArmと契約を行ない、ArmがIFSのプロセスノードにArmアーキテクチャの最適化を行なうことを明らかにしている。また、Synopsys、Cadence、Siemens、Ansys、Lorentz、 Keysightといった各EDAツール(半導体の設計を行なう時に使用するツール)が、Intel 18AやIntelの後工程の技術(例えば2.5DのEMIBなど)を利用したデザインフローの提供を開始したとIntelは明らかにしている。これらにより、ファブレス半導体ベンダーは、既にTSMCやSamsungなどのファウンドリで製造する際に利用しているEDAツールを利用して、IFS向けに設計して製造を行なうことが容易になることを意味しており、IFSでの製造ハードルが1つ下がることになる。

![【Amazon.co.jp限定】 伊藤園 磨かれて、澄みきった日本の水 2L 8本 ラベルレス [ ケース ] [ 水 ] [ 軟水 ] [ ペットボトル ] [ 箱買い ] [ ストック ] [ 水分補給 ] 製品画像:3位](https://m.media-amazon.com/images/I/41n0o65dSkL._SL160_.jpg)

![犬と猫のベーシック画像診断学 腹部編 [ 獣医放射線学教育研究会 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5647/9784895315647_1_2.jpg?_ex=128x128)

![美的2026年8月号 [雑誌] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0866/4912074430866.jpg?_ex=128x128)

![ママ投資家が育休中に1億貯めた株式投資 [ ちょる子 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2983/9784478122983_1_8.jpg?_ex=128x128)

![バックステージ パス 2026年 7月号 [雑誌] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0768/4912175570768.gif?_ex=128x128)

![おいしい!イラストレッスン クレパスで描きました [ momo ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1558/9784522441558_1_2.jpg?_ex=128x128)

![[新品]逃げ上手の若君 (1-25巻 最新刊) 全巻セット 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0035/m8880400172_01.jpg?_ex=128x128)

![【全巻】STEEL BALL RUN 1-24巻セット ジョジョの奇妙な冒険part 7 (ジャンプコミックス) [ 荒木飛呂彦 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3135/2100013433135_1_2.jpg?_ex=128x128)

![動ける体が大復活する1分体操 [ 中山潤一 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4625/9784776214625_1_2.jpg?_ex=128x128)

![臨床区域麻酔科学書 [ 日本麻酔科医会連合出版部 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1191/9784521751191_1_3.jpg?_ex=128x128)