笠原一輝のユビキタス情報局

AI性能を引き上げるために、あらゆる機能が強化されたNVIDIAの「H100」

2022年3月25日 09:41

NVIDIAが開発コードネーム「Hopper」で知られる新しいGPUアーキテクチャを採用したHPC用の「NVIDIA H100 GPU」(以下H100)を発表し、第3四半期から提供を開始することを明らかにした。

NVIDIAが3月23日からオンラインで開催しているGTC 2022では、そうしたNVIDIA H100の技術的な詳細が明らかになってきたので、以下その詳細に関して解説していきたい。

NVIDIAが発表した技術的な詳細から明らかになってきたのは、NVIDIA H100が半導体レベルでも、ソフトウェアのレベルでも、そしてプラットホームのレベルでも手が入れられており、特にDGXのようなサーバー機器レベルで、クラスターとして利用した場合に大きく性能が向上している事実だ。この点は、AIの学習や科学技術演算などで性能が足りていない組織や企業にとっては朗報と言える。

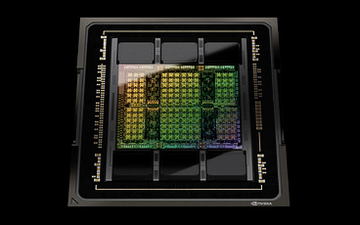

4Nプロセスノードで製造され、814平方mmと巨大チップになっているH100のダイ「GH100」

「Hopper」の開発コードネームを持つ新アーキテクチャGPUのH100は、従来のAmpereアーキテクチャの「A100」GPUの後継となる製品。NVIDIAがGTC開始後に公開した資料などによれば、大きく以下の7つの点で強化されている。

- 内部の演算ユニットが増加されている(SM数はGA100の108から132に増やされている)

- L1データキャッシュが256KB、L2キャッシュが50MBに増やされている(A100はそれぞれ192KB、40MB)

- FP8を新しくサポートした第4世代のTensorコア

- FP32やFP64のFMA(Fused Multiply Add、融合積和演算)が2倍高速になっている

- 新しいCUDA仕組みが導入されている(Thread Block Clusterの導入)

- 非同期データ転送の仕組みが導入されている(TMAの導入)

- 第4世代のNVSwitchに対応し、NVIDIA独自の高速なインターコネクトNVLinkだけで最大256のGPUを接続することができる

これらの改良は、簡単に言えばAIの学習性能を引き上げることが最大の目標になっている点。チップレベルで性能を引き上げるとともに、ソフトウェアもより効率よく演算できるようになっていて、それをスケールアップ(サーバー機器の中で複数のGPUを接続すること)し、そしてNVLinkがスケールアウト(サーバーラックの中で複数のサーバー機器を接続して拡張すること)にも利用できるようになることで、さらに巨大なGPUの塊を作り出し、これまでより高速にAI学習や科学演算などを可能にしているのだ。

H100のリリースにあたり、開発コードネームGH100で呼ばれるダイを設計し、TSMCの4NプロセスノードのNVIDIAカスタム版で製造している。2年前に発表されたNVIDIA A100に採用されていたGA100のダイとの違いは以下のようになっている。

| GA100 | GH100 | |

|---|---|---|

| SM | 128 | 144 |

| GPC | 8 | 8 |

| GPC辺りのSM数 | 16 | 18 |

| Tensorコア | 第3世代 | 第4世代 |

| Tensorコア数(GPU全体) | 512 | 576 |

| メモリコントローラ | 12xHBM2(512bit) | 12xHBM3(51b2it) |

| トランジスター数 | 542億 | 800億 |

| GPUダイサイズ | 826平方mm | 814平方mm |

| 製造プロセスノード(TSMC) | 7 nm N7 | 4N(NVIDIAカスタム) |

なお、これらのスペックはいずれもダイ設計時のフルスペックで、実際に製品化される時にはいくつかのSMやメモリコントローラなどが無効にされて出荷される。そうしないと歩留まり(検査後の良品率のこと)が極端に悪化し、最悪の場合出荷することが不可能になるため、半導体業界ではそうした手法をとるのが一般的だ。もちろん一般論として歩留まりが向上すれば、フルスペックで出荷することもあり得るが、前世代のA100のダイである「GA100」がそうだったように、800平方mmを超える巨大チップの場合にはフルスペックの歩留まりはかなり少ないと考えられるので可能性は低い。

例えば製品版のH100のSMは132個のSMというスペックになっており、フルスペックの144個に比べると減らされている。これは12個を無効にすると、出荷できるレベルの歩留まりに達するためこうした措置が取られていると考えるられる。GA100も同様で、設計上は128個のSMがあるが、製品として出荷されたNVIDIA A100は108個SMとなっている。

なお、GH100のダイサイズは814平方mmと、GA100の826平方mmよりわずかに小さくなっているが、業界でも最大級の巨大チップであることは変わっていない。トラジス多数はGA100の542億から増えて800億となっており、それはTSMCの7Nから 4Nにプロセスノードが微細化したことの恩恵と考えられる。

汎用演算器となるSMは数が増加し、キャッシュ階層も強化されている

H100のGPU汎用演算器部分となるSMは正常進化と言える。強化点は大きく2つあり、1つはSM数の増加で、もう1つがキャッシュ階層の強化だ。

| 製品 | NVIDIA A100 | NVIDIA H100 SXM5 | NVIDIA H100 PCIe |

|---|---|---|---|

| GPUアーキテクチャ | NVIDIA Ampere | NVIDIA Hopper | NVIDIA Hopper |

| GPUダイコードネーム | GA100 | GH100 | GH100 |

| フォームファクター | SXM4 | SXM5 | PCIe Gen 5 |

| SM | 108 | 132 | 114 |

| TPC | 54 | 66 | 57 |

| FP32コア/SM | 64 | 128 | 128 |

| FP32コア/GPU | 6,912 | 16,896 | 14,592 |

| FP64コア/SM (Tensorを含めない) | 32 | 64 | 64 |

| FP64コア/GPU(Tensorを含めない) | 3,456 | 8,448 | 7,296 |

| INT32コア/SM | 64 | 64 | 64 |

| INT32コア/GPU | 6,912 | 8,448 | 7,296 |

| Tensorコア/SM | 4 | 4 | 4 |

| Tensorコア/GPU | 432 | 528 | 456 |

| GPUブースト時クロック | 1,410MHz | 調整中 | 調整中 |

| 最大FP8 Tensor TFLOPS FP16 Accumulate有効時*1 | N/A | 2,000/4,000*2 | 1600/3200*2 |

| 最大FP8 Tensor TFLOPS FP32 Accumulate有効時*1 | N/A | 2,000/4,000*2 | 1600/3200*2 |

| 最大FP16 Tensor TFLOPS FP16 Accumulate有効時*1 | 312/624*2 | 1,000/2,000*2 | 800/1600*2 |

| 最大FP16 Tensor TFLOPS FP32 Accumulate有効時*1 | 312/624*2 | 1,000/2,000*2 | 800/1600*2 |

| 最大BF16 Tensor TFLOPS FP32 Accumulate有効時*1 | 312/624*2 | 1,000/2,000*2 | 800/1600*2 |

| 最大TF32 Tensor TFLOPS*1 | 156/312*2 | 500/1,000*2 | 400/800*2 |

| 最大FP64 Tensor TFLOPS*1 | 19.5 | 60 | 48 |

| 最大INT8 Tensor TOPS*1 | 624/1248*2 | 2,000/4,000*2 | 1,600/3,200*2 |

| 最大FP16 TFLOPS (Tensor未使用時)*1 | 78 | 120 | 96 |

| 最大BF16 TFLOPS (Tensor未使用時)*1 | 39 | 120 | 96 |

| 最大FP32 TFLOPS (Tensor未使用時)*1 | 19.5 | 60 | 48 |

| 最大FP64 TFLOPS (Tensor未使用時)*1 | 9.7 | 30 | 24 |

| 最大INT32 TOPS*1 | 19.5 | 30 | 24 |

| テクスチャユニット | 432 | 528 | 456 |

| メモリインターフェース | HBM2(5120-bit) | HBM3(5120-bit) | HBM2e(5120-bit) |

| メモリ容量 | 40GB | 80GB | 80GB |

| メモリデータレート | 1215MHz DDR | 調整中 | 調整中 |

| メモリ帯域幅 | 1,555GB/s | 3,000GB/s | 2,000GB/s |

| L2キャッシュ(ダイ全体) | 40MB | 50MB | 50MB |

| シェアードメモリサイズ/SM | 最大164KBに設定可能 | 最大228KBに設定可能 | 最大228 KBに設定可能 |

| レジスターファイルサイズ/SM | 256KB | 256KB | 256KB |

| レジスターファイルサイズ/GPU | 27,648KB | 33,792KB | 29,184KB |

| TDP*1 | 400W | 700W | 350W |

| *1 NVIDIA H100のスペックは変更される可能性がある | |||

| *2 スパース性を利用した場合 | |||

NVIDIAはGPUを大きいブロックから順に、GPC(GPU Processing Cluster)、SM(Streaming Multiprocessor)、Lanes(レーン)というブロックに分割しているが、A100もH100もいずれもGPCは8つという基本的な骨格は変わっていない。違いはGPCあたりのSMの数で、GA100のフルスペックでは1つのGPCあたり16個のSMが入る形になっていたが、GH100のフルスペックではGPCあたり18個に増やされている。このため、GPU全体のSMも増えている。

もう1つの強化点であるキャッシュ階層では、GPC 1つごとに搭載されているL1データキャッシュが192KBから256KBに、そしてGPU全体のL2キャッシュが40MBから50MBに増やされている。

ただ、今回NVIDIAはこうしたGPU全体の構造に関してはあまりアピールしていない。GPCあたりのSMが2つ増えたこと、キャッシュ階層が改良されたことがその大きな強化点となるので、NVIDIA自身もそこは大きな強化点と考えていないと言うことだろう。

Tensorコアに進化しFP8対応と処理能力が2倍に、CUDAの改良でメモリのロカリティ問題を低減

それに対して大きな強化点となっているのがTensorコアだ。Tensorコアは、NVIDIA V100で初めて導入された一種のアクセラレータで、行列積和(MMA)演算を実行するための演算器となる。このTensorコアを利用すると、FMA(Fused Multiply Add、融合積和演算)のような、複雑で演算器に負荷がかかる演算を、SMに内蔵されている浮動小数点演算器よりも高速に演算できる。今回のH100ではTensorコアのコア数も従来の512から576に増やされている。

今回のH100におけるTensorコアの最も大きな強化ポイントは、新しくFP8に対応したことと、演算性能そのものが倍になっていることだ。

A100世代まではFP64、FP32、FP16、INT8というデータの精度に対応していた。今回の第4世代となるTensorコアではFP8という新しい精度に対応し、性能向上を実現している。なぜFP8に対応しているかと言うと、最近のAIの演算ではFP8やINT8などのより低い精度に置きかえて演算することが増えているからだ。精度をINT8やFP8に置きかえて演算しても、あまり正確性は落ちないことが確認されており、そうした形で演算することが増えているのだ。

なお、このFP8はE5M2(指数が5bit、仮数が2bit)と呼ばれる形式と、E4M3(指数が4bit、仮数が3bit)と呼ばれる2つのフォーマットに対応している(残り1bitは符号)。NVIDIAによればE4M3が一般的には使われているが、E5M2も一部にニーズがあるということで下位互換性のためにサポートされていると言うことだった。

また、Tensorコア自体の動作スピードも倍になっており、FP64、TF32、FP16、Bflot16、INT8などの以前からサポートされているデータ形式の演算性能は倍になっている。FP8を利用した場合には、A100の内蔵演算器で演算した場合の6倍になっているとNVIDIAは説明している。

このTensorコアとソフトウェアを組み合わせて実現されているのがTransformer Engineと呼ばれているソフトウェアエンジンで、ソフトウェアが自動で判別してFP8に精度を落としてより短い時間で演算することを可能にする。もちろん、時間がかかっても精度を落としたくない場合にはオフにすることも可能だ。

CUDAのプログラムがGPCをクラスターとして扱いデータロカリティの発生を防ぐ

そしてもう1つの大きな改良点はプログラミングモデルのCUDAレベルでの改良になる。それがデータロカリティ(データがローカルのメモリにあるかで発生するレイテンシの削減)と非同期実行という2つの改良点だ。

H100では「Thread Block Cluster」という機能が追加されている。具体的には、CUDAにGPCのレベルを扱う新しい階層として「クラスター」が導入される。

従来のCUDAではGPCを扱う階層がなかったため、データのロカリティという問題が発生していた。簡単に言えば、データがGPUの中に階層的に用意されているメモリ(メインメモリ、L2キャッシュ、L1キャッシュ)のどこに置かれているかという問題で、それが演算しようとするSMから近いところにあればいいのだが、演算しようとするSMが属しているGPC上にはないと、L2キャッシュを読みいったり、メインメモリに読みにいったりして、演算器の待ち時間、つまりメモリレイテンシが増大してしまう問題があった。

そこで、処理しているスレッドをクラスターでブロックして、同じデータを実行するスレッドはできるだけ同じGPCの中にあるSMで実行するようにし、より効率の良いメモリアクセスを可能にする。それによりメモリレイテンシや、内部の帯域が圧迫されることを防ぐことができる。

CUDAができた当初にはSMの数も少なかったためこうした問題は明らかになっていなかったが、今のGPUはSMだけでも100を超えており、こうした仕組みが必要になっているとNVIDIAは説明した。

また、非同期実行では、TMA(Tensor Memory Accelerator)という新しいハードウェアがSMに内蔵されている。これはCPUのDMA転送と同じようなもので、メモリをメインメモリからキャッシュに転送する場合、あるいはほかのクラスターのキャッシュに転送する場合を、GPUの演算器を使わずに行なうことができる。それにより、GPUの演算とメモリ転送が非同期で行なえるようになり、GPU全体の性能が向上することになる。

NVLinkは第4世代になって帯域強化、NVSwitchも進化してNVLinkをDGX32台のスケールアウトにも利用可能

そして、H100のもう1つの大きな強化点はNVLinkの強化だ。NVLinkはGPUとGPUを接続するインターコネクトとして開発されたものだが、現在はNVSwitchというスイッチコントローラも用意されていることで、2つのGPUだけでなく、8つとNVSwitchを利用することでGPUの数をスケールアップできるようになっている。

そうしてスケールアップして、複数のGPUを1つのGPUとして扱うことで、性能を上げていく、これがNVIDIAの近年のデータセンター向けGPUの基本的な戦略だ。今回のH100に内蔵されているNVLinkのコントローラは第4世代となっており、リンクあたり25GB/sで18リンクというスペックになっており、最大900GB/sという超広帯域を実現している。

そうしたNVLink自体が広帯域になっただけでなく、NVLinkのスイッチチップであるNVSwitchも第3世代となり、64ポート、双方向で1.7TB/sを実現しているほか、新しく「SHARP」と呼ばれる仕組みが導入されて、実効帯域が約2倍になっているという。そうした拡張により、GPUのNVLinkとNVSwitchを組み合わせると、最大で256基のGPUをまとめて1つのGPUとして扱うことができる。

従来NVIDIAが販売していたA100を8個搭載したサーバーアプライアンス「DGX A100」では、4つのNVSwitchを利用して8つのGPUを1つの巨大GPUとして扱えるようになっていた。そして、さらに32個のDGX A100をInfiniBandで接続してスケールアウト(サーバーとサーバーを何らかのネットワークで接続して巨大なクラスターを作ること)して利用することが可能になっていた。

H100のDGX H100でも基本それは同じなのだが、NVLinkが第4世代になって帯域幅が向上したこと、そしてNVSwitchが第3世代になり、簡単に言うとスケールアウトにInfiniBandに替えてNVLinkで使えるようになる。具体的にはDGX H100同士の接続は、NVSwitchを利用することで、NVLinkで接続することが可能になる。これは新しいNVSwitchが256個のGPUを接続することが可能になっているためで、8個のH100を搭載しているDGX H100を32台NVLinkで接続してスケールアウトできる。この場合GPUは256個を1つの巨大GPUとして扱うことが可能になる。もちろん性能も引き上げられ、InfiniBandで32台のDGX A100をスケールアウトした場合の性能である80PFLOPSに比べて、NVLinkで32台のDGX H100をスケールアウトした場合には6.4倍の512PFLOPSとなると説明している。

さらにInfiniBandと組み合わせると、256のGPUから構成されるNVLinkクラスター(つまり32台のDGX H100)を4つ(32×4=128)まとめて最大で1,024個のGPUとしてクラスターを構成することができる。その場合には2,048PFLOSと2EFLOPSにも達する演算性能を実現することが可能になっている。NVIDIAはこの1,024個GPUから構成されているスーパーコンピュータをEoS(イオス)というブランドで製品化する計画とGTCで明らかにしている。

このように、今回NVIDIAは、GPUという半導体のレベルでも、そしてCUDAというプログラミングモデルのレベルでも、そして最後にInfiniBandをNVLinkに置きかえるネットワークのレベルでも大きな強化をしており、新しいNVSwitchを利用すると、DGX H100を32台接続してNVLinkだけで巨大なGPUクラスターを構成することが可能になる。これにより512PFLOSという性能を実現可能になる。汎用の半導体だけでそこまでの性能を実現される。

さらに、それを4つクラスター化することで、2EFLOPSのという性能を実現している。このことは、科学演算やAI学習の性能が足りていないと考えている組織や企業などにとっては大きなインパクトをもって迎えられるだろう。

![ASUS ノートパソコン Chromebook Plus CX34(CX3402) CX3402CVA-MW1032 [パールホワイト] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/winkstore/cabinet/272500/272451.jpg?_ex=128x128)

![★エイスース / ASUS TUF Gaming T500MV T500MV-13420H412W [ソーラーエクリプスグレー]【デスクトップパソコン】【送料無料】 製品画像:6位](https://thumbnail.image.rakuten.co.jp/@0_mall/d-rise/cabinet/img054/p000000913791_1.jpg?_ex=128x128)

![わたしはこれでやせました [ MEGUMI ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4512/9784478124512_1_2.jpg?_ex=128x128)

![角川まんが学習シリーズ 日本の歴史 5大特典つき全16巻+別巻5冊セット [ 山本 博文 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3680/9784041153680_1_17.jpg?_ex=128x128)

![【楽天ブックス限定特典】KEITA MACHIDA 15th Anniversary Photobook 「sign」(限定トレカ) [ 町田啓太 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1991/2100014771991_1_3.jpg?_ex=128x128)

![リーガルプログレッシブ14 建築訴訟 改訂版 [ 小久保孝雄 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9060/9784417019060_1_2.jpg?_ex=128x128)

![[新品][ライトノベル]ようこそ実力至上主義の教室へ (全32冊) 全巻セット 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0029/set-youjitsu_01.jpg?_ex=128x128)

![世界は自分で創造する IQ148の天才舞踏家が語る現実創造の法則 [ 大瀧冬佳 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7989/9784815637989_1_9.jpg?_ex=128x128)

![CARPE DIEM 今この瞬間を生きて [ ヤマザキマリ ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1640/9784767831640_1_2.jpg?_ex=128x128)

![異常に非ず [ 桜木 紫乃 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7279/9784103277279_1_22.jpg?_ex=128x128)