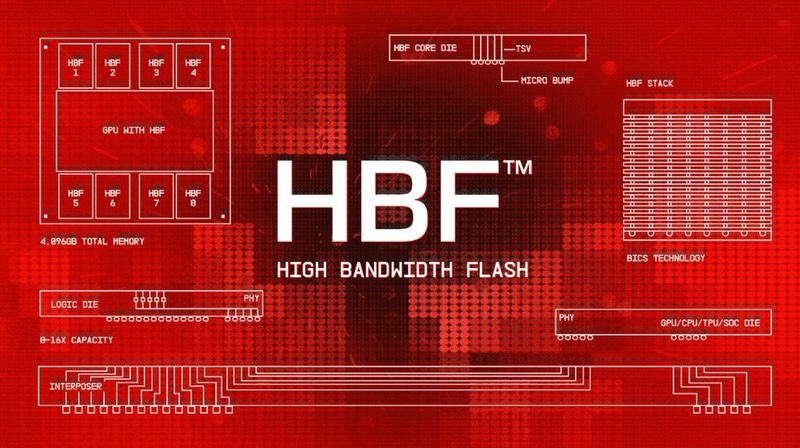

「フラッシュHBM」こと「HBF(High Bandwidth Flash)」を構成する部品と相互接続。左上が基板レイアウトの例。中央にGPUダイ、その上下にHBFモジュール(8/16枚のフラッシュメモリダイ(コアダイ)積層構造と1枚のロジックダイで構成)を4つずつ配置したもの。左中央が、HBFの最下段に位置するロジックダイの断面図。中央上がコアダイの断面図。シリコン貫通電極(TSV)とマイクロバンプによって上下のシリコンダイ(コアダイあるいはロジックダイ)と接続する。右上はHBFの断面構造例。16枚のコアダイと1枚のロジックダイを積層している。右下はGPU(またはCPU/TPU/SoC)ダイの断面構造。マイクロバンプによって中間基板(インターポーザ)と接続する。中央下はインターポーザの断面構造(一部のみとみられる)。インターポーザの左側にHBF(ロジックダイあるいはベースダイ)、右側にGPUダイを搭載すると思われる。Sandiskが2025年2月11日(米国時間)に開催した投資家向けイベント「Investor Day」で発表したスライドから