福田昭のセミコン業界最前線

スケールが桁違い。TSMCが注力する超大規模高速パッケージ「SoW」とは

2025年7月4日 06:16

直径が300mmと大きなシリコンウェハあるいは同じ直径の円板状キャリア(支持母体)に巨大な規模の超高速システムをまとめる先端パッケージング技術 「システム・オン・ウェハ(SoW: System on Wafer)」を、TSMCが積極的に開発している。SoWは、複数のシリコンダイあるいはミニモジュールを2次元マトリクス状に並べることで、超大規模かつ超高速の演算処理能力と高速高密度のデータ転送、消費電力の低下を両立させる。

「InFO」技術を低コストの高性能大型パッケージに応用

SoW技術の源流は、TSMCが開発したモバイルプロセッサ向けパッケージ「InFO(Integrated Fan-Out、呼称は「インフォ」)」、一般的には「FO-WLP(Fan Out-Wafer Level Package)」と称される小型薄型パッケージング技術にある。

2020年前後にTSMCは、シリコン中間基板(Siインターポーザ)によってシリコンダイ間(水平方向に並べたダイ間)を高密度接続するパッケージ技術「CoWoS(Chip on Wafer on Substrate)」を高性能大規模ロジック(FPGAやGPUなど)向けに提供していた。一方で、InFO技術によってシリコンダイ間を高密度接続する「InFO_oS(InFO on Substrate)」技術を高性能大規模ロジックの低コスト版パッケージとして用意し、量産していた。

InFO_oSは寸法の拡大が比較的簡単であり、なおかつパッケージ基板にInFOのRDLを選択することで超多層配線基板を作れるといった利点があった。2018年にはレチクルの1.5倍の大きさに相当する、InFO_oSの量産を始めている。

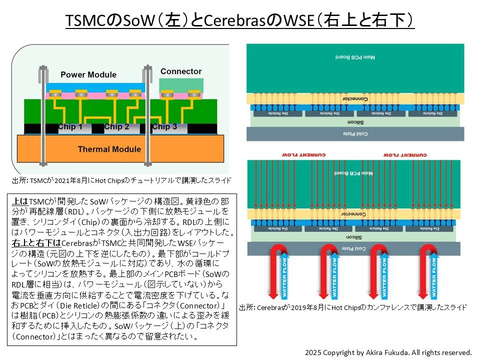

InFO技術をウェハサイズの大型パッケージに適用したInFO_SoW

InFO_oSの基板サイズ(RDLのサイズ)を直径300mmのシリコンウェハ級に拡大したのが、InFO_SoWだ。InFOの微細かつ高密度な再配線層(RDL)をウェハサイズまで拡大し、数多くのシリコンダイをフェイスダウン(シリコンダイの回路面がRDLと相対する方向)でRDLに載せる。シリコンダイを載せたRDLの裏面には電源モジュールや入出力ICを含むコネクタなどを搭載することで、システムモジュールを構成する。

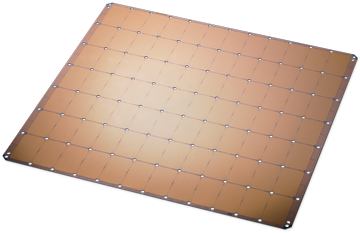

InFO_SoW技術は、AI向けハードウェアの開発企業Cerebras Systems(以降Cerebras)のディープラーニング用アクセラレータ「WSE(Wafer Scale Engine)」に採用された。WSEは、2019年8月に開催された高性能プロセッサ技術の国際学会Hot Chipsで、その技術概要が発表され、高性能プロセッサの開発コミュニティで大きな反響を呼んだ。なお同社は2019年8月19日に、WSEの開発をプレスリリースでも公式発表している。

TSMCのInFO_SoWとCerebrasのWSEの違い

InFO_SoW技術とWSE技術は全く同じではない。大きな違いはシリコンダイの扱いにある。InFO_SoW技術はチップレットを想定しており、異なる製造技術による数多くのミニダイ(良品確認済みのミニダイ)をウェハ大のRDLに搭載する。一方、WSE技術では直径300mmのシリコンウェハに84枚のミニダイを一括して製造する。84枚のミニダイはスクライブラインを介してつながっており、全体は正方形である。

すべてのミニダイをAIプロセッサのコアレベルでテストした後に、ミニダイ群の表面にミニダイ間およびプロセッサコア間を接続する配線(RDLの一部となる)を形成する。この配線はきわめて重要だ。テストで不良と判定したコアを省いて代替となる冗長コア(テストで良品と判定済みとみられる)を配線接続する。言い換えると、テスト後にRDLのミニダイ表面側配線のレイアウトが決まると見られる。

そしてここは推測になるのだが、ミニダイ群よりもわずかに大きな正方形のRDL基板を形成する、あるいは、あらかじめ製造しておいたRDL基板をミニダイ群に貼り付ける。RDL基板の寸法は215mm角であり、その外接円の直径は304mmとなる。300mmウェハよりもわずかに大きい。Cerebrasが公表したWSEの写真はRDL基板を含んでおり、しかも数多くのスルーホール(孔)が形成されている。スルーホール群は上下の電源モジュールやコネクタ、冷却プレートを機械的につなげるために開けられているものとみられる。

3世代のWSEでInFO_SoWを継続して採用

Cerebrasは2019年8月にWSEを発表した後、2021年4月には第2世代のウェハスケールプロセッサ「WSE-2」を、2024年5月には第3世代の「WSE-3」を発表してきた。いずれの世代もTSMCのInFO_SoW技術を採用しており、WSEの大きさ(215mm角)と搭載ダイ数(84枚)は変わらない。

大きく異なるのはシリコンダイの製造技術である。第1世代では、2019年当時としてはかなり緩やかな、16nmプロセスを採用した。2021年に発表した第2世代のWSE-2では微細化を一気に進め、7nmプロセスを採用した。2024年に発表した第3世代のWSE-3では5nmプロセスを選択して微細化をさらに進めた。この結果、第3世代が搭載するトランジスタの数は4兆個と、第1世代の1.2兆個から3.3倍強に増えた。

垂直短距離の電源配線が電圧の安定化と消費電力の削減に寄与

Cerebrasが3世代に渡ってWSEに300mmウェハのInFO_SoW技術を採用してきたのは、直径300mmを超える大きさのウェハが存在していないことの裏返しでもある。現時点における究極の大規模回路モジュールがInFO_SoW技術であるということだ。

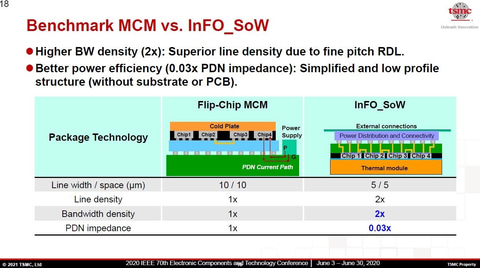

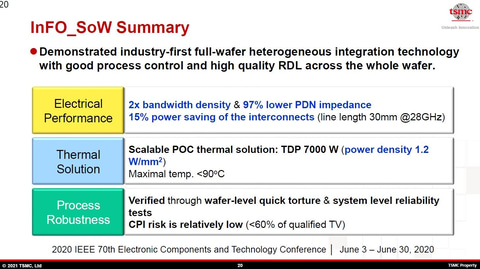

その基本性能は、中間基板を備えたマルチチップモジュール(MCM)と比べてシリコンダイ間の配線幅/間隔が半分、配線密度が2倍、単位長当たりのデータ転送速度が2倍、というものだ。最も大きな違いは電源供給インピーダンスで、MCMの33分の1しかない。215mm角のRDL層の裏面全体を原理的には電源モジュールにレイアウトできるとともに、電源配線群が垂直方向(縦方向)なので配線長がきわめて短いからだ。電源供給インピーダンスの低さは、電源電圧の安定化と消費電力の削減に大きく寄与する。

TSMCは、InFO_SoW技術の次世代に相当するSoW技術の開発にも取り組んでいる。名称は「SoW-X(eXtreme)」だ。また開発済みのInFO_SoW技術は最近になって名称を「SoW-P」に変更した。

SoW-PとSoW-Xの違いは、前者が同一のプロセッサを敷き詰めるのに対し、後者はプロセッサ(あるいはSoC)とメモリのモジュールを敷き詰めることにある。次世代品SoW-Xの概要については、機会を改めて本コラムで述べたい。

![[月間優良ショップ] ミニパソコン デスクトップパソコン ミニPCコンピューターボヂィ Windows11 第13世代 Core i7 13500H 最大5.0GHz 小型 静音 pc 超軽量PC 小型デスクトップパソコン 16GB SSD 1TB DDR4 メモリ office2021 ゲーム 省スペース 製品画像:4位](https://thumbnail.image.rakuten.co.jp/@0_mall/japan-beauty/cabinet/12412735/12472048/dnzj005.jpg?_ex=128x128)

![IOデータ 3辺フレームレス&広視野角ADSパネル液晶ディスプレイ [21.5型 /フルHD(1920×1080) /ワイド] ブラック KH-A221DB 製品画像:16位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001006/4957180170312_1.jpg?_ex=128x128)

![女の園の星 5 特装版 (FCswing) [ 和山やま ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1050/9784396751050.gif?_ex=128x128)

![【5/1限定500円OFFクーポン】 \ レビュー投稿で追加イベントカード / 日めくりカレンダー 知育 カレンダー 日めくり 子供 卓上 万年カレンダー 万年 かわいい おしゃれ マンスリーカード レターバナー 赤ちゃん 月齢フォト 月齢カード 北欧 インテリア 1年 [MUQQU] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/e-kit/cabinet/description/ek-hcd/ek-hcd_1_cp500.jpg?_ex=128x128)

![アオのハコ 25 【電子書籍】[ 三浦糀 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2550/2000020202550.jpg?_ex=128x128)

![エネルギー管理士試験[熱分野]徹底研究(改訂3版) [ 不動 弘幸 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1353/9784274231353.jpg?_ex=128x128)

![盛土等防災マニュアルの解説 [ 盛土等防災研究会 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3301/9784324113301_1_3.jpg?_ex=128x128)

![タヌキまるごとBOOK [ 今泉忠明 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3498/9784777833498_1_3.jpg?_ex=128x128)

![コンプティーク 2026年 6月号 [雑誌] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0661/4912139770661.jpg?_ex=128x128)

![sweet (スウィート) 2026年 6月号 [雑誌] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0665/4912154410665.gif?_ex=128x128)

![逃げ上手の若君 25 【電子書籍】[ 松井優征 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2520/2000020202520.jpg?_ex=128x128)

![カグラバチ 11 【電子書籍】[ 外薗健 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2521/2000020202521.jpg?_ex=128x128)