福田昭のセミコン業界最前線

GPUモジュールも将来はウェハサイズに。第2世代の「SoW」をTSMCが開発中

2025年7月31日 10:07

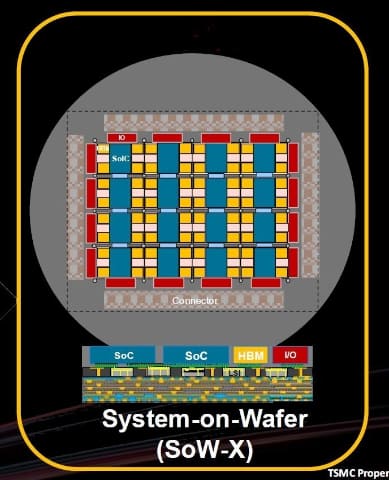

TSMCはこのほど、直径が約300mmと巨大なシリコンウェハあるいは同じサイズの円板状キャリアにシステムを集積する超大型パッケージング技術「システム・オン・ウェハ(SoW: System on Wafer)」の「第2世代品」を開発していることと、その技術概要を公表した。

SoWは、ミニダイ(チップレット)やチップレットの積層モジュール、メモリモジュール、電源モジュール、入出力、放熱プレートなどを直径が約300mmと巨大な円板状キャリアの両面に搭載する。ミニダイやメモリなどは再配線層(RDL)を通じて高密度かつ近距離で相互に接続し、超広帯域の信号伝送を実現する。

直径が約300mmの円板という形状とサイズは、半導体製造装置がごく普通に扱う形状とサイズでもある。このため、半導体製造の要素技術を適用しやすい。既存の製造装置をベースにしたカスタマイズが比較的容易というメリットもある。

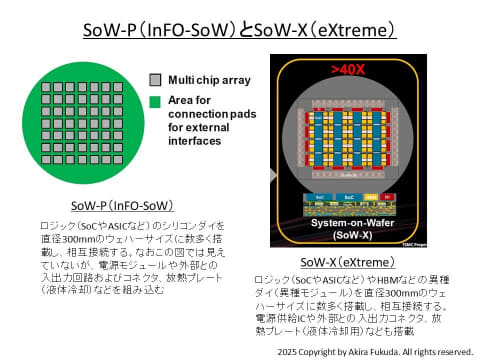

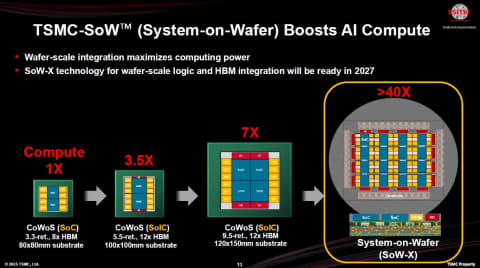

TSMCはSoWの第1世代品「InFO_SoW」を2019年に開発し、量産を始めた。この第1世代品を同社は、「InFO_(Integrated Fan-Out、基本的にはFO-WLPと同じ)」技術のRDLサイズを、直径が約300mmの円板に拡大したパッケージング技術と位置付けていた。第1世代品InFO_SoWの技術概要と応用事例は、本コラムの前回で解説した。ご興味のある方は参照されたい。

第1世代品はロジック、第2世代品はロジックとメモリを集積

本コラムの前回末尾でも述べたように、TSMCはSoWの第1世代品を「SoW-P」に改称するともに、第2世代品を「SoW-X(eXtreme)」と名付けた。

同社は2025年5月下旬に米国で開催されたパッケージング技術の国際学会ECTC 2025で、SoW-Pは主要回路としてSoCだけを300mmウェハサイズに集積する技術であるのに対し、SoW-Xは主要回路としてSoCとHBMを混載する異種集積(ヘテロジニアス・インテグレーション)技術だと口頭で説明していた。

第2世代品は高性能パッケージ「CoWoS」の発展形

もう1つの大きな違いは、第1世代品がInFO技術の大型化であるのに対し、第2世代品は高性能パッケージ「CoWoS(Chip on Wafer on Substrate)」を大型化したものであることだ。CoWoSでは、パッケージ基板(樹脂基板)とシリコンダイ(マルチチップ)の間に別の基板(中間基板またはインタポーザと呼ばれる)を挟む。

RDLはビア径/間隔と配線幅/間隔がパッケージ基板よりもはるかに小さい。隣り合うチップの間隔を大幅に短くするとともに、入出力配線の密度を大きく高められる。単位長当たりのデータ転送速度が著しく上昇する。CoWoSの中間基板には当初、シリコン基板(Siインタポーザ)が選ばれた。シリコンの中間基板はシリコンダイと熱膨張率がほぼ同じなので、温度変化による歪みが原理的には起こらない(実際には製造工程に工夫が必要)。

CoWoSの初期製品は2012年に登場した。FPGAの大手メーカー2社が、FPGAのマルチチップモジュールに採用した。たとえば1つはFPGAの同じダイ4枚をSiインタポーザ上に近接配置したモジュール、もう1つはFPGAのダイ1枚とメモリのダイ1枚をSiインタポーザ上に近接配置したモジュールである。Siインタポーザの面積は最大775平方mmで、ArFスキャナの露光領域858平方mmにかなり近い。1枚のマスク(レチクル)で露光できるギリギリのサイズだとも言える。

CoWoSの巨大化を牽引したブレークスルー「スティッチング」

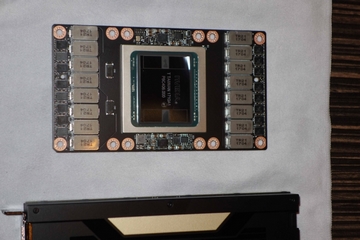

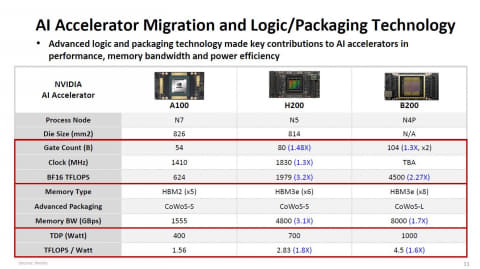

CoWoSの実質的な普及は2016年の第2期から始まったと言えよう。ArFスキャナの露光領域858平方mmを超える、巨大なSiインタポーザを量産できるようになったことが大きい。GPU大手のNVIDIAが大規模GPU「GP100」のパッケージにSiインタポーザ技術を採用したのだ。GPUチップGP100を1個と、HBM2モジュールを4個、Siインタポーザに混載した。Siインタポーザの面積は1,160平方mmである。

Siインタポーザ1枚の製造には2枚のマスクを使う。マスクで露光する長方形領域の1辺をわずかに重ねてつなぐことにより、マスク1枚の露光面積をはるかに超える大きさのSiインタポーザを作る。このつなぎ合わせ技術は「スティッチング(Stitching)」と呼ばれる。2枚のマスクを使うことで、理論的には1,700平方mm近い大きさのSiインタポーザを製造できる。

スティッチングの開発と改良により、レチクルの3.3倍もの面積に達するSiインタポーザが2023年には製造可能になった(Siインタポーザ当たりで4枚のマスクを使って回路パターンをつなぐ)。しかしこの段階で、Siインタポーザのこれ以上の拡大は難しくなりつつあった。インタポーザのコアであるシリコンの材料コストとシリコン貫通ビア(TSV)の製造コストが、インタポーザのサイズ拡大とともに増加し、顧客にとって許容が難しくなってきた。

レチクルの3.3倍でSiインタポーザの大型化は限界に

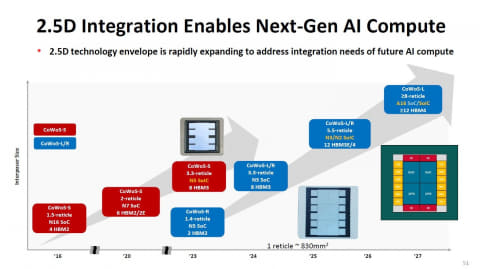

そこでシリコンよりもコストの低い有機樹脂をコアに選択したインタポーザがCoWoSに使われるようになってきた。このCoWoS技術は大別すると3種類ある。

1つはRDLをインタポーザとする「CoWoS-R」、もう1つは「ローカルシリコンインターコネクト(LSI: Local Silicon Interconnect)」と呼ぶシリコンの小片(ブリッジ)を樹脂コアに埋め込む「CoWoS-L」、3番目はLSIとRDLを組み合わせた「CoWoS-L/R」である。なおSiインタポーザを採用した従来のCoWoSは、最近では区別のために「CoWoS-S」と呼称が変更されている。

CoWoS-Rの量産は、中間基板がレチクルの1.4倍と小さめのサイズから始まった。続いてレチクルの3.3倍と、CoWoS-Sと同じ大きさの中間基板を使うCoWoS-L/Rを開発して量産を始めた。この段階でCoWoS-Sは開発ロードマップから消え、CoWoS-L/RまたはCoWoS-Lによって中間基板のサイズを拡大する開発ロードマップに換わった。

CoWoSからSoWへ

2024年12月時点でのCoWoS技術の開発ロードマップは、2025年~2026年にレチクルの5.5倍と大きな中間基板を備えるCoWoS-L/Rを開発し、2026年~2027年にレチクルの8倍を超える巨大な中間基板を備えるCoWoS-Lを開発する計画となっている。

そして2025年6月11日にTSMCが配布した報道機関向け資料では、CoWoS技術の開発ロードマップは以下のようになっていた。始めは中間基板がレチクルの3.3倍となるCoWoSである。2個のSoCと8個のHBMモジュールを中間基板に搭載した。パッケージの大きさは80mm角である。

次に中間基板をレチクルの5.5倍に拡大したCoWoSを開発する。シリコンダイを3次元積層したSoIC(System on Integrated Chips)を2つ、それから12個のHBMモジュール、2個の入出力回路(IO)を中間基板に載せる。パッケージの大きさは100mm角である。

その次は、中間基板をレチクルの9.5倍に拡大したCoWoSを開発する。シリコンダイを3次元積層したSoICを4つ、それから12個のHBMモジュールを中間基板に載せる。パッケージ基板の大きさは120×150mmに達する。このCoWoSが、2024年12月時点での開発ロードマップで示された「レチクルの8倍を超える巨大な中間基板を備えるCoWoS-L」に相当するとみられる。

そしてレチクルの9.5倍に中間基板を拡大したCoWoSの次に考えられているのが、300mmウェハ全体から1個のシステムモジュールを切り出すSoWである。基本単位(ユニット)は中間基板をレチクルの5.5倍に拡大したCoWoSで、ロジックを2つと12個のHBMで構成する(基本ユニットを構成するロジックの数とHBMの数は変わる可能性がある)。基本ユニットを2次元マトリクス状に配置して相互に接続し、大規模化と高性能化、性能あたりの消費電力低減を鼎立させる。

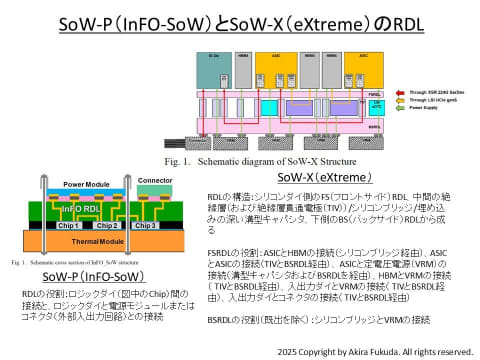

上下分離のRDLと3種類のシリコンブリッジを駆使

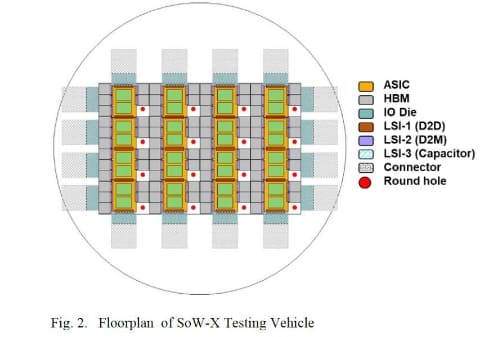

パッケージング技術の国際学会ECTC 2025でTSMCが公表したSoW-X技術は、CoWoS-L技術をベースとする。基本ユニットは1個のASIC(ロジック)とその両隣に5個のHBMを配置したサブモジュールである。原理的にはHBMの最大数は6個なのだが、放熱部を含めたシステム全体を貫通して固定する柱(ピラー)が必要なため、HBM1個分の領域が柱の孔開け用となっている。

中間基板は上部(シリコンリコンダイ側)にフロントサイドRDL(FSRDL)、中央部に樹脂コア(および樹脂貫通電極(TIV: Through Insulator Via))とローカルシリコンインターコネクト、下部にバックサイドRDL(BSRDL)で構成した。BSRDLの下側には定電圧モジュール(VRM)と入出力回路(コネクタを含む)を配置している。

FSRDLの配線層数はASICが6層、HBMが9層とかなり多い。なおHBMは、「HBM4」以降の世代を想定している。BSRDLの配線層数は信号用が5層、電源用が3層である。バックサイドRDLの信号用配線は長い距離(HBMの下をくぐってASIC間を結ぶ)を伝送するので、特性インピーダンスを90Ωに揃えるとともに差動伝送方式を採用した。

ローカルシリコンインターコネクトは3種類。1つは隣接するASIC間の接続用(D2D)、もう1つはASICとHBMの接続用(D2M)、3番目はシリコンキャパシタ兼TSV(Through Silicon Via)用である。

PCIe接続のクラスタに比べ、消費電力当たりの性能は65%向上

1個のASICとその両隣に合計5個のHBMを配置したサブモジュール(基本ユニット)を4×4の行列状に配置し、SoW-Xのモジュールを構成した。モジュールのサイズは横方向(水平方向)が218mm、縦方向(垂直方向)が190mmである。レチクルサイズに換算すると約48倍となる。

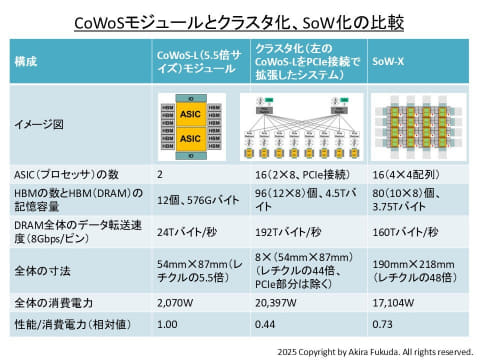

このSoW-Xを、レチクルサイズの5.5倍のCoWoS-Lモジュール(2個のASICと12個のHBMで構成)、および、8個のCoWoS-LモジュールをPCIe接続でクラスタ化したシステム(16個のASICと96個のHBMで構成)と比較した。クラスタ化とSoW-X化で比較すると、消費電力当たりの性能はSoW-Xが約65%高い。ただしCoWoS-Lモジュール単体に比べると、消費電力当たりの性能は27%低下する。

なおSoW-X全体の消費電力は17kWに達する。水冷による放熱を想定しており、ECTC 2025ではその点についても言及していた。水冷方式の放熱プレートはASICおよびHBMの上に配置する。

SoW-Xの実用化時期は2027年とされる。技術的に困難な課題は今のところあまりなく、高額と見られる製造コストを顧客が受け入れられるかどうかだろう。問題はむしろ、この後だ。中間基板の寸法拡大による大規模化と高性能化は、ウェハサイズで限界に達したように見える。その先はパネルサイズなのか、ウェハ積層なのか、それとも別の手法なのか。行方を見守りたい。

![ASUS エイスース 液晶ディスプレイ Eye Care [23.8型 / フルHD(1920×1080) / ワイド] VA249HG 製品画像:10位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001461/4711387795194_1.jpg?_ex=128x128)

![キングダム 79 【電子書籍】[ 原泰久 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2496/2000020202496.jpg?_ex=128x128)

![不夜脳 脳がほしがる本当の休息 [ 東島威史 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2481/9784763142481_1_3.jpg?_ex=128x128)

![ゼロからマスター 手・肘の鏡視下手術 [ 中村 俊康 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8983/9784758318983_1_3.jpg?_ex=128x128)

![【全巻】 SAKAMOTO DAYS 1-27巻セット (ジャンプコミックス) [ 鈴木 祐斗 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6906/2100014986906.jpg?_ex=128x128)

![今日もまた、ニック沼。 ズートピア行きのチケットは、どこで買えますか? [ 講談社 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7507/9784065427507.jpg?_ex=128x128)

![改訂版 本当の自由を手に入れる お金の大学 [ 両@リベ大学長 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3780/9784023323780_1_5.jpg?_ex=128x128)

![[新品]鋼の錬金術師 (1-27巻 全巻) 全巻セット 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0019/ha-21_01.jpg?_ex=128x128)

![角川まんが学習シリーズ 日本の歴史 全16巻定番セット [ 山本 博文 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1374/9784041131374_1_19.jpg?_ex=128x128)