福田昭のセミコン業界最前線

AMDとIntelの最先端「3.5次元」パッケージング技術とは

2024年6月11日 10:02

半導体パッケージング技術は2次元(2D)から3次元(3D)へ

半導体パッケージの密度向上と性能向上が一段と進んでいる。過去、高性能コンピューティング向けの大規模プロセッサはCPU回路と入出力回路を複数のミニダイ(チップレット)に分割して微細配線回路のインターポーザ(中間基板)に搭載することで、実装密度、動作周波数および信号伝送帯域の向上を実現してきた。

当初、ミニダイは中間基板の上に横に並べて搭載していた。従来のパッケージ基板と違うのは、インターポーザではミニダイの間隔を大きく詰められることだ。同時にミニダイの入出力パッドの間隔も詰められる。いずれもインターポーザでは従来のパッケージ基板と比べ、微細な配線を形成できることが大きく寄与している。ミニダイの入出力パッド間隔が詰まると、単位面積当たりの伝送チャンネル数を増やせる。高密度化と高性能化の両方を実現できる。これが「2.5次元(2.5D)パッケージング」と呼ばれる先進パッケージング技術である。なお従来のパッケージング技術は区別のために、「2次元(2D)パッケージング」と呼ばれるようになった。

次に密度と性能をさらに向上させるため、ミニダイを横に並べるのではなく、縦にならべる、つまり積層することが考えられた。パッケージ基板の上に複数のミニダイを積層すれば、実装面積を大きく減らせる。ミニダイ間を接続する距離は、横に並べた場合と比べて大幅に縮まる。これが「3次元(3D)パッケージング」と呼ばれる先進パッケージング技術である。

3Dと2.5Dを組み合わせて3.5Dへ

パッケージの集積密度と動作性能をさらに高めるのが、「3.5次元(3.5D)パッケージング」と呼ばれる技術だ。3Dパッケージと2.5Dパッケージを組み合わせたパッケージになる。2024年5月28日~31日に米国コロラド州デンバーで開催された半導体パッケージング技術に関する世界最大の国際学会「ECTC 2024(The 2024 IEEE 74th Electronic Components and Technology Conference)」では、AMDとIntelがそれぞれ、3.5Dパッケージングの開発成果を発表した。

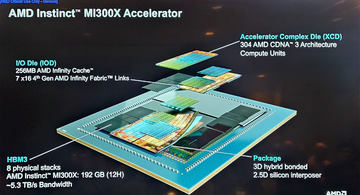

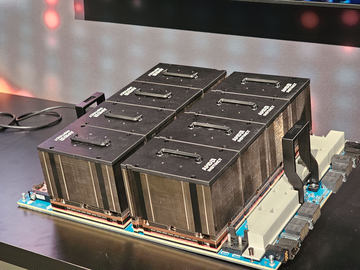

AMDは2023年12月に発表した最新のGPU製品「MI300シリーズ」に3.5Dのパッケージング技術を採用した。2.5Dのパッケージング技術はシリコンのインターポーザと入出力ダイ(IOD)、HBMモジュールの接続に導入した。すなわちインターポーザの上にIODとHBMモジュールをマイクロバンプによって接続している。インターポーザの面積は3,000平方mm(正方形換算で54.77mm角)とかなり大きい。露光領域(レチクル)の約3.6倍に相当する。

3Dのパッケージング技術は、IODとCPUダイ(CCD)あるいはGPUダイ(XCD)の3次元積層(3D Stack)に導入した。IODに形成したシリコン貫通ビア(TSV)電極とCCDあるいはXCDの表面電極をハイブリッド接合によって積層/接続している。なおMI300シリーズにはAPU製品の「MI300A」とGPU製品の「MI300X」があるが、パッケージング技術はほぼ変わらない。

Intelは3.5D向けに量産水準の3μmピッチHBI技術を開発

Intelも、3Dパッケージと2.5Dパッケージを組み合わせた3.5Dのパッケージング技術を開発している。その一端を、ECTC 2024で公表した(論文番号2.3)。公表したパッケージ断面の例は、パッケージ基板にシリコンの小片(「EMIB:embedded multi-die interconnect bridges」とIntelは呼称)を埋め込んでミニダイ間の配線ピッチを狭くするとともにシリコンダイ間の距離を縮める2.5Dパッケージング技術と、ミニダイを縦に積層する3Dパッケージング技術を組み合わせたもの。ミニダイの積層接続にはマイクロバンプあるいはハイブリッド接合(HB:hybrid bonding)を駆使する。

講演では、3Dパッケージングの要素技術であるHBI(Hybrid Bonding Interconnect)の研究成果を述べた。チップとウェハを接続する「CtoW(C2W)」タイプのHBI技術を改良し、量産可能な水準で接続ピッチが3μmと狭いHBI技術を開発してみせた。

開発にあたっては、テスト用のミニダイとミニウェハを作成し、ミニダイとミニウェハの間でハイブリッド接合を実施した。ミニダイの大きさは6.2×7.7mmである。ミニウェハには横方向に4枚、縦方向に2枚のトップダイを搭載できる。ハイブリッド接合によって接続部はデイジーチェーン状となる。デイジーチェーンを作るのは、数多くの接合をつなげることで、全体の電気的特性を測定しやすくするためだ。

25,600のデイジーチェーンで均一な抵抗値を確認

トップダイは64のデイジーチェーンを作り込んである。400枚のトップダイで4端子法によってHBI後の電気抵抗を測定した。合計で25,600のデイジーチェーンに対し、抵抗の変化はほとんどなかった。また位置合わせの誤差は400枚のトップダイに対して0.5μm以下にとどまった。

信頼性試験も実施した。uHAST(unbiased Highly Accelerated Stress Test)、温度サイクル(TC:Thermal Cycle)試験、高温放置(HTS:High Temperature Storage)試験である。uHASTの試験条件は110℃、85%RH、275時間で78個のサンプルがすべて良品のままだった。温度サイクル試験の条件は低温側が-55℃、高温側が125℃、15分ずつで750サイクルである。80個のサンプルはすべて試験を通過した。高温放置試験の条件は165℃、336時間で、80個のサンプルから不良品はまったく出なかった。

AMDとIntelの発表から伺えるのは、3Dパッケージングではハイブリッド接合による接続を重視していることだ。シリコンダイ同士の接続密度を飛躍的に高める技術としては、HBIが最も有力視されている。一方で技術的な難しさもかなりのものだ。このためECTC 2024では、ハイブリッド接合に関する発表が非常に活発だった。今後の発展を強く期待したい。

![全科実例による 社会保険歯科診療 令和8年版 [ 歯科保険研究会 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8557/9784263448557_1_5.jpg?_ex=128x128)

![幸せな小さな台所 夫婦ふたり、狭いキッチンの食事と収納 [ chiemi ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3555/9784046603555_1_2.jpg?_ex=128x128)

![DIE WITH ZERO 人生が豊かになりすぎる究極のルール [ ビル・パーキンス ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9687/9784478109687.jpg?_ex=128x128)

![ベー革(9) (ゲッサン少年サンデーコミックス) [ クロマツ テツロウ ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5940/9784098545940_1_23.jpg?_ex=128x128)

![日本史探偵コナン 全12巻セット [ 青山 剛昌 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9230/9784092969230.jpg?_ex=128x128)

![ブティック [ 池井戸 潤 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4697/9784478124697_1_3.jpg?_ex=128x128)

![改訂 障害者相談支援従事者研修テキスト 初任者研修編 [ 日本相談支援専門員協会 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1444/9784824301444_1_7.jpg?_ex=128x128)

![週刊ビッグコミックスピリッツ 2026年25号【デジタル版限定グラビア増量「いぎなり東北産」】(2026年5月18日発売号) 【電子書籍】[ ビッグコミックスピリッツ編集部 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9237/2000020609237.jpg?_ex=128x128)