ニュース

超低電圧でもデータを保持できるSRAM技術、東京科学大学が開発

2025年11月10日 15:21

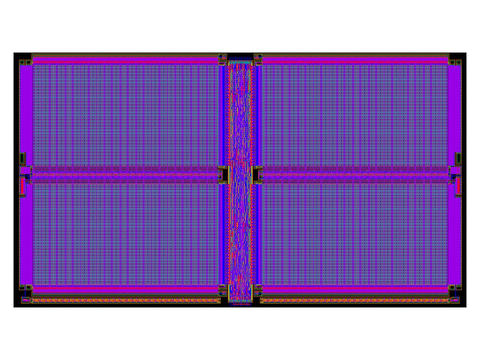

東京科学大学の研究チームは10月31日、0.2V程度の超低電圧でデータを保持できる新たなCMOSメモリ技術を開発したと発表した。この技術を活用すれば、SRAMの待機電力を不揮発性メモリ並みに削減できるとしている。

SRAMは、マイクロプロセッサやAIアクセラレータなどに用いられているメモリ。通常6つのトランジスタからなる記憶セルを用いているが、リーク電力の削減が難しく、ロジックシステムの待機時電力やAIアクセラレータのエネルギー効率改善に向けて課題となっている。

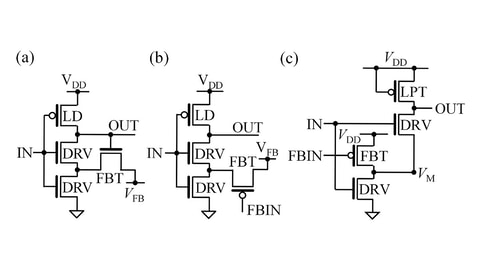

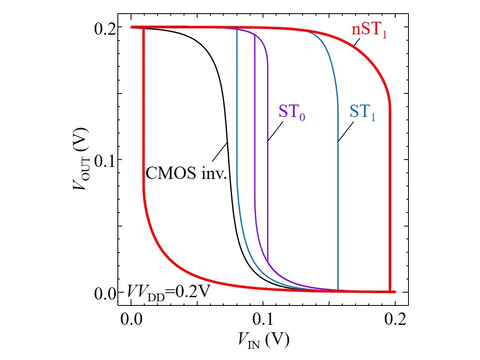

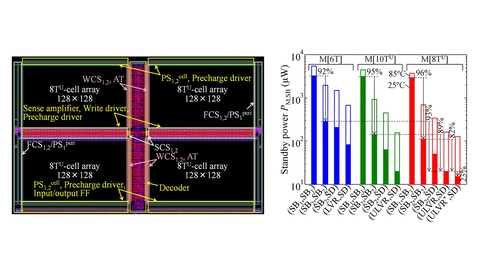

研究グループでは、伝達特性を示すヒステリシスを低電圧でも最大限に拡大できる新型インバータを提案。これを用いて、0.2Vの超低電圧でデータを保持できる新型のULVR-SRAMセル(超低電圧リテンションSRAMセル)を開発した。従来のSRAMセルと比べ、ロードトランジスタとパストランジスタを1つに統合できるため、少ないトランジスタ数でセルを構成できるという。

開発したセルを解析したところ、動作電圧0.2V/動作温度25℃および85℃の環境において、従来の低電圧セルよりもはるかに強いノイズ耐性があり、0.16Vでも安定してデータを保持できることが確認できたという。また、開発したセルを使った8kBマクロのシミュレーションでは、ULVRモードを用いた場合、従来セルのSRAMマクロと比べて93%待機時電力を削減できることが分かったとしている。

グループでは、今回開発した技術により、SRAM上のデータを保持しつつ待機時電力を不揮発性メモリ並みに削減できるため、IoTデバイスやエッジデバイスへの応用が期待できるほか、低電圧でのSRAM動作を生かしてPIM(Processing-in-Memory)型アクセラレータの高性能化も図れるとしている。

![【中古】DELL U2515H [25インチ/2560x1440(WQHD)/IPS/非光沢/DP/mDP/HDMIx2] (2017)【秋葉2号】保証期間1週間 製品画像:9位](https://thumbnail.image.rakuten.co.jp/@0_mall/janpara/cabinet/itemimg_tempostar/shop67_39/108191606-67_1.jpg?_ex=128x128)

![遊☆戯☆王 オフィシャルカードゲーム デュエルモンスターズ 公式カードカタログ ザ・ヴァリュアブル・ブックEX4 (Vジャンプブックス) [ Vジャンプ編集部 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8166/9784087798166_1_4.jpg?_ex=128x128)

![ファイブスター物語 19 [ 永野 護 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3336/9784041173336_1_10.jpg?_ex=128x128)

![ストライヤー生化学 第10版 [ J. M. Berg ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0778/9784807920778_1_8.jpg?_ex=128x128)

![筋肉が全て 健康・不老・メンタル、人生のすべてが変わる唯一の方法 [ ガブリエル・ライオン ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0507/9784478120507_1_3.jpg?_ex=128x128)

![細木数子 魔女の履歴書 新装版 (講談社文庫) [ 溝口 敦 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8276/9784065428276_1_4.jpg?_ex=128x128)

![あんしんえほん はじめての「よのなかルールブック」 [ 高濱正伸 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1007/9784284001007_1_3.jpg?_ex=128x128)

![謎の香りはパン屋から2 [ 土屋うさぎ ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6502/9784299076502_1_2.jpg?_ex=128x128)

![[新品]ゴールデンカムイ (1-31巻 全巻) 全巻セット 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0021/m9880472800_01.jpg?_ex=128x128)