大原雄介の半導体業界こぼれ話

NPUって要するに何?AI処理でGPUが限界を迎え、専用プロセッサが台頭する理由

2026年4月17日 06:03

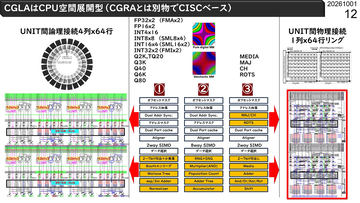

2月のLENZOというスタートアップが開発した新アーキテクチャのプロセッサの特集記事掲載後、編集氏より「CGLAとCPUの違いはよく分かったのですが、GPUとNPUと何が違うのって説明が抜けてる気がしてまして……」という質問がやってきた。

さすがにその記事では要らないと思って落としたのだが、そもそもNPUというかAIプロセッサって何よ?という定義がそもそも曖昧なので、それは分からない人には分からないであろう。NPUとGPUの違い、というよりもNPUというかAIプロセッサの定義なるものを示しておくことは有用に思える。

といっても、実のところAIプロセッサなるものの定義にあたるものは事実上存在しない。しいて言えば「AI(Artificial Intelligence:人工知能)に必要な処理に特化したプロセッサをAIプロセッサと呼ぶ」という以上の定義が存在しないからだ。といってもこれは全然定義になっていないので、もう少し分かりやすく説明してみたいと思う。

というか、この記事をAI WatchではなくPC Watchで書いてるあたり、自分でもどうかとは思わなくもないのだが。

1. AIが利用可能になった契機

そもそも近年のAIの興隆は、実は“3期目”である。1期目は1956年~1974年頃で、2期目は1980年~1987年あたり、3期目が1993年以降になる。1期目/2期目ともにAIが失速したのは、やはり当時の演算性能が求めるレベルに達しなかったという点が大きい。これが1993年になると、演算性能の飛躍的な向上もあって「従来のアルゴリズムのままでもある程度使える」ことが発見される。IBMが「Deep Blue」を構築し、当時のチェスの世界チャンピオンであるGarry Kimovich Kasparov氏を打ち破ったのは、1997年のことだ。

もっともこの時のDeep Blue、32ノードのRS/6000システムに専用VLSIを512個搭載し、毎秒2億手の先読みをするという、ある意味力業に近い所業であり、まだ一般的とはいえなかった。

これがもう少し一般的というか、研究者の手に届くようになったきっかけは2012年のILSVRC(ImageNet Large-scale Visual Recognition Challenge)にトロント大が出した「AlexNet」というConvolution(畳み込み)ベースのニューラルネットワークが非常に良い成績を収めて優勝したことである。これを受けて、それまでほかの方法を模索していた研究者が一斉にCNN(Convolutional Neural Network)に殺到。あっという間にCNNが第3期のAIの興隆の中心となった。

ここでそもそもCNNとは何か?という話であるが、元々AIを実現するにあたり、人間の脳の構造を模式化しようと考えるのはごく自然なことである。理論的な仕組みとしては、1958年にFrank Rosenblatt博士が発表した「The Perceptron: A Probabilistic Model for Information Storage and Organization in the Brain」という論文がその基礎となっている。これは、脳の仕組みをパーセプトロンという数値演算で置き換え可能な形式で模すための仕組みを構築した。

これを利用して、実際にAIを実現しようという試みもいろいろあった。たとえば第2期にあたる1983年にアメリカで創業したThinking Machinesは、1bitプロセッサ(3bit入力、2bit出力)を65,536個並べた「CM-1」というシステムを1985年に発表している。このプロセッサがそれぞれ脳のニューロンに相当し、プロセッサ同士の接続が脳のシナプスとなる仕組みである。このシステムの上でパーセプトロンを利用したシステムを実装しようとしたわけだが、65,536個のプロセッサは当時としては大規模ではあったものの、人間の脳に比べるとあまりに貧弱過ぎた。結果、CM-1やその後継製品は、AI向けの研究ではなくむしろHPC向けのシステムとして利用されるに留まっている。

ではなぜCM-1では不可能だったことがトロント大の研究で可能になったか?と言えば、演算性能が飛躍的に向上したから、ということに尽きる。CM-1は65,536個の1bitプロセッサにそれぞれ4KbitのSRAMが搭載されており、最初のプロトタイプの動作周波数は4MHzほど。システム全体での性能は、32bitの加算を行なった場合に概ね1,000MIPS、メモリ帯域は最低32Mbps、典型値で1Gbpsほどとなっていた。

これに対しトロント大が利用したのはおそらくFermiベースのNVIDIA Teslaと思われるのだが、その中でもローエンドにあたるC2050でも演算性能は1.03TFlops、メモリ帯域は最大144GB/secであり、CM-1と比較して桁違いに性能が向上している。AlexNetの構築にあたってはこれを2枚用意し、2週間ほどぶん回したとされている。同じことをCM-1でやろうとしたら、70年以上かかる計算である。要するに演算性能が大きく向上したことで、現実的に処理が可能になったというわけだ。

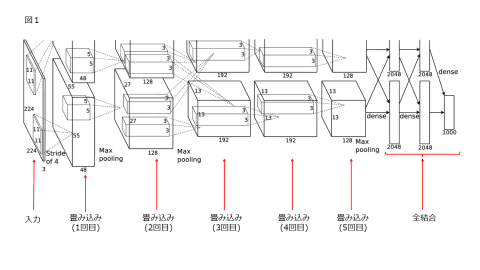

2. CNNで必要とされること

せっかくなので、AlexNetを例にもう少し説明を進めたい。図1はAlexNetの構造図である。この図で、データは左から右に流れていく格好だ。まず一番左が入力画像で、これは224×224ピクセルのRGBデータである。ここから96種類のフィルタ(11×11ピクセル)を介して、55×55に畳み込みを行なう。この畳み込み、96種類のフィルタごとに結果が出てくるので、55×55の出力が全部で96個ある。この結果に対して活性化関数と呼ばれる処理を施し、次いで最大値プーリングと呼ばれる処理を行なう。

【12時40分訂正】記事初出時、図1が誤っておりました。お詫びして訂正します。

ついでその結果に対して再び畳み込み、活性化関数、最大値プーリングを行なう。その結果に対して、さらにに3回の畳み込みを実施。その後で3度目となる最大値プーリングを実施した後で、全結合という処理を経て最終的に出力が出てくる格好だ。このAlexNetの目的は、入力画像をClassification(分類)するのが目的で、出力候補が1,000種類用意されている関係で、全結合の出力が1,000個になる格好だ。

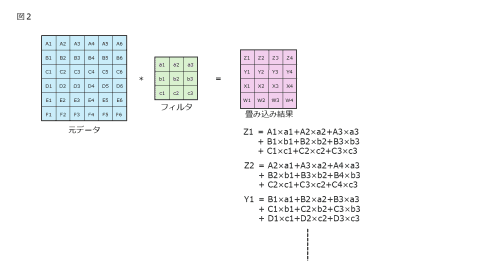

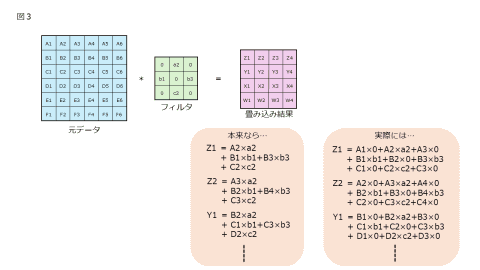

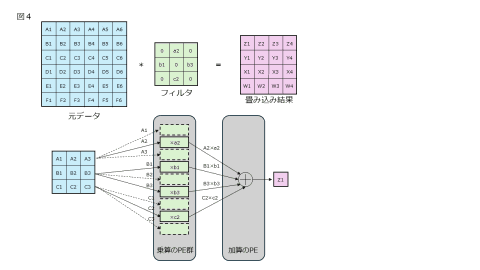

個々の処理の説明はしないが、まず畳み込みというのは図2のような計算になる。これは6×6の入力データに対して3×3のフィルタを適用するケースだが、出力は4×4になる。ただしこの4×4の出力に対して、それぞれ9回の乗算+全体の加算が必要になるので、この畳み込み結果を得るためには全部で144回の乗算+16回の加算が必要になる計算だ。

ちなみに加算が少ないのは、まとめて複数の加算を行なえるような仕組みを持った計算機がAI向けでは一般的だからだが、それがないと加算も毎回8回、トータルで128回必要になる。先の図1で畳み込みの1回目は224×224の入力に対して11×11のフィルタを適用し、最終的に55×55の結果を得る(ここではStride of 4、つまり4つおきに計算を行なっているから55で済んでいるのであって、普通にやると出力は216×216になる)わけだが、この際に必要な計算回数は乗算が11×11×55×55=366,025回、加算が363,000回になる。しかもこれを96種類のフィルタごとに行なうから、トータルでは35,138,400回の乗算と34,848,000回の加算である。

毎サイクル1回の加算ないし乗算が可能なCPUが1GHzで動くとすれば、0.07秒ほどで済む処理ではあるのだが、問題はこれはあくまでも第1層の処理でしかないことだ。この後も延々と畳み込みが続くわけで、トータルの計算量は壮絶なことになる。

もっと悪い(?)話をすると、このAlexNetは、その後に出てきたさまざまなCNNの中ではかなり軽量な部類に入ることだ。2015年にMicrosoftはResNetと呼ばれるものをILSVRCで発表するが、こちらは誤り率が3.57%(AlexNetは16.4%、一般人は5.1%)と人間を超えたと評されたが、このResNetは152層ものネットワーク構成になった。いうまでもなく計算量はすさまじい。

3. GPUがもてはやされた理由

AlexNetの構築や学習(2枚のGPUカードで2週間掛かったらしい)にGPUカードを使ったのは、当時としては必然であった。要するにバカみたいな計算量を現実的な速度で処理できるものがGPUしかなかった、というそれだけの理由である。

NVIDIAはGPUを汎用的に使えるAPIとしてCUDAを2007年に発表、これを利用してHPCなどの用途向けにTeslaシリーズのサーバー向けGPUをやはり2007年にラインナップする。AMDもKhronos Groupが標準化を担ったOpenCLに対応する形でサーバー向けGPUのラインナップを開始する(FireProシリーズ)。

ここでGPUを使うことは、いくつかのメリットがあった。1つは演算の性質が非常に並列性が高かったことだ。図2を例に取れば、Z1とZ2、Y1の計算はお互いに独立して行なえる。GPUで採用されているSIMT(Single Instruction Multi Thread)というメカニズムは、命令そのもの(ここで言えば3×3の乗算とその結果の加算)そのものは共通で、扱うべき対象のデータだけスレッドごとに異なる、という仕組みだ。SIMTはSIMDに似ているが、異なるのは命令単位での同期ではなくスレッド単位の同期になっていることだ。図2で言えば、Z1~Z4、Y1~Y4、X1~X4、W1~W4の16個の演算をそれぞれ別々のスレッドに割当て、これを同時に処理することができる。もちろん、実際にはそもそも扱うべきデータサイズがもっと大きくなるが、利用できるスレッドの数もやはり大きい。

たとえばFermiの場合は24,576スレッドが利用可能だ。もちろん同時に2万あまりのスレッドを動かすことはできない(のでほとんどのスレッドは自分の処理の番が回ってくるのをじっと待ってる)が、メモリアクセスなどの待機時間もあることを考えると、このぐらいの数のスレッドがあれば常に稼働状態を維持できるというわけだ。

もう1つのメリットは、必要なメモリ量がそれほど多くないことだ。図2に戻ると、元データ、フィルタ、結果が全部FP32だとしても、必要なデータ量は244Bytesでしかない。それでいて計算量は272回(加算が144回の場合)である。つまり1Flops/Bytes未満の帯域で十分に間に合うわけで、それほど大量のキャッシュを持たないGPUでも無理なく実行できた。

図1のAlexNetの第1層の場合でも、入力が224×224で196KB、Filterが11×11×96で45.4KB、出力が55×55×96で1,134.46KB。合計で1.3MB程度であり、これは十分にL2キャッシュに収まる。一方で計算量は先に示したように合計7,000万回ほど。計算量と必要なメモリ(キャッシュ)サイズのバランスを考えると、Compute Intensiveな構成になっていることが分かる。(今もそうだが)この当時のGPUは計算性能に対してメモリ帯域が必ずしも十分ではなかったが、CNNに関して言えば工夫すれば効率よく処理ができそう、というめどが立っていた。

なによりGPUは入手性が非常に良い、というのが最大のメリットだった。2012年のILSVRCの発表を見た研究者は、一斉にGPUを入手して自身でも研究を始めることになる。結果、すぐにNVIDIAのTeslaが入手困難になり、コンシューマ向けのGeForceを買い漁る動きまで出るようになったわけだが、なにしろPCショップに行けばGeForceが買えるというのは、AI研究者にとって非常に都合が良かった。そしてOpenCLよりCUDAの方が使いやすかった(なにしろAlexNetがCUDAで記述されており、研究者もこれに右に倣えした)ことで、一気にAIといえばCUDAという流れができた。あとは拡大再生産である。

NVIDIA自身も2014年のGTCの基調講演の第3部をまるまるAI(当時はAIではなくML: マシンラーニングと称していた)に充て、さらに第4部ではCUDAベースの自動運転車のデモを行なうというほどに力を入れていることを明らかにした。AMDなど競合がAI/MLを言い始めるのはもっとずっと後の話であり、かくして「AIを使いたければNVIDIAのGPU」という流れができたことになる。

4. GPUでのAI処理

ただここで注意されたいのは、GPUはAIに向いた特徴を持っていたが、AI向けに設計されていたわけではないことだ。これはNVIDIA自身も良く分かっており、アドホック的にAI向けの特徴を強化していく。

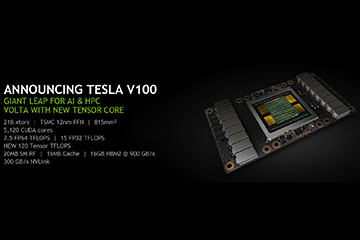

まずはTensor Coreの増設だ。CNNにおいては、畳み込み演算が全体の演算の9割以上を占めるケースも珍しくない。こうしたものをもっと効率的に処理するためには、通常の演算あるいは1次元のSIMDではなく、行列などの2次元演算に特化した計算ユニットを搭載する方が賢明である。この発想に基づき2017年にVoltaで搭載されたのがTensor Coreである。

次がデータ型の変更である。CNNにおいては、1個1個の演算精度を上げるよりも、トータルの演算性能の方が最終的な結果が向上することが研究によって確かめられている。つまりFP64を使う代わりにFP32に留めて演算性能を2倍する一方、2倍のサイズのネットワークを実行するようにすれば、同じスループットでもより良い結果が得られるし、もっと小さくFP16/BF16とかFP8というように、個々の演算精度を落としても、その分大規模なネットワークを構築すればさらにに良い結果が得られるというわけだ。

かくしてFP32の代わりにTensor FP32という型や、数値演算ではこれまで使われてこなかったFP16/BF16といった型、さらにはFP8/FP6などを経て最新のBlackwellではFP4のサポートが追加されている。単純にFP64の16倍とはならない(ハードウェア的にデータパスの最適化などの問題があるから)とはいえ、FP4のサポートで大幅な性能向上が実現した(*1)。

(*1) 実際にはFP64などはもうハードウェアでのサポートが削られ、ソフトウェアで実行している部分があるため、Blackwell世代以降急激にFP64の性能が落ちているので、それを勘案するとFP4の性能はFP64の16倍では利かなくなってるのだが。

ただし大規模なネットワークを利用するということは、それだけメモリを食うという話でもある。データ幅が半減して、その分ネットワークの規模が2倍で収まっている限りにおいてはメモリ不足にならないはずだが、実際には2倍で利かない勢いでネットワークが大規模化している。またAlexNetのような小規模なネットワークならL2で収まったが、その後に出てきたネットワークはいずれもサイズだけでなく層数という意味でもはるかに大規模化しているので、どっちみち大量のメモリアクセスが発生する。これはメモリ容量とメモリ帯域の両方の面で強化が必要という話であり、NVIDIAはこれに対してHBMメモリの搭載で対応する。

ただここに来ていろいろ行き詰まりが見え始めているのも事実だ。まずは電力問題。Ampere世代のA100で250W、Hopper世代のH200で700W、Blackwell世代のB300で1400WというTDPは、データセンターでの電力供給に支障をきたす数値であり、NVIDIAはそれもあって2025年度から800V給電を強力に推し進めている。というのは先日発表されたVera RubinベースのNVL144はラックあたり120~140kWとされるが、次世代のRubin Ultraを搭載するNVL576はラックあたり600kWとされており、従来の100~200V給電では流れる電流量が大きすぎるためである。

またLLMとかAgentic AIといった新しいトレンドへの対応に苦慮しているのも事実である。SIMTという構造上、なるべく多数のデータをまとめて処理するほど実効効率が上がる。バッチサイズ(Batch Size)と称されるが、LLMで言えばプロンプトから入力される文字というか文章を、どれだけ並べて一度に処理するかという数字がある。GPUではバッチサイズ大きいときには効果的だが、小さくなると途端に遅くなるというか性能が上がらなくなる。

LLMに関しては2025年にNVIDIAは分離型推論を提唱、Dynamoと呼ばれる新しいフレームワークをオープンソースで公開し、これを利用して実装する方向を示していた。このDynamoではLLMの推論をプリフィルとデコードという2つのステージに分解し、プリフィルを従来のGPUで、プリフィルを新しく登場するRubin CPXと呼ばれるGPUで処理することを目論んでいた。

ところが今年になってこの計画は白紙化され、プリフィルは従来のRubinで実施。代わりにデコードを「Groq 3」で実施することを3月のGTCで発表した。2025年10月にはロードマップで「CUDA Everywhere」を謳っていたのに、半年後に非CUDA対応のプロセッサを組み入れているあたりに、同社のGPUの限界が見える。

もう1つ挙げておくと、そもそもSIMD構造ではSparsity(疎行列)への対応が困難である。疎行列というのは、行列の要素の中に「0」があるものだ。図3は図2の変型版で、フィルタに0となる要素があるケースだ。この場合、本来なら計算は中央下のように大幅に節約できるはずだが、実際には右下のように無駄に0の乗算と加算が入ってしまう。これを省ければより高効率に計算ができるわけだが、これは通常の行列計算で実装するのは難しい。

NVIDIAはいくつかの疎行列の対応策を打ち出しているが、たとえばAmpereで導入された疎行列対応というのはフィルタの0の要素をあらかじめ検出して、その要素を省いたCompressed Matrix Formatなるものを生成、これを利用して畳み込みを行なうことで効率を上げるという仕組みである。逆に言えば、元データが疎だと効果がない(データを毎回圧縮する位なら、圧縮せずにそのまま処理した方が早い)。致命的な問題というわけではないが、欠点の1つであることは間違いない。

5. AIプロセッサ/アクセラレータというもの

2010年台前半から、AIプロセッサなりAIアクセラレータというものの開発が始まった。正確に言えば、2010年前半のものは、元々はメディアアクセラレータだったりDSPだったり、と必ずしもAIを目指したものではなかったが、途中からAIマーケットの興隆にあやかるべくAI向けに路線変更したものが多い。

一方で2010年台後半以降になると、GPUを利用してのAIの欠点や弱点などが次第に露呈してきたので、そこをカバーできるものであるとか、GPUが不適当なマーケット向けなどにAI Processor/Acceleratorを企画するメーカーが急速に増えていった。当然狙うターゲットによって構成は著しく異なるのだが、しいて特徴を挙げるとすれば

AI演算に超絶特化

GPUは(だんだん怪しくなってきてはいるが)一応汎用の計算ができるようになっている。データ型もFP4とかFP8/BF16などだけでなくInt 4/8/16/32とかFP32/FP64もサポートしているし、単なる四則演算以外もカバーしている。

さすがにビット操作とかまでは入っていないが、一応条件分岐は可能だし、割と汎用の数値演算も可能になっている。対してAIプロセッサ/アクセラレータは、もうサポートするデータ型に対する畳み込みと活性化関数くらいしかサポートしていない、というものが少なくない。そもそも実行制御すら放棄しており、アクセラレータ的に「あるデータをメモリに書き込んでから、トリガーなどで実行を指示すると、一定サイクル後に結果が出てくる」的なものも少なくない。

ただ、これだと本当に応用が利かないことが多いため、実際には汎用のCPUコア(ここでRISC-Vコアを使うことが非常に多いのはライセンスやロイヤリティの関係だけでなく、コアに手を入れられることが大きいのだろう)に、AI演算向けのアクセラレータを組み合わせる、という構造を取るメーカーが非常に多い。

実装方法はいろいろあるが、命令パイプラインに手を入れ、AI命令のみAIアクセラレータ側に制御を渡すという実装のことが多い。これなら、将来新しいアルゴリズムなどが開発され、既存の演算ユニットでカバーできなくなった場合でも、(性能は落ちるにせよ)汎用CPUコアのALUなどを使ってカバーできる。

データフロー

長らく論文などでその有用性が論じられつつもなかなか商用製品で実装されなかったデータフローだが、AIプロセッサではこれを搭載していないのが少数派では?と思うほど広く普及している。

データフローはLENZOの記事でも簡単に説明しているが、要するに複数の実行単位(PE:Processor Elementなんて呼ぶことが多い)が順につながっている際に、「前の段のPEの出力が到着したら、それを入力として処理を開始し、終わったら待機に入る」仕組みである。これを生かすと、たとえば疎行列を生かした畳み込みが非常に簡単に実装できる(図4)。係数が0のPEはそもそも入力を受け取らない(から動かないので省電力になる)し、結果も出てこないから無駄に加算も発生しない。

もっと積極的なデータフローの使い方としては、そもそもの処理の流れを変えることができる。GPUというかSIMTの場合、原則として処理のプログラム(NVIDIA用語ではKernel)はすべてのスレッドで共通である。原則、というのはもちろん例外があるからで、複数のスレッドを束ねた単位(これをWarpと呼ぶ)ごとにKernelを変更することは不可能ではない。ただ容易に可能か?というと結構大変である。

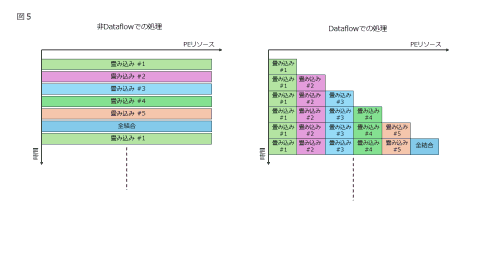

とりあえず説明の単純化のために、全スレッドでKernelは共通だとする。先のAlexNetを例に、これも説明を簡単化するために処理は5つの畳み込み層(活性化とかMax Poolingは畳み込みの一部とする)+全結合の6ステップだとしよう。GPUなどの非データフロー方式(DSPとか汎用CPUもここに含まれる)では、図5左側のような形で処理を時分割して畳み込み、#1→#2→……と進めていくことになる。ただし処理ごとに切り替えが発生するから、オーバーヘッドは少なくない。

一方データフローでは図5の右側のように、ちょうどCPUのパイプラインのように処理を分割してそれぞれの処理に割り振ることが可能である。この方式の場合、それぞれの処理の負荷に応じて割り振るPEの数を変更することで、負荷の最適化が図りやすいし、何より個々のPEの処理を変更する必要がないから、オーバーヘッドも最小である。もしPEにゆとりがあるなら、複数種類のネットワークも同時に動かすことが可能である。こうした柔軟性は、AIプロセッサ/アクセラレータ向けに非常に好ましいものである。

CIM(Compute In Memory)/PIM(Processor In Memory)

名前はともかく、理屈は同じである。

特に消費電力の観点で見た場合、プロセッサ内部で一番消費電力が多いのはデータの移動である。要するにメモリから演算器までデータを移動し、そこで演算して結果をまたメモリまで戻す、という流れで演算器とメモリの間のデータ移動に要する電力が一番大きい。

そこでいっそメモリと演算器を一体化してしまえば消費電力が減るだろう、というわけだ。ちなみにこの発想、古いところで言えばNeoMagicの「APA」や、Connex Technologyの「CA1024」とか、まぁチャレンジして消えていった例は少なくないのだが、これもAIと意外に相性が良い。

というのはこうしたPIM/CIM、エリア面積の観点からあまり複雑なALUを入れにくいのだが、畳み込み演算だと、実質加算と乗算だけで実装が楽である。そして演算の9割以上が畳み込み演算ということは、ここの消費電力を減らすと全体への影響が非常に大きくなる。費用対効果が高いわけだ。

これに関してはSamsungがHBMに、SK HynixがGDDRメモリにそれぞれプロセッサを組み込んだAIアクセラレータを試作しており、どちらも商用化に向けて現在開発を続けている。Intelも、CPUのL3キャッシュの脇にプロセッサを搭載するという発表をVLSI Symposium 2022で行なっていたりする(あくまで研究レベルの話で商用化を睨んだものではなさそうだが)。また後で説明するアナログプロセッサも、原理的にはCIM/PIMの一種として捉えることができるだろう。

汎用プロセッサを実装するにはあまりに回路規模に制約がありすぎて無理なCIM/PIMだが、畳み込み演算のアクセラレータとしてはかなり実用性が高いと見做されており、次に説明するSRAMに関してもCIM/PIM的な実装を考慮しているケースが少なくない。

大量のSRAM

CIM/PIMとも絡む話だが、AIプロセッサ/アクセラレータではとにかく演算性能を引き上げるために大量のPEを搭載する。さすがに動作周波数を引き上げるという選択肢は、基本的にはない(性能/消費電力比が急激に悪化するため)。ということはそれだけメモリが必要になるわけだが、オフチップのDRAMは帯域も低いしレイテンシも大きく、そしてオフチップでのデータの移動を伴う=消費電力が大きくなるから敬遠される方向にある。結果として大量のSRAMを搭載する方向に進んでいる。

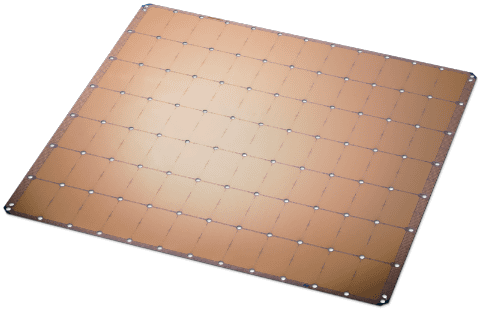

多分、この方向の極北に位置するのが、Cerebrasの「WSE(Wafer Scale Engine)」で、初代の「WSE-1」は40万個のPEと18GBのSRAM、最新の「WSE-3」は90万個のPEと44GBのSRAMを搭載する。もちろんこんなものがチップ1個で収まるわけもなく、WSE-3は84個のダイで構成される21.5cm角のチップ(?)である。

概してAIプロセッサ/アクセラレータ(特にデータセンター向け)の場合、大規模なチップに大量のSRAMを搭載する方向にある。ちなみにこのSRAMはScratchPad(スクラッチパッド)、つまりキャッシュではなくPEから明示的にアクセスできるメモリ領域として置かれるのが一般的である。また個々のPEのそばにSRAMを配して、そのローカルSRAMを相手に処理を行なうことでデータ移動を減らすという、CIM/PIM的な配慮がなされていることが多い。

超高速DRAM

超高速DRAMとは、いうまでもなくHBMのことである。消費電力も価格も上がるが、通常のDRAMよりも帯域が確保できる。特にLLMの急速な普及と発展のおかげ(?)で、もうオンチップSRAMではどうにもならないところに来てしまっている。結果として、最近のAIプロセッサはダイあたり2~4つのHBMを実装するのがごく当たり前になってしまっている。現状HBMは一部のCPUで実装例はあるものの、ほとんどがAI向けプロセッサかAI向けGPUになっており、これもAIプロセッサの特徴といえるだろう。

アナログプロセッサ

アナログプロセッサは、データセンター向けというよりもエッジ向けのAIプロセッサであるが、アナログ回路で畳み込み演算を実施することで省電力化と高性能化/低価格化を同時に実現している例がいくつかある。

たとえばMythicはフラッシュメモリを利用したメモリセルを可変抵抗として扱うことで、DACでアナログ信号化した入力データの乗算と加算をアナログ回路で行なうというアイディアだし、Aspinityの「AnalogML」はRAMP(Reconfigurable Analog Modular Processor)なるエンジンでやはりアナログベースでの演算を可能にするとしている。

データセンター向けにはちょっと使いにくい構成だが、消費電力が数Wという非常に低いことと、アナログ回路ということで比較的古いプロセスで構築できる(ので製造コストが安い)ことなどを特徴として販路を拡大しようとしている。最近はこの延長(?)として、光ファイバーベースを利用したAIアクセラレータを開発しようとしているイスラエルのCogniFiberなどもちょっと話題を集めている。

……といったあたりだろうか?

一番頭にちょっと触れたが「GPUとNPUと何が違うのって説明が抜けてる」というので書いたらこの始末である。AIプロセッサの定義は難しい。

![\楽天ランキング1位 / デスクトップパソコン 一体型pc 一体型パソコン タッチパネル[第13世代CPU] オールインワン All-in-One デスクトップパソコン 一体型pc 23/27型 フルHD液晶一体型 インテル Core 7 Windows 11搭載 16G PSE認証済 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/enmachihiguchishouten/cabinet/dn/dn011/dn011.jpg?_ex=128x128)

![【期間限定 P10倍】WINTEN モバイルモニター 15.6インチ テレワーク/デュアルモニター/サブモニターに最適!ゲーミング 1080P FHD IPSパネル 軽量 薄型 非光沢 カバー付 ミニPC Switch iPhone Type-C/HDMI接続 [1年保証] WT-156H2-BS 5523 製品画像:10位](https://thumbnail.image.rakuten.co.jp/@0_mall/win10/cabinet/monitor/imgrc0112809238.jpg?_ex=128x128)

![●【中古】 黄昏流星群 1-75巻 セット [小学館 ビッグコミックス] [レンタル落ち] [コミック] [漫画] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/youing-gaba/cabinet/13259209/imgrc0120713365.jpg?_ex=128x128)

![10年先のわたしをつくる、家と時間 [ Emi ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2433/9784087902433_1_2.jpg?_ex=128x128)

![完訳7つの習慣 人格主義の回復 [ スティーヴン・R.コヴィー ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0246/9784863940246.jpg?_ex=128x128)

![はる!たまごっちコネクション まるごとシールブックDX [ 小学館 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6110/9784097356110_1_12.jpg?_ex=128x128)

![30時間でマスターWord&Excel2021 [ 実教出版企画開発部 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9398/9784407359398.jpg?_ex=128x128)

![よくわかる Excelではじめるデータ分析入門 関数・グラフ・ピボットテーブルから分析ツールまで [ 富士通ラーニングメディア ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1480/9784867751480_1_2.jpg?_ex=128x128)

![よくわかる Word 2024 & Excel 2024 & PowerPoint 2024 Office 2024/Microsoft 365 対応 [ 富士通ラーニングメディア ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1527/9784867751527_1_5.jpg?_ex=128x128)

![手を動かして学ぶ Google AppSheet ノーコード開発入門 [ イルカのえっちゃん ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4727/9784863544727_1_4.jpg?_ex=128x128)

![ゼロから学ぶ はじめてのWordPress 第2版 [バージョン6.x対応] 簡単にできるWebサイト制作入門 [ 泰道 ゆりか ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6754/9784815626754_1_6.jpg?_ex=128x128)

![MOS Word 365&2019 対策テキスト&問題集 (よくわかるマスター) [ 富士通エフ・オー・エム(FOM出版) ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4301/9784865104301.jpg?_ex=128x128)