ニュース

NVIDIA、推論特化の「Groq 3 LPU」発表。Arm CPU「Vera」の詳細も

2026年3月17日 05:30

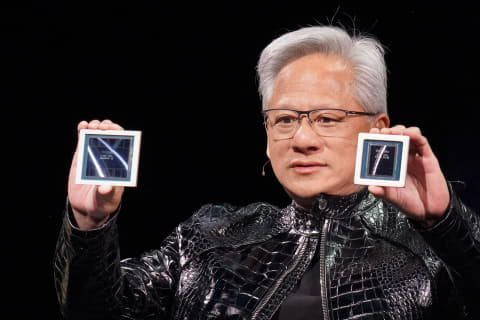

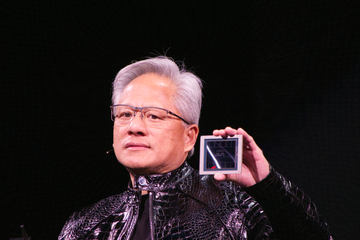

NVIDIAは3月16日(現地時間)から、同社のAIソリューション向け年次イベントGTC 2026を開催しており、初日の11時から13時までには同社 共同創業者でCEOのジェンスン・フアン氏による基調講演が行なわれた。

この中で注目を集めたのは、先日同社が非独占ライセンス契約を結んだばかりのGroqが開発したLPUを、同社のAIデータセンター向け製品などに統合し、提供すると明らかにしたことだ。

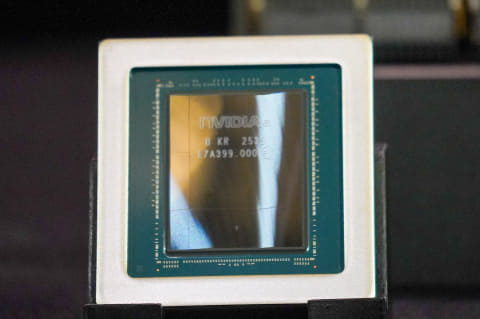

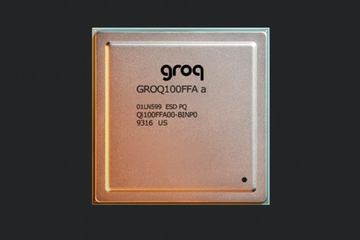

ライセンス契約が発表されたGroqの技術を応用したGroq 3 LPUが発表される

今回NVIDIAが発表したのは、「Groq 3 LPU」と呼ばれるAI推論アクセラレータになる。このGroq 3 LPUは、昨年(2025年)の暮れにNVIDIAと非独占ライセンス契約を結んだGroqの技術を応用したものだ。

Groqは低遅延で低消費電力なAI推論アクセラレータ「LPU(Language Processing Unit)」を開発してきた企業で、AI推論に特化することで、低遅延で高い電力効率を実現していることが大きな特徴になる。

LPUは、プロセッサの内部でのデータ処理がベルトコンベアのように順次処理されていく形になっており、チップ間でデータ移動などができるだけ起きないような構造になっている。また、オンチップのSRAMを搭載しており、メモリ遅延がDRAMにアクセスする場合に比べて少なく、外部メモリへのアクセスを大幅に減らすことができる。

CPUやGPUのようないわゆる従来型のプロセッサは、チップ間通信やメモリアクセスが多発するアーキテクチャで、それが消費電力増加の一因となっていたが、LPUでは両方とも減らすことができるため、同じ処理をさせても消費電力が圧倒的に少なくて済む。

今回NVIDIAが発表したGroq 3 LPUのスペックは以下のようになっている。

| Rubin GPU | Groq 3 LPU | 比較 | |

|---|---|---|---|

| メモリ | 288GB HBM4 | 500MB SRAM | 1/500 |

| メモリ帯域 | 22TB/s | 150TB/s | 7倍 |

| 性能 | 50PFLOPS(NVFP4時) | 1.2PFLOPS(FP8) | 1/25 |

| トランジスタ数 | 3,360億(ダイ)+2兆5,000億(HBM4) | 980億 | 約29%(ダイのみ) |

Groq 3 LPUは500MBのSRAMを搭載し、150TB/sのメモリ帯域を実現し、処理能力は1.2PFLOPS(FP8時)となっている。Rubinと比べると明白だが、メモリ容量は500分の1、性能は25分の1となっているが、逆にメモリ帯域は7倍と飛び抜けている。

また、ダイだけのトランジスタ数の比較でもRubinが3,360億であるのに対して、Groq 3 LPUは980億と3分の1以下となっている。トランジスタ数が増えれば増えるほど消費電力は増える(もちろんプロセスノードの微細化も考慮にいれる必要があるが)ことを考えれば、このGroq 3 LPUが少ない消費電力で動作することは容易に想像できる。

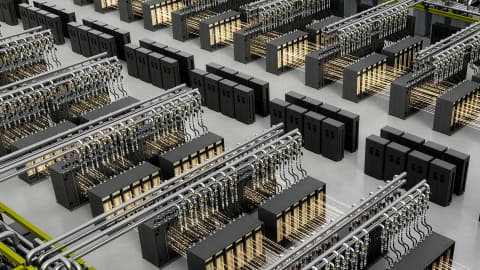

NVIDIAはこのGroq 3 LPUをラック単位で提供する。それが「NVIDIA Groq 3 LPX inference accelerator racks」(以下Groq 3 LPX)だ。

Groq 3 LPXは、Groq 3 LPUが256基ラック内に搭載されており、NVIDIAが1月のCESで発表したVera Rubinベースのラックサーバー「Vera Rubin NVL72」と並べて利用することを想定している。Rubinでより高いスループットが必要な超大規模モデルをカバーし、Groq 3 LPXでそこまで大規模ではないが低遅延と電力効率を必要とするアプリケーションをカバーする。

具体的にはBlackwellベースのNVL72だけと比較して、RubinベースのNVL72+Groq 3 LPXはスループットが35倍になり、費用対効果は約10倍になるとNVIDIAは説明している。

Veraの内部構造などが明らかに、256基にスケールアップした「NVIDIA Vera CPU racks」も発表される

NVIDIAは1月のCESで、新しいArm CPUとなる「Vera」、新しいGPUとなる「Rubin」を発表し、それを搭載したラックデザイン「NVIDIA Vera CPU racks」を発表した。

今回のGTCでは、さらにCPUのVeraの詳細を発表した。VeraはNVIDIAが自社設計したArmv9.2ベースの「Olympus コア」のCPUが88基搭載されている。Olympusコアは10ワイドの命令デコーダを搭載し、ニューラルエンジンを応用した分岐予測、1クロックサイクルあたりに2つの分岐予測が可能、さらにPyTorchに最適化された命令バッファなどの新機構が搭載されており、前世代となるGraceに比較して1.5倍のIPC(1クロックサイクルあたりに実行できる命令数)を実現している。

SOCAMM LPDDR5で実装されるメモリは1.5TBを搭載可能で、帯域幅は1.2TB/sとなる。従来世代に比べて2分の1の消費電力で、2倍の帯域幅を実現している。

また、第6世代のNVLinkに対応して、GPUとの接続時には1.8GB/sの帯域幅を実現しているほか、CPU間のNVLinkでは最大2つのCPUを接続することができる。

こうした特徴から、Vera CPU racksでは最大256基のVera CPUを1つのラックに格納することができる。それにより最大400TBのLPDDR5メモリ(300TB/s)、64基のNVIDIA BlueField-4 DPU(CPUへの負荷をオフロードできるネットワークアダプタ)などのスペックで、従来のGraceに比較して概ね倍の性能を実現することができる。

現在でも推論処理にはCPUが利用されている例が多く、そのほとんどがx86ベースのAMDないしはIntelのCPUになっている。NVIDIAとしてはその市場をVeraで奪いにいきたいという意向があると考えられ、VeraおよびVera CPU racksはそのための戦略製品になりそうだ。

![新品 LAVIE Direct N15 Slim Ryzen 5・16GBメモリ・512GB SSD・15.3型WUXGA液晶・Office Home&Business 2024搭載 [ルナグレー] 製品画像:3位](https://thumbnail.image.rakuten.co.jp/@0_mall/pchome/cabinet/07387522/imgrc0104101940.jpg?_ex=128x128)

![BARFOUT! SPECIAL EDITION EARLY SUMMER 2026 / TINY ESCAPE 渡辺翔太 [ ブラウンズブックス ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5189/9784344955189.jpg?_ex=128x128)

![[新品]出禁のモグラ (1-12巻 最新刊) 全巻セット 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0037/m2560431883_01.jpg?_ex=128x128)

![転生したらスライムだった件(32) (シリウスKC) [ 川上 泰樹 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7544/9784065437544_1_2.jpg?_ex=128x128)

![旅の短篇集 春夏 (角川文庫) [ 原田 宗典 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2110/9784041762110_1_8.jpg?_ex=128x128)

![プレゼント [ 伊坂幸太郎 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2574/9784101332574.jpg?_ex=128x128)

![FP3級 合格のトリセツ 速習テキスト 2026-27年版 (FP合格のトリセツシリーズ) [ 東京リーガルマインド LEC FP試験対策研究会 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8101/9784844938101_1_5.jpg?_ex=128x128)

![わたしはこれでやせました [ MEGUMI ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4512/9784478124512_1_2.jpg?_ex=128x128)