福田昭のセミコン業界最前線

微細化の壁を超える“次のCMOS構造”。TSMCが挑む極限技術「CFET」

2025年12月12日 06:13

投稿件数は2年連続で過去最多を更新

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting、日本語の通称は「国際電子デバイス会議」)」が、米国カリフォルニア州サンフランシスコで始まった。技術講演会(テクニカルカンファレンス)の初日となる2025年12月8日の正午には、IEDMの実行委員会によって報道機関向け説明会が開催された。

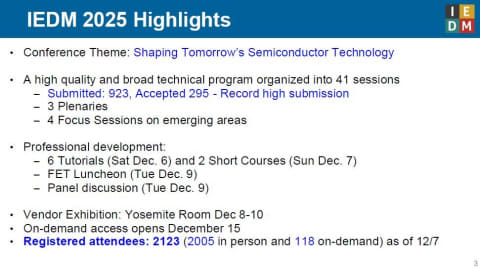

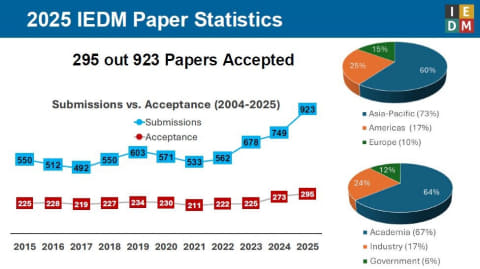

IEDMでの発表を目指して投稿された論文の件数は923件で、過去最多を記録した前年(IEDM 2024)の763件をさらに上回り、2年連続で過去最多を更新した。採択された論文の件数は295件である。前年の採択件数である274件から、21件増えた。採択率は32%である。前年の採択率35.9%と比べて3.9ポイント低下した。

参加登録者数は12月7日時点で2,123名である。内訳はリアル参加が2,005名、バーチャル参加が118名。前年の参加登録者数は2,160名(リアル参加2,025名、バーチャル参加135名)だったので、ほぼ変わらない。

IEDM 2025の採択論文数を地域別に見ていくと、アジア太平洋地域が60%(投稿論文数の比率は73%)と最も多い。米州地域は25%(同17%)、欧州地域は15%(同10%)である。機関別の採択論文数ではアカデミア(主に大学)が64%(投稿論文数の比率は67%)と多い。インダストリ(主に企業)は24%(同17%)、ガバメント(主に国公立の研究組織)は12%(同6%)となっている。

米国、日本、韓国、中国、台湾の合計が参加者の9割近くを占める

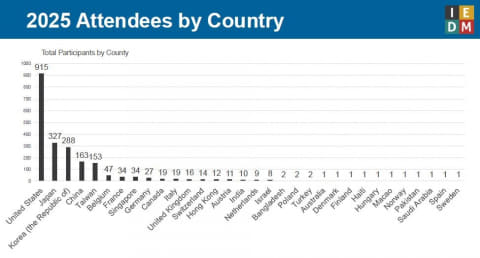

参加登録者数を国/地域別に見ると、米国が915名で43%を占める。次いで日本が327名、韓国が288名、中国が163名、台湾が153名と続く。日本と韓国、中国、台湾の合計は931名で、米国を超える。またこれら5カ国/地域で1,846名となり、全体の87%を占める。

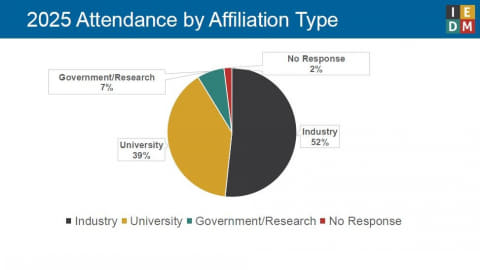

参加登録者数を機関別に見ると、インダストリが52%と半分を超える。大学は39%とほぼ4割を占めた。残りはガバメント/リサーチ(主に国公立の研究組織)が7%、不明が2%である。

相補型トランジスタでリング発振器とSRAMセルを試作

ここからは、12月8日午後の一般講演から注目の発表をご紹介しよう。次世代のトランジスタ技術である「相補型トランジスタ(CFET: Complementary Field Effect Transistor)」で初めて、集積回路の動作が確認された。開発したのはTSMCである(講演番号2-5)。

CFETは、CMOSデバイスの基本構成であるnチャネルFETとpチャネルFETを垂直方向に積層することで、トランジスタの密度を高める技術だ。現在の最先端トランジスタ技術であるナノシートFET(NS FET)に比べ、理論的にはトランジスタ密度を2倍近くに高められる。

ただし技術的な難しさは極限に近い。そもそも、ナノシートFETの製造が難しい。CFETでは、そのナノシートFETを垂直方向にモノリシック積層する(TSMCの場合)。当然ながら、製造はさらに難しくなる。これまでCFETの研究開発成果はほぼ、単体のトランジスタ(厳密には2個のトランジスタによる積層構造)にとどまっていた。TSMCは昨年のIEDMでCFETによるインバータ素子(論理値を反転させる素子)を試作/動作させた結果を報告しており、今回の開発成果はその続きとなる。

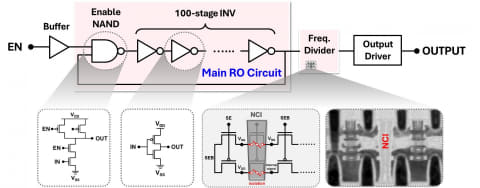

試作した集積回路は2種類。論理回路(ロジック)の基本となる「リング発振器」と、メモリ回路の基本となる「SRAMセル」だ。集積規模が特に大きいのはリング発振器で、トランジスタ数は800個~1,000個に達する。

リング発振器は1段のイネーブルNAND論理素子(リング発振器出力のフィードバック用素子)と100段のインバータ素子で構成した。全体としては101段のリング発振器となる。

試作したリング発振器は、電源電圧が0.5V~0.95Vの範囲で動作した。電源電圧を上げるとともに発振周波数は上昇し、発振周波数のばらつきが減少した。発振周波数そのものは明らかにしていない。

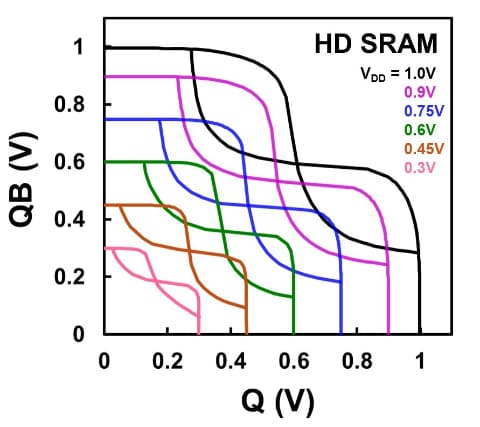

SRAMセルは、6トランジスタによる標準的な回路構成である。記憶密度を重視したHD(高密度)タイプと、性能(駆動電流)を重視したHC(大電流)タイプの2種類のSRAMセルを試作した。いずれも動作を確認している。HDタイプのセル面積は、ほぼ同一の設計ルールによるナノシートFETに比べ、30%縮小した。CFET技術のHCタイプとHDタイプでは、HDタイプのセル面積が20%狭い。逆に読み出し電流はHCタイプがHDタイプの1.7倍と大きい。

SRAMセルの回路には「クロスカップリング(交差結合)」と呼ばれる独自の接続部分が存在する。このために上下のFETを相互接続するコンタクト電極(BCT: Butted Contact)を設けた。

試作したHDタイプのSRAMセルは、電源電圧が0.3V~1.0Vの範囲で動作した。電源電圧が0.75Vのときに読み出し静的雑音余裕(RSNM: Read Static Noise Margin)は135mV、読み出し電流は17.5μA、書込み余裕(WM: Write Margin)は265mVである。SRAMセルのパラメータは最適化されておらず、改善の余地があるとする。

CFET技術によるロジックやメモリなどの実用化時期は、2030年代を目標とする。今回の集積回路は基本中の基本であり、実用化にはまだはるかに遠い。最初の1歩あるいは2歩を踏み出したばかりであるといえる。今後の進展に期待したい。

![イーヤマ G-MASTER G2445HSU-B2 [23.8型液晶ディスプレイ/1920×1080/HDMI、DP/IPS/ノングレア/100Hz/角度調整] 製品画像:16位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage37/1284765.jpg?_ex=128x128)

![5年間フル保証ディスプレイ 243B9/11 [23.8型ワイド液晶ディスプレイ 5年フル保証(USB-C)] 製品画像:15位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage15/1204657.jpg?_ex=128x128)

![[アウトレット] ゲーミングモニター ホワイト パステル ブルー 200hz 24インチ pcモニター 144Hz 165Hz対応 モニター 白 フルHD IPS HDR ノングレア スピーカー搭載 VESA 23.8インチ 液晶ディスプレイ Pixio ピクシオ 公式 PX248WAVE 製品画像:14位](https://thumbnail.image.rakuten.co.jp/@0_mall/pixiogaming/cabinet/outlet/px248w-outlet.jpg?_ex=128x128)

![地球の歩き方 スター・ウォーズ [ 地球の歩き方編集室 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6939/9784058026939_1_2.jpg?_ex=128x128)

![中学英語をもう一度ひとつひとつわかりやすく。改訂版 [ 山田 暢彦 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4821/9784053054821_1_5.jpg?_ex=128x128)

![火山灰アトラス 第3版 日本列島とその周辺 [ 町田 洋 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7667/9784130607667_1_13.jpg?_ex=128x128)

![遊☆戯☆王OCG STORIES 5 (ジャンプコミックス) [ 三好 直人 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4596/9784088844596_1_6.jpg?_ex=128x128)

![愛蔵版 イクサガミ [ 今村 翔吾 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3029/9784065413029_1_4.jpg?_ex=128x128)

![仏像の着衣と僧衣の研究 東洋美術史論考 [ 吉村 怜 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3287/9784831863287.jpg?_ex=128x128)

![2026年度版「スピードテキスト」診断士7冊セット [ TAC中小企業診断士講座 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2266/2100014752266.jpg?_ex=128x128)

![[注文後キャンセル不可/代引き不可/発売後に発送] ワンピースマガジン ONE PIECE magazine[本/雑誌] Vol.21 【特集】 ヒロインズ 【カード付き同梱版】 (集英社ムック) (単行本・ムック) / 尾田栄一郎 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/neowing-r/cabinet/item_img_2196/neobk-3205619.jpg?_ex=128x128)

![タッチペンで音が聞ける!はじめてずかん1000 英語つき [ 小学館 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6775/9784099416775_1_37.jpg?_ex=128x128)