福田昭のセミコン業界最前線

物理解析なしにDRAMの不良モードと要因を推定するツールなどがIRPS 2024に登場

2024年4月13日 11:59

本コラムの前回でお伝えしたように、半導体デバイスの信頼性技術に関する世界最大の国際会議「国際信頼性物理シンポジウム(IRPS : IEEE International Reliability Physics Symposium)」(通称は「アイアールピーエス」)が2024年4月14日~18日に米国テキサス州ダラスで開催される。

本コラムの前回では、IRPSの開催概要と基本スケジュール、それから技術講演セッションのテーマとスケジュールの一覧を報告した。技術講演では分野別に「回路とシステムの信頼性」、「次世代トランジスタの信頼性」、「自己発熱効果(SHE : Self-Heating Effect)」に関連した主な発表を簡単に紹介した。

今回は分野別注目講演の続きになる。「フラッシュメモリ」、「DRAM」、「強誘電体メモリ」、「クロスポイントメモリ」、「高周波/ミリ波デバイス」、「シリコンフォトニクス」、「SiCデバイス」、「GaNデバイス」、「Siパワーデバイス」、「ソフトエラー」に関する主な発表の概要を述べる。

TLC NANDのSSDとQLC NANDのSSDで信頼性を比較

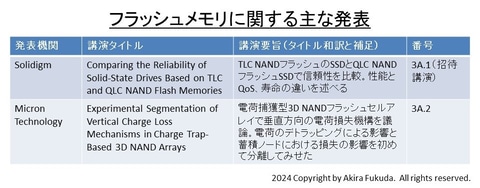

始めは半導体メモリに関する主な発表を順番に説明する。最初は「フラッシュメモリ」である。

Solidigmは、TLC NANDフラッシュメモリのSSDとQLC NANDフラッシュメモリのSSDで信頼性を比較した(招待講演、番号3A.1)。性能とQoS、寿命の違いを述べる予定だ。

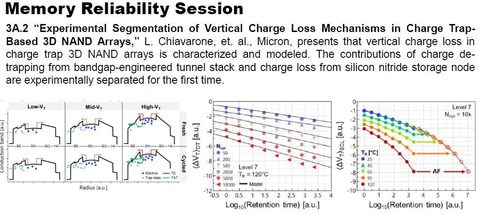

Micron Technologyは、電荷捕獲(チャージトラップ)型3D NANDフラッシュセルアレイで垂直方向の電荷損失メカニズムを議論する(講演番号3A.2)。電荷のデトラッピングによる影響と蓄積ノードにおける損失の影響を初めて分離してみせた。

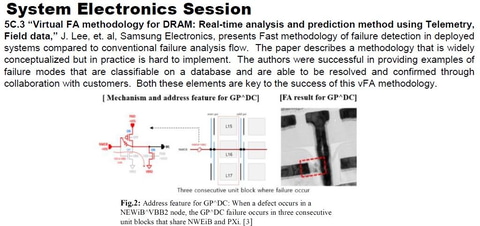

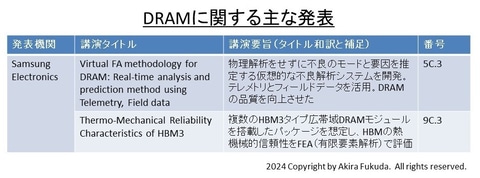

続いて「DRAM」である。Samsung Electronicsが披露する2件の研究成果が興味深い。1件は物理解析をせずにDRAMの不良モードと不良要因を推定する仮想的な不良解析システムである(講演番号5C.3)。テレメトリとフィールドデータを活用する。DRAMの品質向上に役立ったという。

もう1件は、複数のHBM3タイプ広帯域DRAMモジュールを搭載したパッケージを想定し、HBMの熱機械的信頼性をFEA(有限要素解析)で評価した研究である(同9C.3)。1個のパッケージに搭載するHBMの数が増えており、さらにはHBMが収容するDRAMダイの枚数が増えていることから、熱機械的解析の必要性が高まっている。

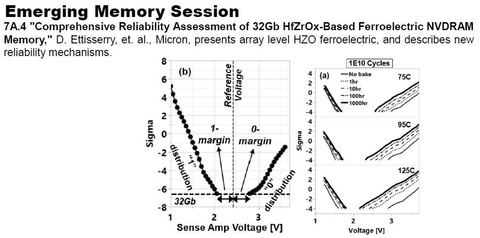

32Gbitの大容量強誘電体メモリを試作して長期信頼性を評価

次は「強誘電体メモリ」である。Micron Technologyは、ハフニウムジルコニウム酸化物(HfZrOx)強誘電体キャパシタ(C)による1T1C(1トランジスタ、1キャパシタ)セルの32Gbit大容量不揮発性メモリを試作した(講演番号7A.4)。長期信頼性を測定し、新たなTDDB不良モードを確認した。

Namlabほかの共同研究グループは、ハフニウム酸化物(HfOx)強誘電体のキャパシタを利用した不揮発性メモリ(FeRAM)の読み書きサイクル寿命とデータ保持期間に対する強誘電体酸化物/金属界面の影響を解明した(招待講演、番号7A.1)。東京大学は、デバイスの劣化に耐性を有するシリコン強誘電体FETベースのリザーバーコンピューティングについて述べる(招待講演、番号6C.1)。

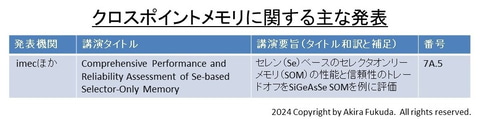

このほか半導体メモリでは、imecなどの共同研究グループが、セレン(Se)系材料のセレクタを使うセレクタオンリーメモリ(SOM)の性能と信頼性のトレードオフを報告する(講演番号7A.5)。セレクタの材料はSiGeAsSe化合物である。

77GHzミリ波レーダー向けCMOSアンプの動作寿命

ここからはメモリ以外の分野を取り上げていく。無線通信、光通信、パワーデバイス、ソフトエラーが挙がる。

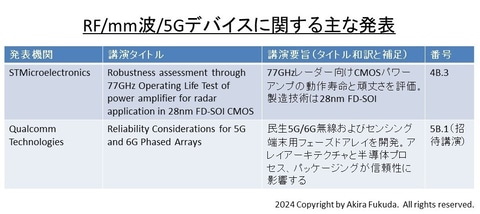

「高周波/ミリ波デバイス」では、STMicroelectronicsが77GHzレーダー向けCMOSパワーアンプの動作寿命と頑丈さを評価した(講演番号4B.3)。製造技術は28nmのFD-SOIプロセスである。Qualcomm Technologiesは、民生5G/6G無線およびセンシング端末用フェーズドアレイを開発した(招待講演、番号5B.1)。アレイアーキテクチャと半導体プロセス、パッケージングが信頼性に影響するという。

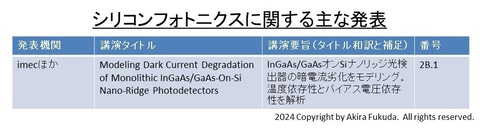

「シリコンフォトニクス」では、imecほかの共同研究グループがInGaAs/GaAsオンSiナノリッジ光検出器の暗電流劣化をモデリングした(講演番号2B.1)。温度依存性とバイアス電圧依存性を解析した結果を発表する。

300mmのSiウェハによるGaN-on-Siのエンハンスメント型HEMT

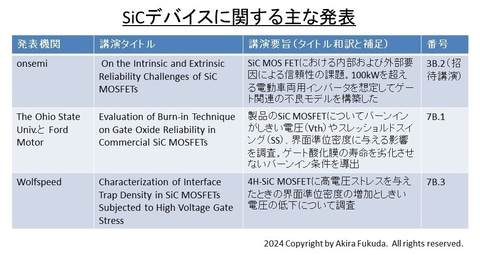

続いてパワーデバイス関連の注目講演を紹介したい。始めは「SiCデバイス」である。onsemiは、SiC MOS FETにおける内部要因および外部要因による信頼性の課題を解説する(招待講演、番号3B.2)。100kWを超える電動車両用インバータを想定してゲート関連の不良モデルを構築した。

The Ohio State Universityと Ford Motorの共同研究チームは、製品のSiC MOSFETについてバーンインがしきい電圧(Vth)やスレッショルドスイング(SS)、界面準位密度に与える影響を調査した(講演番号7B.1)。ゲート酸化膜の寿命を短縮させないバーンイン条件を導出している。Wolfspeedは、4H-SiC MOSFETに高電圧ストレスを与えたときの界面準位密度の増加としきい電圧の低下について調べた結果を述べる(同7B.3)。

続いて「GaNデバイス」である。Texas Instrumentsは、GaNデバイスの信頼性試験が抱える課題について述べる(招待講演、番号2C.3)。GaNトランジスタに対する従来の信頼性試験方法は、電源用途におけるさまざまなストレスをカバーしていない。実用的な試験方法の開発によって信頼性を確保した製品の例を示す。

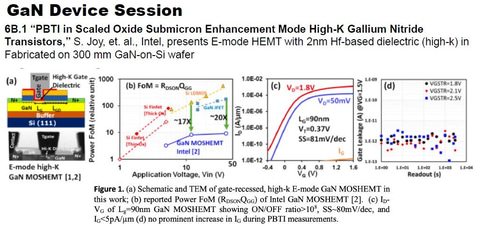

Intelは、直径300mmのSiウェハを利用したGaN-on-Si技術によるサブミクロンのエンハンスメント型GaN MOS HEMTのPBTI特性を検証した(講演番号6B.1)。ゲート絶縁膜はハフニウム系の高誘電率膜で2.15nmと薄い。Si LDMOSと比べてFOMは15倍前後と高い。

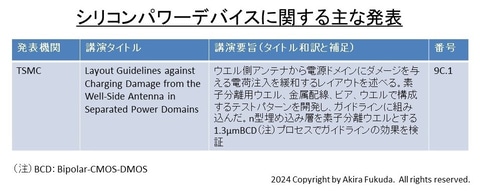

「Siパワーデバイス」でも注目すべき発表がある。TSMCはバイポーラCMOSのウエル側アンテナから電源ドメインにダメージを与える電荷注入を緩和するレイアウトを述べる(講演番号9C.1)。素子分離用ウエル、金属配線、ビア、ウエルで構成するテストパターンを開発し、ガイドラインに組み込んだ。n型埋め込み層を素子分離用ウエルとする1.3μmのBCD(Bipolar-CMOS-DMOS)プロセスでガイドラインの効果を検証した。

微細化してもソフトエラー耐性は弱くならない

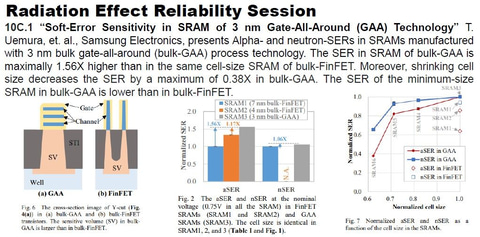

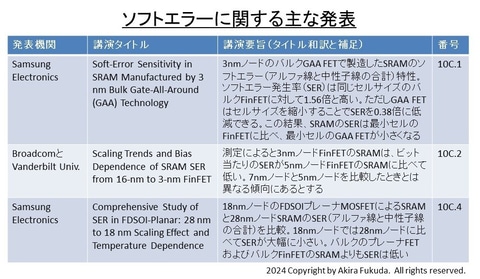

最後は「ソフトエラー」に関する主な発表を紹介しよう。Samsung Electronicsは、3nmノードのバルクGAA FETで製造したSRAMのソフトエラー(アルファ線と中性子線の合計)特性を調べた(講演番号10C.1)。ソフトエラー発生率(SER)は同じセルサイズのバルクFinFETに対して1.56倍と高い。

ただしGAA FETはセルサイズを縮小することでSERを0.38倍に低減できる。この結果、SRAMのSERは最小セルのFinFETに比べ、最小セルのGAA FETが小さくなる

Broadcomと Vanderbilt Universityの共同研究チームは、3nmノードのFinFETによるSRAMソフトエラーと5nmノードのFinFETによるSRAMのソフトエラーを実測で比較した(講演番号10C.2)。3nmノードFinFETのSRAMは、ビット当たりのSERが5nmノードFinFETのSRAMに比べて低い。7nmノードと5nmノードを比較したときとは異なる傾向にあるとする。

Samsung Electronicsは、18nmノードのFD SOIプレーナMOSFETによるSRAMと28nmノードFD SOIプレーナMOSFETによるSRAMのSER(アルファ線と中性子線の合計)を比較した(講演番号10C.4)。18nmノードでは28nmノードに比べてSERが大幅に小さい。バルクのプレーナFETおよびバルクFinFETのSRAMよりもSERは低い。

誌面の関係で紹介できなかったポスター発表を始め、このほかにも興味深い発表が少なくない。開催後のレポートに期待されたい。

![■air-J NEW カラビナコイルストラップ 太型ロングタイプBK〔品番:ASR10BK〕【3928897:0】[店頭受取不可] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/hcvalor-eshop/cabinet/trusco/3928/trusco-3928897.jpg?_ex=128x128)

![北北西に曇と往け 続の1 [ 入江 亜季 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8024/9784911278024_1_56.jpg?_ex=128x128)

![JISハンドブック 59 製図(2025) [ 日本規格協会 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1488/9784542191488_1_3.jpg?_ex=128x128)

![【特典】メロとタビ(【初回限定シールB付】) [ まめきちまめこ ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6482/2100014936482_1_2.jpg?_ex=128x128)

![糖毒脳 いつまでも「冴えた頭」でいるために知っておきたいこと [ 下村 健寿 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1757/9784478121757_1_2.jpg?_ex=128x128)

![駆動システムの高性能・高効率化技術を完全習得 モーター・インバーター制御 【電子書籍】[ 高橋 久 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0328/2000019200328.jpg?_ex=128x128)

![CBT対応版 QC検定3級 対策問題集 2026年版 [ 仁科 健 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5384/9784542505384_1_4.jpg?_ex=128x128)

![リンネル 2026年 7月号 [雑誌] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0769/4912193070769_1_2.jpg?_ex=128x128)