福田昭のセミコン業界最前線

新品と再生品ICの見分け方など、最新の信頼性技術がIRPS 2024に続出

2024年4月12日 09:42

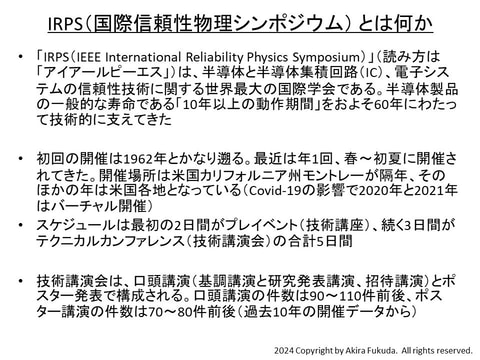

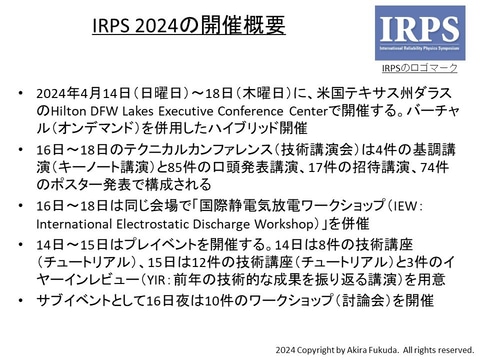

半導体デバイスの信頼性技術に関する世界最大の国際会議「国際信頼性物理シンポジウム(IRPS:IEEE International Reliability Physics Symposium)」が4月14日~18日に米国テキサス州ダラスで開催される。3nm以降の半導体ロジックやロジック用トランジスタ、DRAM、フラッシュメモリ、化合物半導体パワーデバイス、RF/ミリ波デバイス、シリコンフォトニクス、パッケージングなどの分野で信頼性を支える技術の研究開発成果が登場する。

今年(2024年)のIRPS(IRPS 2024)は、前年に続いてリアルイベントとバーチャル(オンデマンド)のハイブリッド開催となる。リアルイベントに参加することが望ましいのは言うまでもない。しかし東京とダラスを往復するための航空運賃と交通費は合計で30万円近くに上る。残念ながら筆者は予算が足りず、バーチャルでの参加となる。

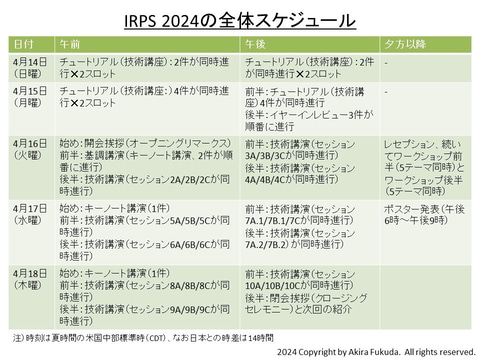

IRPSの基本的なスケジュールは5日間で、日曜日から木曜日までとなる。始めの2日間は技術講座(チュートリアル)とイヤーインレビュー(前年の技術的な進展を振り返る講演)で構成される。今年は20件のチュートリアルと3件のイヤーインレビューを用意した。

メインイベントである技術講演会は火曜日から木曜日までとなる。今年は4件の基調講演、85件の一般講演、17件の招待講演、74件のポスター発表で構成される。

もう少し詳しく説明すると、14日は午前に4件、午後に4件のチュートリアルを予定する。翌15日は午前に8件、午後に4件のチュートリアルを設けたほか、夕方には3件のイヤーインレビューを用意した。

メインイベント初日の16日は議長による開会挨拶から始まる。続けて午前に2件の基調講演を予定する。基調講演の後は技術講演会の一般講演と招待講演のセッションとなる。夕方はレセプション、その後にワークショップと進む。ワークショップは前半と後半があり、それぞれ5件のテーマを用意した。

メインイベント2日目の17日は午前の最初に1件の基調講演があり、その後は夕方まで技術講演会となる。夜にはポスター発表がある。

最終日の18日も、午前の最初に1件の基調講演を予定する。その後は午後まで技術講演会となる。夕方にはチェアによる閉会挨拶と次回予告がある。

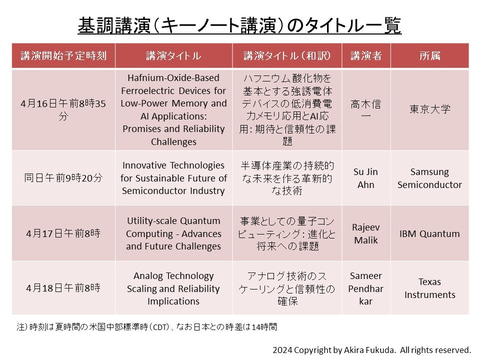

東京大学、Samsung、IBM、TIが基調講演

それでは口頭発表講演の概要を見ていこう。初めは基調講演である。4件の講演(いずれも招待講演)を予定する。技術講演会の初日である16日の午前に2件の基調講演がある。まず東京大学の高木信一教授が「ハフニウム酸化物を基本とする強誘電体デバイスの低消費電力メモリ応用とAI応用:期待と信頼性の課題(Hafnium-Oxide-Based Ferroelectric Devices for Low-Power Memory and AI Applications: Promises and Reliability Challenges)」と題してハフニウム酸化物強誘電体デバイスの現状と課題を述べる。

続いてSamsung SemiconductorのSu Jin Ahn氏が「半導体産業の持続的な未来を作る革新的な技術(Innovative Technologies for Sustainable Future of Semiconductor Industry)」と題して半導体産業を維持する革新的な技術群を展望する。

17日の午前は、IBM QuantumのRajeev Malik氏が「事業としての量子コンピューティング:進化と将来への課題(Utility-scale Quantum Computing - Advances and Future Challenges)」と題して量子コンピューティングの商業化を論じる。

最終日である18日(木曜日)の午前は、Texas Instruments(TI)のSameer Pendharkar氏が「アナログ技術のスケーリングと信頼性の確保(Analog Technology Scaling and Reliability Implications)」と題してアナログ技術の微細化と信頼性の将来像を語る。

29の技術講演セッションを3日間で実施

技術講演会のテーマ別セッションは、最大で3つのセッションが同時進行する。少し詳しく見ていこう。

16日の午前は、「ゲートとコンタクトの誘電体(Gate/MOL Dielectrics)」、「信頼性試験(Reliability Testing)」、「窒化ガリウム(GaN)デバイス(GaN Devices)」のセッションが並行して進む。午後の前半は、「メモリの信頼性(Memory Reliability)」、「シリコンカーバイド(SiC)デバイス(SiC Devices)」、「製品の信頼性(Product Reliability)」の3つのセッション、午後の後半は「トランジスタ(Transistors)」、「高周波/ミリ波/第5世代移動体通信(RF/mmW/5G)」、「回路の信頼性とエージング(Circuit Reliability & Aging)」の3つのセッションが並行して実施される。

翌17日午前の前半は、「集積化プロセス(Process Integration)」、「RF/mmW/5G」(2回目)、「電子システムの信頼性(System Electronics Reliability)」の3つのセッションが並行して進む。午前の後半は「トランジスタ(2回目)」、「GaNデバイス(2回目)」、「ニューロモルフィックコンピューティングの信頼性(Neuromorphic Computing Reliability)」が並行して実施される。

17日午後の前半は、「次世代メモリ(Emerging Memory)」、「SiCデバイス」(2回目)、「回路の信頼性とエージング」(2回目)の3つのセッションが同時に進行する。午後の後半は、「次世代メモリ」(2回目)と「トランジスタ」(3回目)の2つのセッションが並行して進む。

最終日である18日午前の前半は、「信頼性試験」(2回目)、「パッケージングと2.5/3次元組み立て(Packaging & 2.5/3D Assembly)」、「静電気放電とラッチアップ(ESD and Latch-up)」の3つのセッションが同時に進む。午前の後半は、「ゲートとコンタクトの誘電体」(2回目)、「メモリの信頼性」(2回目)、「製品の信頼性」(2回目)のセッションを予定する。

18日午後は、「多層配線工程の信頼性(Metallization/ BEOL Reliability)」、「不良解析(Failure Analysis)」、「放射線が信頼性に与える影響(Radiation Effect Reliability)」の3つのセッションを並行して進める。

新品のICと再利用品のICを外部から見分ける

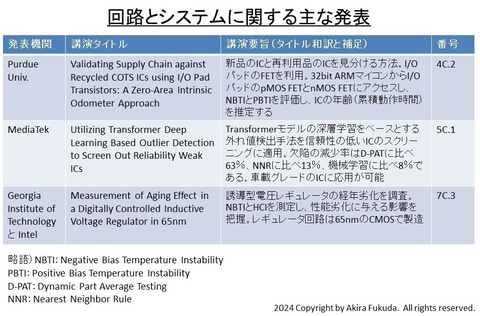

続いて注目すべき技術講演を分野別に紹介しよう。始めは回路とシステムの信頼性に関する研究成果の講演を取り上げる。いずれも大変に興味深い研究成果だ。

パデュー大学は、新品のICと再利用品のICを見分ける方法を開発した(講演番号4C.2)。I/OパッドのFET(バッファトランジスタ)を利用する。32bit ARMマイコンからI/OパッドのpMOS FETとnMOS FETにアクセスし、それぞれNBTI(Negative Bias Temperature Instability)とPBTI(Positive Bias Temperature Instability)を評価する。評価結果から、ICの年齢(累積動作時間)を推定する。新品であれば、累積動作時間はテスト時間とバーンイン時間の合計程度にとどまる。

MediaTekは、Transformerモデルの深層学習をベースとする外れ値検出手法を信頼性の低いICのスクリーニングに適用してみせた(講演番号5C.1)。外れ値を取り除くことによる欠陥の減少率はD-PAT(Dynamic Part Average Testing)に比べ63%、NNR(Nearest Neighbor Rule)に比べ13%、従来の機械学習に比べ8%とかなりの効果がある。車載グレードのICに応用することを目指す。

GAAトランジスタの性能と信頼性のトレードオフを議論

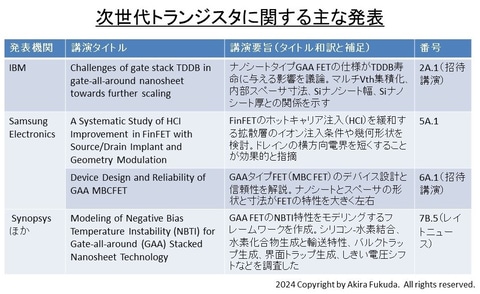

次はIRPSの定番とも言える、次世代トランジスタの信頼性に関する研究成果である。

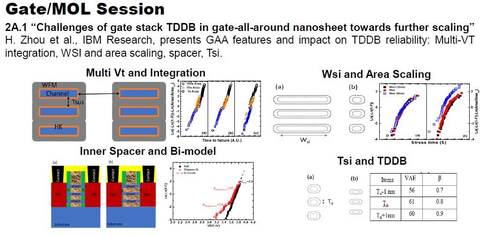

IBMは、ナノシートタイプGAA(Gate All Around) FETの仕様がTDDB(Time Dependent Dielectric Breakdown)寿命に与える影響を議論する(招待講演、番号2A.1)。マルチVth集積化、内部スペーサ寸法、Siナノシート幅、Siナノシート厚とTDDB寿命の関係を示す。

Samsung Electronicsは、GAAタイプFET(MBC FET)のデバイス設計と信頼性を解説する(招待講演、番号6A.1)。ナノシートとスペーサの形状と寸法がFETの特性を大きく左右する。IBMの講演(2A.1)と比べたくなる発表だ。

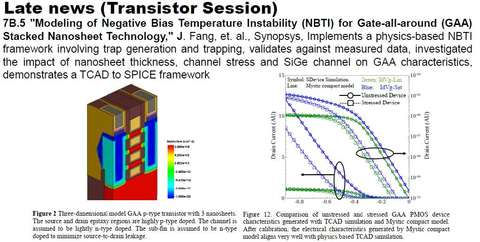

Synopsysほかの共同研究グループは、GAA FETのNBTI特性をモデリングするフレームワークを作成した(講演番号7B.5、レートニュース)。シリコン-水素結合、水素化合物生成と輸送特性、バルクトラップ生成、界面トラップ生成、しきい電圧シフトなどを調査した。

自己発熱効果の影響を見積もる技術が相次いで登場

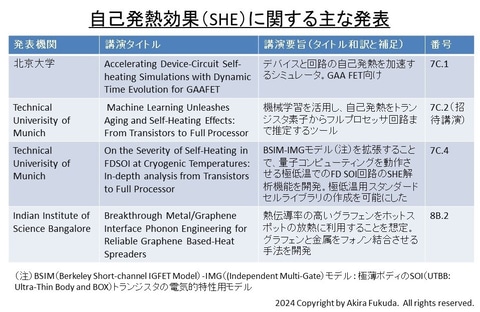

今回のIRPSでは「自己発熱効果(SHE:Self-Heating Effect)」に関連した研究の発表が少なくない。過去に問題とされてきた配線の温度上昇ではなく、トランジスタと回路ブロックに関連した寿命推定の研究が目立つ。

北京大学はGAA FET向けにデバイスと回路の自己発熱を加速するシミュレータを開発した(講演番号7C.1)。ミュンヘン工科大学は機械学習を活用し、自己発熱をトランジスタ素子からフルプロセッサ回路まで推定するツールについて述べる(招待講演、番号7C.2)。同大学はまた、極低温環境下におけるFD SOI回路のSHE解析ツールを開発した(講演番号7C.4)。業界標準のBSIM-IMGモデルを極低温用に拡張した。極低温用スタンダードセルライブラリの作成を可能にしたとする。

インド理科大学院は、グラフェンと金属をフォノン結合させる手法を開発した(講演番号8B.2)。熱伝導率の高いグラフェンをホットスポットの放熱に利用できるようにする。

そのほかの分野である「フラッシュメモリ」、「DRAM」、「強誘電体メモリ」、「高周波/ミリ波デバイス」、「シリコンフォトニクス」、「SiCデバイス」、「GaNデバイス」、「Siパワーデバイス」、「ソフトエラー」に関する注目講演は、機会を改めて本コラムで急ぎ紹介する予定だ。しばらくお待ちいただけるとありがたい。

![内視鏡所見のよみ方と鑑別診断ー上部消化管 第3版 [ 小原 勝敏 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6848/9784260046848_1_4.jpg?_ex=128x128)

![ブティック [ 池井戸 潤 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4697/9784478124697_1_3.jpg?_ex=128x128)

![イン・ザ・メガチャーチ [ 朝井リョウ ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1045/9784296121045_1_4.jpg?_ex=128x128)

![将軍の都の客人 越後の寺娘・常野、江戸を訪う [ エイミー・スタンリー ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7501/9784622097501_1_6.jpg?_ex=128x128)

![NHK テレビ ハングルッ!ナビ 2026年 6月号 [雑誌] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0660/4912091930660_1_2.jpg?_ex=128x128)

![認知症の人びとの看護 第4版 [ 中島 紀惠子 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0722/9784263710722_1_2.jpg?_ex=128x128)

![爺さんバイク奮闘記 [ 佐東敏三郎 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0305/9784991430305_1_5.jpg?_ex=128x128)