福田昭のセミコン業界最前線

キオクシア、218層の第8世代3D NAND発表。“第7世代”は幻に?

2023年8月18日 06:17

NANDフラッシュメモリとその応用製品に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」が2023年8月7日に米国カリフォルニア州シリコンバレー地域の会議場「サンタクララコンベンションセンター(SCCC:Santa Clara Convention Center)」で始まった。メインイベントである講演会と展示会は8日から10日まで開催される。

恒例の基調講演では本コラムの前回で述べたように、キオクシア、SK hynix、Western Digital(以降はWDと表記)の3社が次世代の3D NANDフラッシュメモリを発表した。前回はSK hynixの講演概要を紹介した。今回はキオクシアの講演概要をご報告する。

キオクシアは始めに、第8世代(BiCS8世代)の3D NANDフラッシュメモリを発表した。既存世代(第6世代:BiCS6世代)のNANDフラッシュに比べ、記憶密度が50%、電力効率が30%、インターフェイス速度が60%向上するとアピールしていた。メモリセル(ワード線)の積層数は218層である。

続いて現在までの回路レイアウトの進化を示した。第5世代(BiCS5)ではメモリセルアレイとCMOS周辺回路をシリコンダイに並べてレイアウトするCNA(CMOS Next to Array)だった。ごく一般的なレイアウトである。BiCS6ではメモリセルアレイとCMOS周辺回路を積層するCUA(CMOS Under Array)を採用してシリコンダイの記憶密度を高めた。最近の世代はCUAあるいは類似の技術を採用していることが多い。

CMOS周辺回路とメモリセルアレイを別々のウェハに

BiCS8では、メモリセルアレイとCMOS周辺回路を異なるウェハに形成してからウェハ同士を貼り合わせる「CBA(CMOS directly Bonded to Array)」技術を開発した。ワード線積層数の高層化によって記憶密度を35%高め、CBAの開発と採用によって記憶密度を15%高めた。その結果、記憶密度を第6世代に比べて50%向上させた。

さらに細かな性能の違いもBiCS6との相対比較で説明していた。書き込み(プログラム)スループットは20%向上し、読み出し遅延時間(レイテンシ)は10%短くなり、書き込みと読み出しの消費電力はともに30%低下した。

記憶容量は1Tbit、多値記憶にはTLC方式、記憶密度は17Gbit/平方mm

キオクシアとWDは今年(2023年)3月30日に、BiCS8の3D NANDフラッシュ技術を開発したと報道機関向けにアナウンスしていた。このとき、シリコンダイの記憶容量が1Tbitであること、メモリセルの積層数は218層であること、CBA技術を開発したこと、メモリセルアレイは4つのプレーンに分割していること、などをすでに明らかにしている。

同年6月には国際学会VLSIシンポジウムで、第8世代の3D NANDフラッシュの試作チップを公表した(論文番号C2-1)。メモリセルの積層数は210層以上、記憶容量は1Tbit、多値記憶方式はTLC(3bit/セル)方式、メモリセルアレイのプレーンは物理的には8分割で論理的には4分割、ページサイズは16KB(と誤り訂正ビット)、読み出しレイテンシは40μs、書き込みスループットは205MB/s、入出力速度は3.2Gbpsである。記憶密度は17Gbit/平方ミリを超えるとする。シリコンダイ面積とメモリセル面積は公表していない。またCBA技術について論文では触れていないものの、発表講演直後の質疑応答ではCBA技術を採用していることが確認された。

ウェハ貼り合わせによるコストと性能のトレードオフ

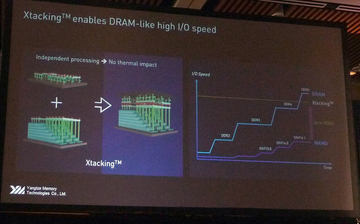

CBA技術は、中国のYMTCが以前に開発した「Xtacking」技術と類似の要素技術だ。メモリセルアレイ形成時の高温アニール処理をCMOS周辺回路が受けないので、周辺回路の動作速度を高めやすい。またCMOS周辺回路とメモリセルアレイのビット線を接続するための領域を省けるので、記憶密度が上がる。

ただし性能は向上するものの、ウェハ貼り合わせ工程によって製造コストは上昇する懸念がある。YMTC以外のNANDフラッシュ大手はこれまで採用してこなかった要素技術なので、今後の行方が注目される。

メモリ拡張インターフェイス「CXL」と高速フラッシュ「XL-FLASH」を組み合わせる

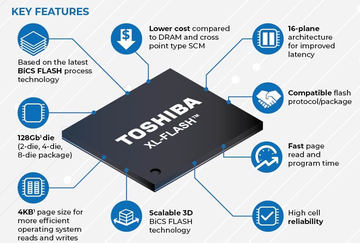

キオクシアがキーノート講演で述べたもう1つの重要なテーマに、「拡張メモリインターフェイスとしてのCXL(Compute Express Link)」がある。従来、NANDフラッシュメモリは外部ストレージとしてメモリ階層ではHDDと同等に扱われていた。これがCXLの登場と普及によってDRAMと同等のメモリ階層に置ける可能性が強まった。

そこでキオクシアは、DRAMを含めたメモリの記憶容量を拡張する手法として、高速フラッシュ「XL-FLASH」のメモリモジュールをCXLインターフェイス経由でプロセッサと接続することを提案した。「XL-FLASH」は3D NANDフラッシュメモリの一種で、多値記憶ではなく、2値記憶(SLC(1bit/セル))方式を採用することによって読み書きを高速に実行する。

講演では、CXLのXL-FLASHをメモリ階層に導入することによってキャッシュ性能(スループット)が従来の5倍に高まるとのシミュレーション結果を示していた。

「第7世代(BiCS7)」の呼称が消えた謎

キオクシア-WD連合は2023年の3月~8月にかけてBiCS8の3D NANDを発表してきた。ここで生じた最大の疑問は第6世代の次世代が「第7世代(BiCS7)」ではなく、第8世代となったことだ。ワード線積層数はBiCS6が17X層、BiCS8が218層なので、層数からは218層が「第7世代」でも不思議はない。むしろ当然に見える。

ここで気になるのは、CUA技術ではなく、ウェハ貼り合わせ技術(CBA技術)を採用したことにある。そこで第7世代ではなく、世代を飛ばして「第8世代」と呼称したとも考えられる。カギとなるのは入出力速度だ。YMTCは2018年のFMSでXtacking技術(ウェハ貼り合わせ技術)のメリットの1つに周辺回路の高速化を挙げていた。この時、CUA技術による入出力速度の限界を1Gbpsとし、Xtacking技術だと入出力速度の限界を3GHz前後に伸ばせると、述べていた。

奇しくもキオクシアの第8世代品は入出力速度が3.2Gbpsであり、YMTCの指摘と合致する。すると個人的な観測に過ぎないが、「幻の第7世代」は既存のCUA技術で21X層に高層化したチップだとの推定が成立する。もちろん本当のところは分からない。今後、謎が解けることを期待したい。

![IOデータ ゲーミングモニター KH-GD251UH 240Hz&フルHD対応 GigaCrysta [24.5型 / フルHD(1920×1080) / ワイド / 240Hz] ブラック 製品画像:7位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001504/4957180184845_1.jpg?_ex=128x128)

![ハーバード、スタンフォード、オックスフォード… 科学的に証明された すごい習慣大百科 人生が変わるテクニック112個集めました [ 堀田秀吾 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3417/9784815633417_1_19.jpg?_ex=128x128)

![2級電気工事施工管理技士 完全攻略 第一次検定・第二次検定対応 [ 不動 弘幸 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8667/9784274228667_1_2.jpg?_ex=128x128)

![貴族転生 〜恵まれた生まれから最強の力を得る〜 11巻 【電子書籍】[ 三木なずな ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0537/2000020190537.jpg?_ex=128x128)

![ダンジョンに出会いを求めるのは間違っているだろうか 1-21巻セット [ 大森藤ノ ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2242/2100014752242.jpg?_ex=128x128)

![人文知は武器になる (文春新書) [ 山口 周 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5292/9784166615292_1_9.jpg?_ex=128x128)

![アニメディア 2026年 6月号 [雑誌] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0660/4912015790660_1_2.jpg?_ex=128x128)