大原雄介の半導体業界こぼれ話

AMDに買収されて消えた良きAIプロセッサ企業の話と、電源設計やDDR4メモリ高騰の話

2025年6月27日 06:17

消えたUntether AI

AMDは6月12日に「Advancing AI 2025」を開催し、Instinct MI350XシリーズやROCm 7.0などを発表したという話は既に記事が掲載されているが、このイベントの陰でAMDはいくつかの動きをしていた。

6月4日、AMDはBriumを買収したことを発表した。リリースによれば、これはSilo AI、Nod.aiとMipsologyに続く4社目の買収であり、AMDは同社のコンパイラおよびAIソフトウェアのエンジニアリングチームを高く評価しており、これが同社のAI戦略に重要であるとしている。

その翌日である6月5日、AMDはUntether AIのエンジニアリングチームのみを買収した。これに関してAMDはリリースを出していないが、Untether AIがこんなリリースを出しており、同社がこれまで提供してきた製品やソフトウェアは完全に供給中止となること、そしてエンジニアリングチームが全部AMDに移籍することを明らかにしている(冒頭、図1)。

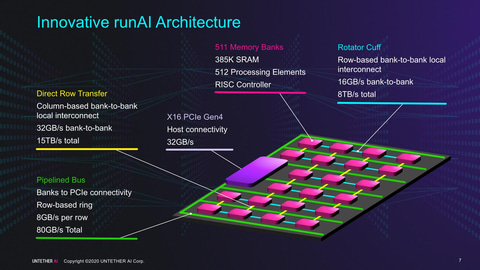

Untether AIは2018年にカナダ・トロントで創業した。同社はNear-Memory Computingを武器にした推論向けプロセッサの開発を試みる。2020年のLinley Fall Processor Conferenceにおける説明によれば、同社の「runAI200」という最初のチップは511個のメモリバンクから構成されるが、各々のメモリバンクには385KBのSRAMとRISCプロセッサ、それと512個のPE(Processor Element)が内蔵されている(図2)。

メモリバンク間はコラム方向のデータをまとめて転送するDirect Row Transferと、個々の演算結果を転送するPipelined Bus、さらにメモリバンク同士を繋ぐRotator Cuffの3種類で接続される複雑な構造だ。

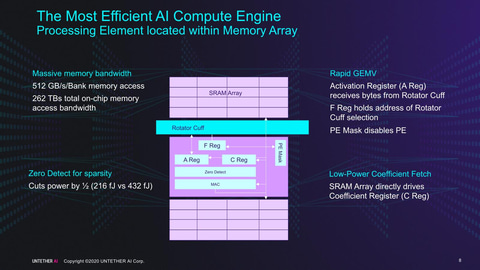

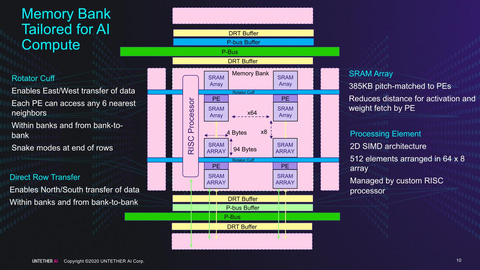

ここのPEの内部はこんな具合(図3)で、アドレスとかアクティベーションの閾値はRotator CuffからA Reg/F Regに取り込み、これを利用してPEで演算した結果をSRAMに格納するという形になる。このPEを512(64×8)個集積したのがメモリバンク(図4)であり、これをさらに511個集めるという仕組みだ。

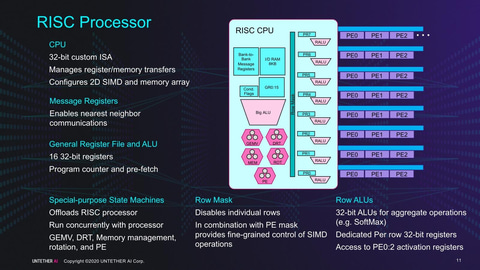

個々のPEは全体で連動する形で64×8の2D SIMD演算が可能になっており、この制御を左端のRISCプロセッサで行なうという形である。そのRISCプロセッサの構造が図5で、一応自前で演算を行なうこともできるが、メインの処理はPEの管理と最後にPEから来た結果の合計(Softmaxなど)の計算といった感じになっている。

【6月30日訂正】初出時、図5が誤っておりました。お詫びして訂正します。

この独自の構造により、MAC演算の消費電力は432fJ/Bとされており、一般的なCPUでのMAC演算が2.5pJ/B(これは同社の推定による数字)に比べて6倍近く効率的、とされていた。runAI200全体で言えば、ピークで502TOPsの性能を叩き出し、動作周波数は720MHzのEcoモードと、960MHzのSpotモードの2種類。このEcoモードの時には8TOPs/Wの効率を誇った。

チップの絶対性能もさることながら、何よりこのチップ、TSMCの16nmで製造されていながらこの性能である点がポイントで、同じプロセスで製造されている同時期のAIプロセッサを間違いなく上回る性能だ。

ちなみにトランジスタ数は184億個と説明されている。比較対象が難しいが、概ね同等のトランジスタ密度のZen+(GF 12nm)は48億トランジスタで213平方mmだったから、比率が同等だとすると、ダイサイズは816.5平方mmとレチクル・リミット(露光限界=ダイサイズの限界)ギリギリの巨大なダイだったことが分かる。

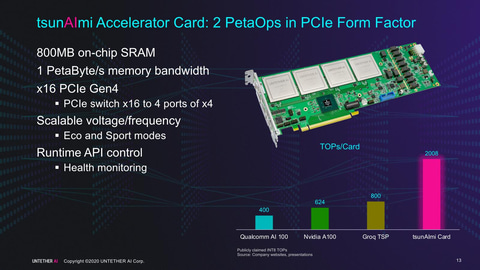

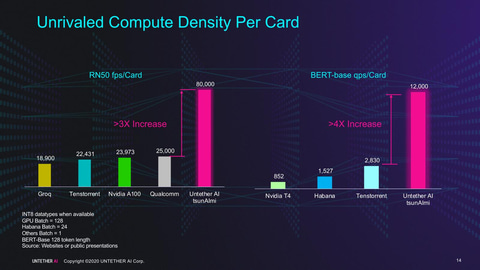

Untether AIはこのrunAI200を4つ搭載したPCIeカードをtsunAImi Accelerator Cardとして用意(図6)し、競合製品を大幅に上回る性能を実現できる、としていた(図7)。

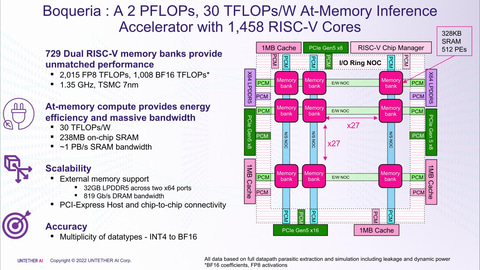

この2年後のHot Chips 34で、同社は「Boqueria」という次世代チップを発表する(図8)。runAI200ではINT8とFP32のみだったデータ型のサポートはINT4/FP8/BF16となり、メモリバンクの数も729(27×27)に増強。ピーク性能はFP8で2PFlops、BF16でも1PFlopsであり、効率は30TFlops/Wと大幅に改善された。

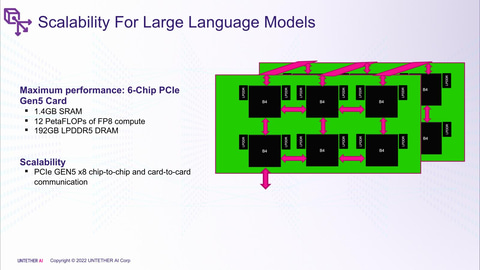

もっとも発表時点ではまだチップは存在しておらず、これはあくまでもシミュレーションでの数値である。計画ではこのBoqueriaチップを6つ、1つのカードに搭載したカードを開発することになっており、これは2024年10月にSpeedAI 240 Slimとして発売開始された(図9、10)。

このSpeedAI 240 Slimは2024年11月のMLPerf v4.1のDatacenter Inferenceに結果を登録しており、「Dell PowerEdge R760xa」(Xeon Gold 6448Y×1)に6枚のSpeedAI 240 Slimを搭載した構成で、ResNet-50のOfflineで334,462 Samples/sec、Serverで309,752 Queues/secの記録を残した。

この数値はなかなかのもので、これを上回っているのはH100-SXM-80GB×8の構成のシステム(どちらも大体スコア70万程度)しかない状況である。SpeedAI 240 Slimの価格は非公開であったが、概ね1枚1万ドル前後だったらしく、コスト的に言えばH100-SXM-80GBが3~4万ドルあたりなことを考えるとかなりコストパフォーマンスは良い(し、性能/消費電力比もかなり優秀と考えられる)。独立系のベンチャー企業でよくここまで漕ぎつけた、という感じはするのだが、このあたりで力尽きてしまったようだ。

AMDがUntether AIの技術そのものを欲しがらなかったのは、同社のAI Engine(VLIWベースのData Flow Processor)と互換性がないためだろう。もし買収してしまったらサポートも必要になるし、既存の同社のフレームワーク(ROCmやRyzen AI Softwareなど)でのサポートも必要になってくるが、全く異なるアーキテクチャをサポートするのは結構手間が掛かる。

結果、Untether AIそのものは完全に放棄されてしまいエンジニアだけが吸収されるという、なんかIntelがCentaur Technologyを買収した時のような事態が発生することになってしまった。

Untether AIはMartin Snelgrove博士ら3人によって創業されたが、そのSnelgrove博士は2019年10月までCEO、2023年7月までCTOを務めた後で退職、その後Hepzibah.AIというインメモリコンピューティングのAIプロセッサの会社を創業してCEOを務めている。

Snelgrove博士の後はXilinxでMarketingのVPを務めていたArun Iyengar氏が2024年1月までCEOを務め、次いでIntelで2022年までMobile ClientのCVPを務めていたChris Walker氏がCEOに昇格(Walker氏は2023年8月にまずPresidentとして入社)したが、この5月に退任している。実際、同社の管理チームのページをWayback Machineで見てみると、今年(2025年)4月22日時点ではWalker氏がCEOとして紹介されているのに、6月7日時点ではCEOが不在になっている。要するにVCなりファンドなりから暫定CEOすら派遣されなかったという話であり、もうこの辺でVCなどから見切りを付けられていたものと考えられる。

生き残るのが難しいAIプロセッサのマーケットとはいえ、なかなか物悲しい最後に終わったことに同情を禁じ得ない。

電源側の問題

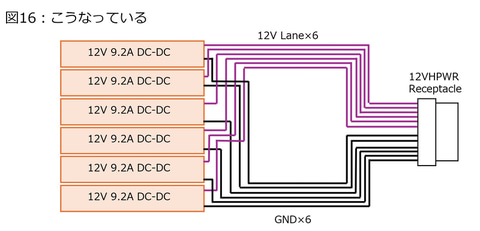

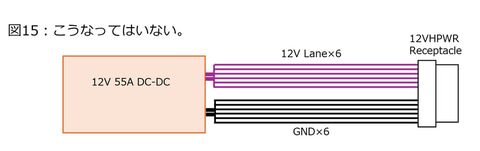

PCIe 5.0の12VHPWERコネクタの記事で色々コメントを戴いたが、結構電源に関する問題を指摘される声が多かった。どういう話か?というと、図16がおかしいという話である。というか、そんな電源がない、という指摘も多かった。

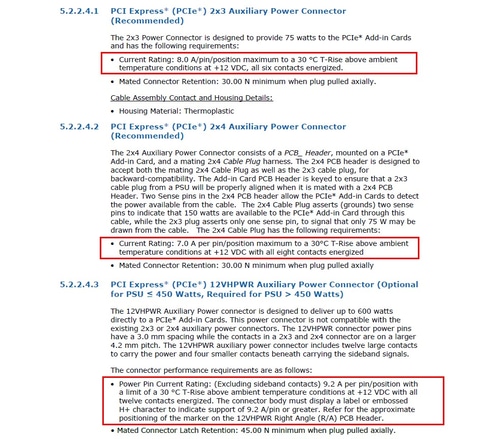

実はこの電源の話は、意図的に記事から落としていた。理由は簡単で、そもそも仕様の中で、明示的に電源ピンに流せる電流の最大値が規定されているためである(図11)。

これをきちんと実装しようと思った場合、シングルレール(前回の図15の構造)であれば、DC-DCコンバータと6本の配線の間に、それぞれ電流クランプ回路(出力電流が9.2Aを超えないようにする回路)を挟む必要がある。そのくらいなら、図16の方がいっそ実装が楽である(部品点数は増えるが)。ところが実際には図15のような電源が多数存在する……というのは、既に12VHPWRコネクタの問題ではなく、電源側の問題である。

もちろん図11を見て頂くと分かるが、2×3で8.0A、2×4で7.0Aという指定は“Required”ではなく“Recommended”であり、12VHPWRに関しても、450W以下の供給なら“Optional”で450Wを超える場合にのみ“Required”となっている。つまり、「この電源は450Wまでしか対応しません」という場合には、電流クランプ回路を持たない図15の方式でも“合法”は合法である。

実を言えば、2×3とか2×4の方も、最初期の高価格帯電源はマルチレールになっていたが、結局シングルレールでしかも電流クランプ回路なしが主流になり、それで現実に問題がほとんど出なかったから、12VHPWRでもシングルレールで電流クランプ回路なしでも大丈夫だろう、と思ったのかもしれない。

ところが12VHPWRのトラブルを見ると、電源側が要因じゃないか?という事例がいくつか見つかっている。

こっちもユーザー的にはどうしようもない話で、ちゃんと電流クランプ回路を入れてくれるか、もしくはマルチレール構成になった電源が登場するのを待つしかない。個人的には、12VHPWRコネクタを使うビデオカードは避けた方が無難ではないかと思うのだが、そうするとNVIDIAのハイエンド製品が全滅するところがまた何とも……。

DDR4 爆騰

実はこの話は別の媒体に書いたのだが、現在DDR4の値段が急騰している。

6月初頭には同容量のDDR5よりDDR4の方が価格が上がる、俗にいうビットクロス(Bit cross)が発生した。で、6月末の現在は?というのがこちら(図12)。DDR5-4800/5600の16Gbit(2G×8)が6.047ドルなのに対し、DDR4-3200の16Gbit(2G×8)は8.537ドル、同じDDR4-3200でも1G×16の方は12.750ドルと、同容量のDDR5チップの倍の値段に跳ね上がっている。

なんでこんなことに、という話は筆者の記事を検索してお読みいただくとして、今後DDR4の値段は上がることは間違いない。もし旧来のプラットフォーム(Socket AM4とかDDR4対応のLGA1700)をまだしばらく使うつもりであれば、今が増設なり交換のチャンスだろう。スポット価格がここまで高騰しており、またコントラクトが今後期待できない(DRAM大手各社は年内にDDR4の生産を終了する)となると、今後DDR4 DIMMの価格が高騰するのは必至と考えられるためだ。

それにしても、ここまで値段上がるか?というのが正直な感想ではあるのだが……。

![【Amazon.co.jp限定】 伊藤園 磨かれて、澄みきった日本の水 2L 8本 ラベルレス [ ケース ] [ 水 ] [ 軟水 ] [ ペットボトル ] [ 箱買い ] [ ストック ] [ 水分補給 ] 製品画像:3位](https://m.media-amazon.com/images/I/41n0o65dSkL._SL160_.jpg)

ThinkPad L13 GEN2 20VJS33K00 製品画像:14位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-bomber-shop/cabinet/mastertool87/251051002293800.jpg?_ex=128x128)

![内視鏡下鼻副鼻腔・頭蓋底手術 [手術動画・3DCT画像データDVD-ROM付] 第2版 CT読影と基本手技 [ 中川 隆之 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8393/9784260038393.jpg?_ex=128x128)

![盾の勇者の成り上がり 30 【電子書籍】[ 藍屋球 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7729/2000020477729.jpg?_ex=128x128)

![ゴールデンカムイ 全巻セット(1-31巻) (ヤングジャンプコミックス) [ 野田サトル ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7713/2100013057713.jpg?_ex=128x128)

![チャイロイコグマの10th Anniversary BOOK (生活シリーズ) [ サンエックス ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5606/9784391645606.jpg?_ex=128x128)

![テレビマガジン特別編集 仮面ライダー 昭和46年~48年 講談社所蔵写真集 究極 [ 講談社 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1309/9784065401309_1_3.jpg?_ex=128x128)

![頭頸部の臨床画像診断学(改訂第4版) [ 尾尻博也 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6610/9784524226610.jpg?_ex=128x128)

![ヤングジャンプ 2026 No.25 【電子書籍】[ ヤングジャンプ編集部 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/7354/2000020407354.jpg?_ex=128x128)