元半導体設計屋 筑秋 景のシリコン解体新書

ファウンダリ事業で最強プロセス技術の座を取り戻すIntel

2024年4月23日 06:21

先日、Intelがファウンダリ(半導体製造請負)ビジネスに関する更新を発表した。その内容は、今後の半導体ビジネスを考察する上で非常に重要な点が多いと感じた。また、日本でも半導体工場が新設される中で、どのように運営していくべきかを判断する参考になるだろう。

IDM 1.0から IDM2.0への戦略的移行の背景

IntelはIDM 2.0と呼ばれる、とても野心的な変革に着手するために、まず製造能力を再構築した。続いてプロセス技術と製品設計でリーダーシップを再確立し、最終的にワールドクラスのファウンダリになることを目指している。これを実現するためにファウンダリサービス部門を立ち上げた。

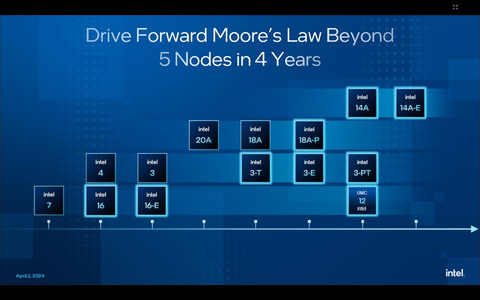

Intelはこの4年間で5ノードの実用化にこぎ着けた。最新ノードとなる「Intel 18A」は2024年末までに製造準備が整うという。Intel 18Aで設計された最初の製品は現在製造中で、すでにIntel以外に5社の顧客が量産の1つ手前までの工程にさしかかっているという。

またIntelは、次世代の「Intel 14A」以降の開発も順調に進めている。アクセラレータでAI機能を強化したXeonにより、AIでのリーダーシップにも勢いが増している。そしてクライアントでは、AI PCカテゴリを立ち上げた。PC、エッジ端末、オンプレミスサーバー、データセンター、クラウドゲームなど、上流から下流までAIにおける地位を強化している。

この戦略と製品群から、IntelはAI時代のモメンタムにそった業界随一のシステムファウンダリといえるだろう。言い換えるなら、レジリエンス(復元力/回復力)があり、信頼され、持続可能であるグローバルな新製造拠点といえる。実際現在までに、ファウンダリ事業において22兆7,000億円を超える取引額がコミットされてるという。

Intelは4月に、透明性と説明責任を推進するために必要という判断から、ファウンダリ事業と自社製品の財務報告を分離するという重要なステップを発表した。この判断の背景にも重要なポイントがいくつかあるのでそれらも触れておこう。

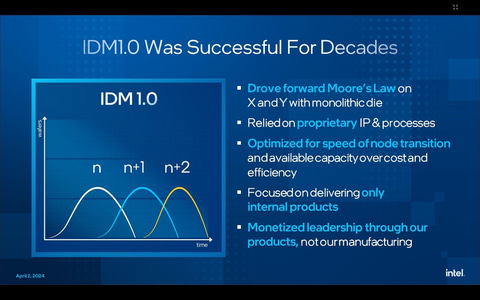

IDM 1.0はすばらしい戦略だった。世界で最も先進的テクノロジーを提供し、何十年にもわたって優れたリターンをもたらすことができた。だが、それは根本的に、2年以上のプロセス技術のリードを維持する能力に根ざしていた。プロセスの世代間移行が滞りなく実施され、そして常に世代内での改善を1回できることが前提だった。Intelならではのプロセス開発といえるだろう。

その頃はファブで使用するツールがサービス開始から数年間でフリーキャッシュフローを稼いでいたため、コストダウンや長期に資産を保持する必要はなかったようだ。Intelはそれ以上に知的財産を収益化することを選択していた。

製品においても、Intelのファブオペレーションによるキャッシュフローは、導入した設備投資に匹敵するものだったという。驚くほどの収益性だったようだ。

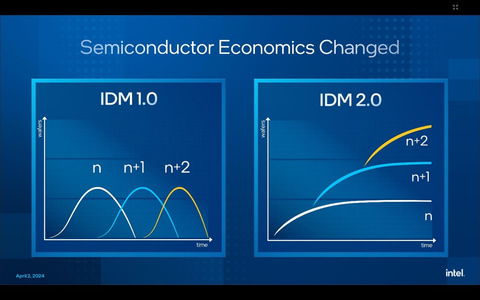

しかし、過去10年半ほどは、EUVの必要性に始まり、資本集約度(設備費用)が信じられないほど高まってきたため、1世代のプロセスノードと、それらに対応するドライバとツールの両方のライフタイムを延ばす必要があった。Intelはその新たな環境の課題に取り組んできたが、EUVの採用は遅くなった。

この資本集約度の上昇とファウンダリモデルへの根本的な移行への適応が遅れたことにより、同業他社に大きく遅れをとった。この反省がIDM 2.0戦略における原動力となっている。

3年前にパット・ゲルシンガー氏がIntelにCEOとして復帰した時に始まったIDM 2.0は、全周型トランジスタ、バックサイドパワー(裏面側からの電力供給)、High-NAリソグラフィー、アドバンスドパッケージングのプロセス技術とパッケージ技術の両方でムーアの法則を推進するすることを目的とする。

まず、ムーアの法則はX&Y次元からZ次元、つまり3つの次元全てで革新しようとしている。そしてコスト効率を最適化し、資産のライフタイムを延ばすことで、増大する資本要件にも対応していく。また、外部での設計製造製品を半導体製造ネットワークに取り込み、製品とファウンダリの両方でマージンを積み重ねて収益化することで、投資規模の課題に取り組んでいくという。

当初目標であった4年間で5ノードを超えるペースの技術開発

Intelは2月に開催した「IFS Direct Connect」というイベントで、プロセスのバリエーションを当初の目標であった4年間で5ノードを超えることを発表。そして、より成熟したノード世代(最先端ではないがプロセスとしては利用価値の高いもの)を補い、UNCおよびタワーセミコンダクターとのパートナーシップによりシステムファウンダリとしての資本資産を拡大していることなどを説明した。

4年間で集中的に5ノードを導入完了し、プロセスでのリーダーシップを確保することで、テクノロジー開発をそれまでの2年サイクルに戻し、新世代プロセス導入時のコストと効率に有意義なメリットをもたらすサイクルに入れるとしている。

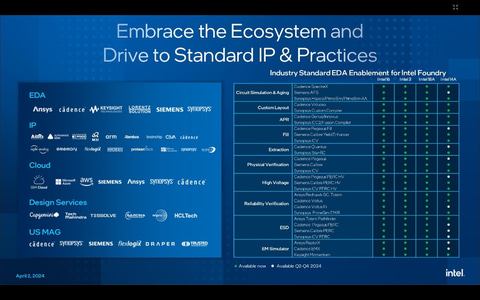

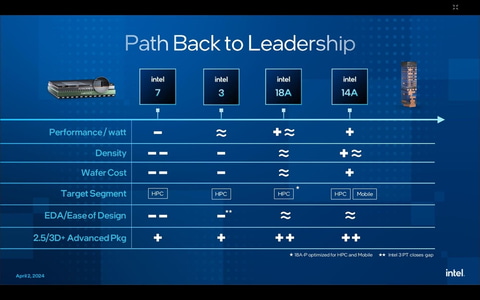

上記スライドはIPエコシステム、特に重要なEDA(Electric Design Automation)のパートナーの状況を表わしている。プロセスとパッケージの進化に合わせ、エコシステムも急速に補強した。ファブレスの潜在的な顧客のほぼ全社となる約300社と直接コンタクトし、現在Intelのファウンダリがどこまで可能になっているかを理解してもらったという。

すでにIntel 18Aは、EDAに関する項目の全てを実現しており、まもなく1.0 PDKをリリースする。Intel 14Aも完全なソリューションセットに向けて順調に進んでいる。Intel 14Aは、Intel 3やIntel 18Aと比べ、開発スケジュールが数年先を進んでいるという。EUV時代におけるIDM 1.0の課題を1つ1つ解決してきた結果なのだろう。

上記スライドは、各Intelプロセスと外部ファウンダリの同等品を比較したものだ。Intel 7では、EUVの使用を回避するため、大きなステップが必要になっていた。これにより電力性能が不十分でコストも高かった。

続くIntel 3は大きな進歩を遂げた。パフォーマンスを向上させ、密度、EDA、コストを大幅に改善した。だが、それでも業界最高水準には達していない。

それに対しIntel 18Aでは、競合他社よりも少し先を行き、電力性能やコストの大幅な改善を実現している。そして、Intel 14Aは、電力性能、密度、およびコストで他社に先んじることを期待している。また、モバイルパワーとハイパフォーマンスコンピューティングの両方を初めて最適化している。これによりファウンダリのエコシステムに対して真の包括的な製品を提供できることになる。

そしてこの比較表の最後の行にあるパッケージング技術は非常に強力なものといえる。

ムーアの法則再び

Intelは、チップレット化により、ムーアの法則をさらに進めていけるとしている。最先端プロセス技術はより小さなダイ(チップレット)として、サーバーやAIチップの設計に利用でき、製品開発を早めることができる。I/Oやアナログの最先端プロセスでのダイ使用量を減らすことで、最先端の技術をより効率的に使用できる。これは、ムーアの法則を健全に遂行するための重要な進化の1つになる。

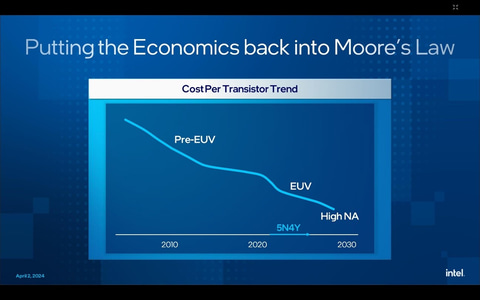

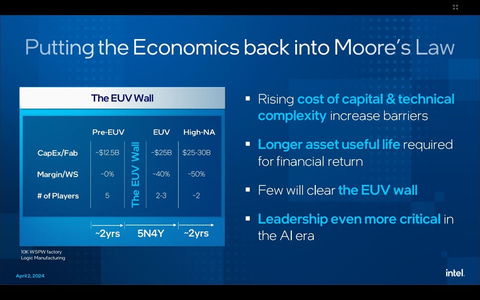

ムーアの法則は、常に電力、性能、面積、コストの最適化によって実現されている。IntelはEUVをIntel 7で採用しないというつまづきによって、競合に追いつかれてしまった。しかし、EUVは高コストで複雑なため、各社の進捗は横並びになってきている。そんな中、逆にIntelはIntel 4でEUVの壁をうまく突破し、Intel 18AではHigh-NA EUV導入への舵を切った。

ここで重要なことは、Intelが半導体製造にムーアの法則のコストメリットを再びもたらそうとしている点だ。一方、High-NA EUV以前のEUV技術を利用するメーカーの競争力はなくなるだろう。

これまでも半導体業界では10年に1度の困難さの出現により、最先端トランジスタを経済的に製造できる企業数が減少するのを我々は見てきた。EUVの採用は、まさにこの10年に1度の壁と言える。

Intelファウンダリは、Intelの大幅な利益成長を牽引するとパットCEOは説明する。2024年はファウンダリ事業の営業損失の底になり、年度内に営業利益率の改善を推進。2030年までに業界2位のファウンダリとなることを約束した。

次回の記事では、この壮大なプランにおいて、Intelが大規模な投資をしつつ、どのように健全に運営していくのかを説明する。

![5年間フル保証ディスプレイ 243B9/11 [23.8型ワイド液晶ディスプレイ 5年フル保証(USB-C)] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage15/1204657.jpg?_ex=128x128)

![巻き戻り令息の脱・悪役計画3 【電子書籍】[ 日村透 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9849/2000020509849.jpg?_ex=128x128)

製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0763/4912159850763_1_2.jpg?_ex=128x128)

![百姓貴族(9) (ウィングス・コミックス・デラックス) [ 荒川 弘 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1951/9784403671951_1_2.jpg?_ex=128x128)

![ジュニア・アンカー 中学 英和・和英辞典 第8版 オールカラー 無料アプリつき 英検対応 (中学生向辞典) [ 羽鳥 博愛 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9420/9784053059420_1_8.jpg?_ex=128x128)

![イン・ザ・メガチャーチ [ 朝井リョウ ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1045/9784296121045_1_4.jpg?_ex=128x128)

![建築知識 2026年 6月号 [雑誌] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0660/4912034290660.gif?_ex=128x128)