福田昭のセミコン業界最前線

サブ10nmロジックやメモリ、パワーなどの信頼性を支える技術がIRPS 2025に大集合

2025年3月19日 06:24

半導体デバイスの信頼性技術に関する世界最大の国際会議「国際信頼性物理シンポジウム(IRPS:IEEE International Reliability Physics Symposium)」が3月30日~4月3日に米国カリフォルニア州モントレーで開催される。

最先端の半導体テバイス、具体的には大規模ロジック回路やロジック用トランジスタ、大規模ロジック用多層配線、不揮発性メモリ(磁気メモリや強誘電体メモリ、フラッシュメモリなど)、化合物デバイス(パワーデバイスおよび高周波デバイス)、パッケージなどの信頼性に関連する研究成果が披露される。開催形式は2024年と同様、リアルとバーチャルを併用するハイブリッド開催になる。

IRPSの基本的なスケジュールは5日間で、日曜日から木曜日までを予定する。日曜と月曜の2日間は技術講座(チュートリアル)とイヤーインレビュー(前年の技術的な進展を振り返る講演:「最近の話題」と以降は表記)で構成される。今年(IRPS 2025)は20件のチュートリアルと3件のイヤーインレビューを用意した。この件数は前年(IRPS 2024)と変わらない。

前年よりも30件多い、189件の研究成果発表を予定

メインイベントである技術講演会(テクニカルカンファレンス)は火曜日から木曜日までとなる。今年は4件の基調講演(キーノート講演)、97件の一般講演、22件の招待講演、92件のポスター発表を予定する。一般発表の合計は189件となり、前年の159件から30件ほど増加した。

もう少し詳しく説明すると、3月30日(日)は午前に4件、午後に4件のチュートリアルを予定する。翌31日(月)は午前に8件、午後に4件のチュートリアルを設けたほか、夕方には3件のイヤーインレビュー(最近の話題に関する講演)を用意した。

メインイベント初日の4月1日(火)はチェア(議長)による開会挨拶から始まる。続けて午前に2件の基調講演(キーノート講演)を予定する。その後は技術講演会(テクニカルカンファレンス)のセッションとなる。午前の後半と午後をあわせて合計で9個のセッションを予定する。時間枠(タイムスロット)は3つ(午前に1つ、午後に2つ)あり、同時に3個のセッションを同時並列に実施する。夕方はレセプション、その後にワークショップ(討論会)と進む。ワークショップは前半に6テ―マ、後半に6テーマに分かれて討論を実施する。

メインイベント2日目の4月2日(水)は午前の最初に1件のキーノート講演があり、その後は夕方まで技術講演会のセッションとなる。午前と午後の合計で12個のセッションがある。タイムスロットは4つ(午前と午後に2つずつ)あり、前日と同様に3個のセッションを同時並列に実施する。夜にはポスター発表のセッションを予定する。

最終日の4月3日(木)も、午前の最初に1件のキーノート講演がある。その後は午後まで技術講演会となる。合計で9個のセッションを予定する。タイムスロットは3つ(午前に2つ、午後に1つ)あり、前日と同様に3個のセッションを同時並列に実施する。夕方にはチェアによる閉会挨拶と次回予告がある。

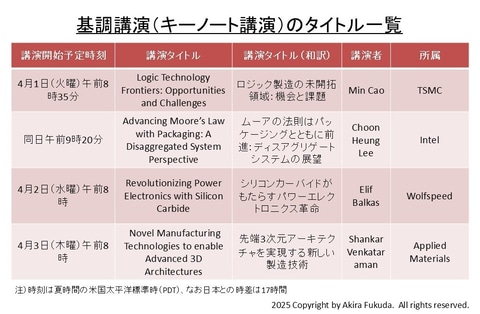

キーノートではTSMC、Intel、Wolfspeed、Applied Materialsが講演

すでに述べたように3日間で4件の基調講演(キーノート講演)を予定する。初日は始めにTSMCのMin Cao氏が「Logic Technology Frontiers: Opportunities and Challenges(ロジック製造の未開拓領域:機会と課題)」と題して、ロジック製造技術の将来を展望する。続いてIntelのChoon Heung Lee氏が「Advancing Moore's Law with Packaging:A Disaggregated System Perspective(ムーアの法則はパッケージングとともに前進:ディスアグリゲートシステムの展望)」と題して、パッケージング技術の活用による「ムーアの法則」の継続について述べる。

2日目はWolfspeedのElif Balkas氏が「Revolutionizing Power Electronics with Silicon Carbide(シリコンカーバイドがもたらすパワーエレクトロニクス革命)」と題し、シリコンカーバイド(SiC)デバイスによってパワーエレクトロニクスがどのように変革されていくかを概観する。

最終日はApplied MaterialsのShankar Venkataraman氏が「Novel Manufacturing Technologies to enable Advanced 3D Architectures(先端3次元アーキテクチャを実現する新しい製造技術)」と題し、3次元集積化をさらに進化させる新たな製造技術を説明する。

30の技術講演セッションを3日間で実施

技術講演会(テクニカルカンファレンス)の口頭発表では、最大で3つのセッションが同時進行する(「パラレルセッション」と呼ばれる)。少し詳しく見ていこう。

技術講演会初日である4月1日の午前(後半)は、「Transistors(トランジスタ)」、「SiC Devices(炭化シリコン(SiC)デバイス)」、「Emerging Memory(次世代メモリ)」の3セッションが同時並行で実施される。それぞれ4件の講演を予定する。

同日午後は、前半と後半の2つのタイムスロットがある。前半は「GaN Devices(窒化ガリウム(GaN)デバイス)」、「Packaging & 2.5/3D Assembly(パッケージングと2.5/3次元組み立て)」、「Reliability Testing(信頼性試験)」の3セッションが並列に進む。講演数は4件、3件、4件である。後半は「Gate/MOL Dielectrics(ゲートとコンタクトの誘電体)」、「Failure Analysis(不良解析)」、「Radiation Effect Reliability(放射線が信頼性に与える影響)」の3セッションが同時並行に実施される。いずれのセッションも5件の講演を予定する。

技術講演会の2日目である4月2日の午前は、前半と後半のタイムスロットがある。前半は「Product Reliability(製品の信頼性)」、「SiC Devices」(2回目)、「Metallization/ BEOL Reliability(多層配線工程の信頼性)」の3セッションが並列に進む。いずれも3件の講演を予定する。後半は「Transistors」(2回目)、「Emerging Memory」(2回目)、「Metallization/ BEOL Reliability」(2回目)の3つのセッションを同時並行で実施する。講演件数はいずれも4件である。

同日の午後も、前日と同様に前半と後半のタイムスロットがある。前半は「Packaging & 2.5/3D Assembly」(2回目)、「Circuit Reliability & Aging(回路の信頼性とエージング)」、「ESD and Latchup(静電気放電とラッチアップ)」のセッションが同時並行で進む。講演件数はいずれも3件である。後半は「GaN Devices」(2回目)、「Process Integration(プロセス集積化)」、「System Electronics Reliability(電子システムの信頼性)」の3つのセッションを並列に実施する。発表件数はいずれも5件を予定する。

技術講演会の最終日である4月3日の午前も、前日と同様に前半と後半のタイムスロットがある。前半は「GaN Devices」(3回目)、「Circuit Reliability & Aging」(2回目)、「Neuromorphic Computing Reliability(ニューロモルフィック計算の信頼性)」の3つのセッションが同時に進む。講演件数はいずれも3件である。後半は「Reliability Testing」(2回目)、「Product Reliability」(2回目)、「Neuromorphic Computing Reliability」(2回目)のセッションを並列に実施する。発表件数は3件、3件、4件である。

3日午後は前半のタイムスロットしかない。「Gate/MOL Dielectrics」(2回目)、「Memory Reliability(メモリの信頼性)」、「RF/mmW/5G(高周波/ミリ波/第5世代)」のセッションが同時並行で進む。講演件数はいずれも5件である。同日午後の後半は、閉会挨拶となる。

化合物半導体デバイスのセッションが全体の6分の1と多い

プログラムを通じて感じるのは、化合物半導体関連のセッション数の多さだろう。全体で30セッションがある中で、GaNデバイスのセッションは3つ、SiCデバイスのセッションは2つと少なくない。化合物半導体だけで全体の16.7%を占める。同一テーマのセッションが3つあるのはGaNデバイスだけ。セッションが2つあるのはSiCデバイス、トランジスタ、次世代メモリ、配線とBEOLの信頼性、回路の信頼性とエージング、信頼性試験、製品の信頼性、ニューロモルフィック計算の信頼性、ゲート/MOLの誘電体である。

GaNデバイスはパワーデバイスまたは高周波デバイス、SiCデバイスは高耐圧パワーデバイスへの応用を想定した研究の講演が目立つ。そこでまずはGaNデバイスに関する注目講演をご紹介したい。

寿命の予測や正孔の役割など、GaNパワーデバイスの理解が進む

ルネサス エレクトロニクスは、横型GaNパワーHEMTの加速寿命試験の新しい手法を開発した(講演番号3A.1)。従来の加速因子である温度と電圧に加え、第3の加速因子として2次元電子ガス(2DEG)密度を採用した。高電圧印加で懸念されるバッファの絶縁破壊を防ぎつつ、ゲートドレイン間の不良を正確に評価できる。3つの加速因子を組み込んだ寿命モデルを新たに構築し、実際のデバイスで評価した。

Power Integrationsは、定格電圧が1,250Vと高い横型GaN HEMTの信頼性試験結果を報告する(講演番号3A.2、招待講演)。HTRB(高温逆バイアス)試験、H3TRB(高温高湿逆バイアス)試験、DHOL(動的高温動作寿命)試験を実施した。Si MOS FETとのカスコード構成回路では2,000Vまでオフ状態を維持した。

The National Tsing Hua Universityと Device Dynamics Labは共同で、パワースイッチやRFパワーアンプに使用されるGaN-on-Si HEMTの信頼性、ロバスト性、安定性におけるホール(正孔)の役割を調べた結果を発表する(講演番号8A.1、招待講演)。AlGaNスペーサがホールの蓄積を強化することで、pチャンネルGaN HEMTのESD耐性が向上すること、RFアンプ用ディプリーションGaN HEMTでAlGaNバックバリアを組み込むと、2次元ホールガスによって基板損失が減少することなどを見出した。

TU WienとKAI GmbH、Infineon Technologies AGは共同で、GaN-GIT(ゲート注入トランジスタ)にAlGaNバックバリアを導入することで2次元ホールガス(2DHG)が生成し、動的オン抵抗(RDSon)の回復がどのように改善されるかを調べた(講演番号8A.4)。測定とTCADシミュレーションから、ゲートバイアスによる回復の加速には2DHGの電荷再分布が影響していることが示された。

University of Bolognaとimecなどの研究チームは、順方向バイアスを与えたショットキーpチャンネルGaNゲートHEMTのRTN(ランダムテレグラフ雑音)を包括的に解析した(同8A.2)。製造後に動作させていない状態(フレッシュ状態)かつ高温下にあるHEMTのランダムテレグラフ電流は3つの成分で構成されることが分かった。温度依存性の評価から、雑音を発生させる捕獲準位の活性化エネルギーを求めた。低温下ではHEMT電流にRTN成分は含まれなかった。

Raytheonは、ウエハースケールの銅ダマシンベース異種集積化技術によってGaNモノリシックマイクロ波IC(MMIC)とSOI CMOS回路を直径200mmのSiウエハーに統合した(11C.3、招待講演)。デジタルビーム形成方式のミリ波フェーズドアレイ回路に適する。Raytheonはこの技術をライセンス供与する用意があるとする。

そのほかのテーマ、すなわちSiCデバイスやプロセッサ、メモリ、トランジスタ、多層配線、パッケージ、放射線影響などに関する注目講演は機会を改めて紹介する。

![[アウトレット] ゲーミングモニター ホワイト パステル ブルー 200hz 24インチ pcモニター 144Hz 165Hz対応 モニター 白 フルHD IPS HDR ノングレア スピーカー搭載 VESA 23.8インチ 液晶ディスプレイ Pixio ピクシオ 公式 PX248WAVE 製品画像:15位](https://thumbnail.image.rakuten.co.jp/@0_mall/pixiogaming/cabinet/outlet/px248w-outlet.jpg?_ex=128x128)

![【★東証上場の安心企業】iiyama 液晶ディスプレイ ProLite XUB2497HSN-B2 [23.8インチ] 製品画像:14位](https://thumbnail.image.rakuten.co.jp/@0_mall/mitenekakakubamboo/cabinet/01113290/imgrc0099703098.jpg?_ex=128x128)

![【エントリーで最大全額ポイント還元|5/6まで】 I-O DATA|アイ・オー・データ USB-C接続 PCモニター フリースタイルスタンド(5年保証) ブラック LCD-C242SDB-FX [23.8型 /フルHD(1920×1080) /ワイド /100Hz] 製品画像:12位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/13736/00000014311253_a01.jpg?_ex=128x128)

![これが本当のSPI3だ! 2028年度版 【主要3方式〈テストセンター・ペーパーテスト・WEBテスティング〉対応】 (本当の就職テスト) [ SPIノートの会 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5887/9784065415887.jpg?_ex=128x128)

![神達に拾われた男(16) (ガンガンコミックスUP!) [ Roy ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5018/9784301005018_1_3.jpg?_ex=128x128)

![雑用付与術師が自分の最強に気付くまで(コミック) : 11 【電子書籍】[ アラカワシン ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/3698/2000020463698.jpg?_ex=128x128)

![筋肉が全て 健康・不老・メンタル、人生のすべてが変わる唯一の方法 [ ガブリエル・ライオン ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0507/9784478120507_1_3.jpg?_ex=128x128)

![例解学習漢字辞典 第九版 新装版 オールカラー [ 藤堂 明保 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7617/9784095017617_1_6.jpg?_ex=128x128)

![わたしはこれでやせました [ MEGUMI ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4512/9784478124512_1_2.jpg?_ex=128x128)

![道路橋示方書・同解説 IV 下部構造編(令和7年10月) [ 公益社団法人 日本道路協会 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8147/9784889508147_1_2.jpg?_ex=128x128)

![パルス色素レーザー治療スプリーム 形成外科医・皮膚科医のために [ 葛西 健一郎 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6388/9784830626388_1_4.jpg?_ex=128x128)