大原雄介の半導体業界こぼれ話

NVIDIAでIntelが救われた!と喜ぶのは時期尚早だと思う理由

2025年9月25日 06:00

さすがに今月、この話を避けて通るわけにはいかないだろう。既にニュース報道そのものは以下にある通りで、現時点で発表されていることはそれほど多くない。笠原一輝氏による解説もあるが、とりあえず筆者の思うことをいくつかまとめておく。

最大の焦点はIntelのデータセンターロードマップへの影響

今回の提携は、まずIntelのデータセンター側のロードマップに重大なインパクトを与えるものになっている。

まず一番影響を喰らうのが次世代AIチップのJaguar Shores(コードネーム)である。これ、結末から言えばおそらく立ち消えになるだろう。理由は簡単で、今回の提携によって開発される“NVIDIA-custom x86 CPUs that NVIDIA will integrate into its AI infrastructure platforms”とJaguar Shoresはターゲットとする市場がモロ被りになり、そして明らかにNVIDIAカスタムx86の方が競争力があるからだ。

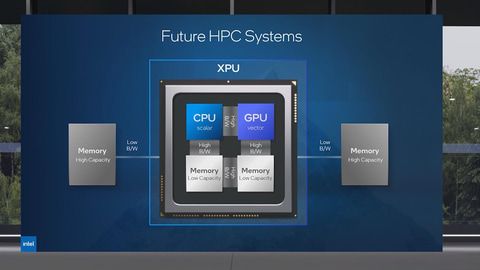

Jaguar ShoresはFalcon Shoresの後継と予定されていた製品であるが、そのFalcon Shoresはx86とXe HPC GPUを1つのパッケージの中に収めたハイブリッド構成を予定していた(図1)。

2024年12月に行なわれたBarclays 22nd Annual Global Technology Conferenceに参加されたMichelle Johnston Holthaus氏(当時は暫定CEO、先日Intelを退社された)が、Falcon Shoresを市販せずに開発者向けのプラットフォームとしてのみ提供するという、まるでMercedとかLarrabeeみたいな扱いになることを発表し、市販するのはFalcon Shoresの後継製品以降になることを表明していた。

実はこのFalcon Shoreは、単にAMDのInstinct MI250Aの対抗馬(つまりHPC向けとなるCPU/GPUハイブリッドプロセッサ)というだけでなく、Gaudi 2およびGaudi 3の後継というか移行先になることも期待されている。ところがFalcon Shoresの世代ではこのGaudiからの移行にはかなりの困難が伴い、性能も出なかったようだ。

Holthaus氏は「Gaudiから第1世代のFalcon Shores (GPU)への移行を真剣に考える必要があります。正直に言って、素晴らしいものになるかと問われれば、答えはノーです。しかし、プラットフォームを完成させ、そこから学び、ソフトウェアがどのように機能し、エコシステムがどのように反応するかを理解するための良い第一歩となるでしょう」と大人的な表現でまとめていたが、要するにFalcon Shoresはこれから頑張るためのプラットフォームにしかならない、という話である。

考えうるNVIDIAカスタムx86のプラン

ではNVIDIAカスタムx86が出たらどうなるか?これはGrace HopperやRubin Veraなどと同じく、やはりCPUとGPUが密結合した構成になると考えられる。Falcon Shoresとは異なり、CPU側メモリとGPU側メモリは直接接続されない。

Grace Hopperの場合、GraceのローカルLPDDR5とHopperのHBM3Eが、NVLink C2Cを経由してキャッシュコヒーレンシが保たれるという形になっており、多分これに準ずる形になるとは思うが、それがおそらく1つのパッケージに収まって提供されるか、もしくはGrace BlackwellのようにCPUとGPUは別パッケージになり、間をNVLinkでつなぐ方式のどちらかだろう。

どちらにしても構成的にはJagure Shoresとそう変わりはないと思われる。そして既存のGaudi 2およびGaudi 3のユーザーは、Xe-HPCベースのGPUかNVIDIAのCUDAベースGPUかのどちらかに乗り換えを余儀なくされる。移行ツールはもちろんそれなりに提供されるだろうが、仮に両方が提供されたとして、どちらに将来性があると顧客が考えるかは議論の余地がないだろう。こうなると、Xe-HPCの未来も非常に怪しいものになってくる。

実際のところ、ここでJaguar Shoresの開発を止めることで、結構な開発コストをIntelは節約できることになる。Intelが用意するのは、Gaudi 2/3からCUDAへの移行ツールと、Xe-HPCアプリケーションのCUDAへの移行ツールだけだし、Xe-HPCアプリケーションに関して言えば端的に言えばユーザーがIntelのMath LibraryをCUDA-X(GPU-Accelerated Math Library)に置き換えるだけだからそう手間はかからない。

一筋縄にはいかないNVIDIAの統合

もっともIntelの地獄はここからである。まず既存のoneDNNをCUDAに対応するように変更する必要がある。まああっさりoneDNNを廃止する可能性もあるのだが。もうoneAPIを発表当時とはだいぶ状況が異なっており、oneAPI的な共通APIのニーズそのものが薄れているというか、oneAPIが時代に合わなくなってきている感は強いので、案外これはスムーズにいくかもしれないが。

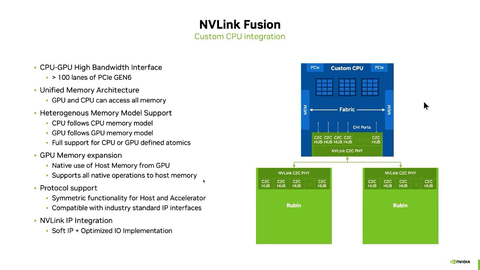

次がNVLinkへの対応である。最終的にNVIDIAカスタムx86がGrace Hopper方式(1パッケージにCPUとGPUが搭載される)か、それともGrace-Blackwellのように別チップになるかはともかくとして、ベースになるのはおそらくNVLink Fusionである。

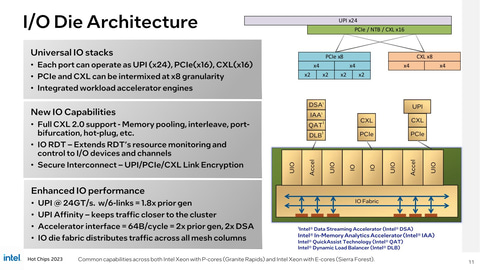

NVLink Fusionの仕様はおおよそ公開されており(図2)、ホストから見るとNVLinkは100レーンのPCIe 6.0に見える。PCIe 6.0だからレーンあたり64GT/s、つまり8GB/sであり、100レーンで800GB/sの帯域で接続される形になる。

面白いのは、このPCIeの上にArmのCHI(Coherent Hub Interface)プロトコルを通しており、そしてCHIの上にNVIDIAのGPUをアクセスするためのプロトコルが通るという多層構造だ。おそらく従来のNVLinkとNVLink Fusionの最大の違いは、このCHIを利用するか否かではないかと思うのだが、それはさておき。図2で言うと、ブルーの部分は顧客(この場合はIntel)のIPで構成されるが、グリーンはNVIDIAのIPが提供される。つまりNVLink C2C PHYはNVIDIAからIPが提供(多分RTLベース)され、これをIntelが組み込む形になるのだろう。

問題はNVIDIAのIPはIntel Foundryのことを考慮していないというか、TSMC向けのIPしか持っていないことだろう。もちろんRTLだから、原理的に言えばどこのファウンドリ/プロセスでも製造できるのは間違いないが、そこでターゲットとなる性能や消費電力、実装密度を実現できるかどうかはまた別の話であり、これはIntelとNVIDIAがこれから取り組まなければならない作業である。

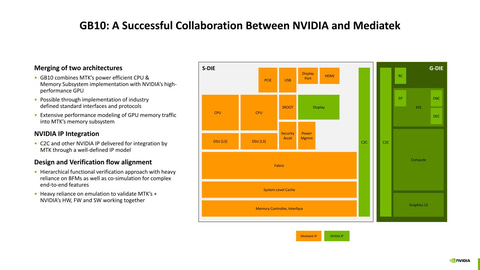

NVLink C2C PHYのIPはTSMC 3nmに対応していることはGB10で証明されている(図3)。ターゲットとなるのがIntel 18AなのかIntel 14Aなのか、それともTSMCでNVLink C2C接続専用Cチップレットを製造して(これはTSMC N3でもなんでもいいだろう)、それとIntelのCPUをUCIeでつなぐのか?方法はいろいろあるだろうが、これまでロードマップになかった作業が急遽捻じ込まれることになるわけだ。

3つ目がサーバー向け製品の基本的なアーキテクチャの見直しだ。もちろんIntelがNVIDIAカスタムx86はいわばスペシャル製品であり、通常のXeon ScalableはNVLinkへの対応は行なわないと決断すれば(もしIntel側に十分な開発リソースがないと、こうなりそうなのが怖い)必要ないが、「汎用のXeon ScalableプロセッサもNVLinkを使ってNVIDIAのGPUを接続できます」(これがないと、Xeon ScalableはPCIeでの接続しか方法がなくなる)というのは大きなアピールポイントになる。なのだが、これは一筋縄ではいかない。

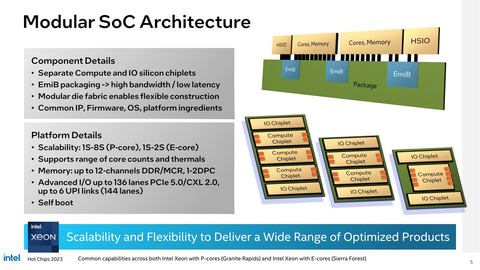

さきほど図2で示したように、NVLinkへの接続には800GB/sの帯域が必要になる。現在のXeon Scalableはこんな帯域を連続的に接続するような構造にはなっていない。Xeon 6のチップレットの構成がこちら(図4)だが、I/Oダイは全体の上下に分散しており、しかもそれほど帯域は広くない。Xeon 6のハイエンドにあたるXeon 6978PでもPCIeレーンは合計96でしかない。しかも一部はUPIとの共用になっている(図5)。そもそもI/Oダイが2つに分かれている時点でNVLinkの接続には不適であり、I/Oダイにはそれぞれ最低でも100レーンのPCIeが出てくれないと困ることになる。

「それぞれ」と書くのは、XeonにNVLinkだけをつなげば済むわけではないからで、ネットワークやCXL、そのほかのPCIeカードなどを装着できる余地を残す必要があるから、トータルすると200レーンぐらいにI/Oの能力を増やす必要がある。おまけにPCIe 6.0だから現行の2倍の速度である。要するに現在のXeon 6のI/O帯域を4倍に増やさないと辻褄が合わないことになる。

これはもう根本的にアーキテクチャレベルから見直しをする必要がある。というのはXeon 6のアーキテクチャはCPUダイ同士の接続(というか、CPUコア/L3同士の接続)と、CPUとI/Oダイの接続に、同じリングバスメッシュ(縦方向と横方向のリングバスでメッシュを構成する)の接続を共用しているからだ。なのでI/Oインターコネクトの帯域を4倍にしたいと思うと、内部のリングバスの速度そのものを4倍にしないといけない。

メモリコントローラもこのリングバスメッシュにつながれる形になっているから、たとえばメモリとI/Oダイの間だけ高速化する、といった小技は使えない。

余談だがAMDのEPYCの場合、CPUダイとI/Oダイが分離されているがゆえに、仮にEPYCにNVLink Fusionを実装しようとしてもIntelの時ほどには困ったことにはなりにくい(sIODを作り直すだけで済む)。このあたりは、限界まで最適化を進めてしまったことで、大きな変更ができないIntelのチップレットの考え方が裏目に出てしまったことになる。

最後がラインナップへの影響である。先も述べたように、もし「汎用のXeon ScalableプロセッサもNVLinkを使ってNVIDIAのGPUを接続できます」の路線に舵を切った場合、Xeonの製品ラインナップは必然的にGPUと組み合わせるのに便利なものが増えることになるだろう。なにせそこが一番売れる可能性が高いからだ。もちろんすべての用途にNVIDIAのGPUが必要というわけではないから、NVLinkなしのSKUは当然用意されるだろう。ただ今後Intelは、NVIDIAの意向を伺いながらSKUを決めることになるだろう。

全体として今回の協業により、Intelのデータセンタービジネスは短期的には勢いを取り戻すことになるかもしれない。ただし長期的にはNVIDIAのGPUあってのIntelのXeon、という立場に堕ちる可能性が否定できないものである。

ついでに言えば、そんなわけで協業をしたからといってすぐにシリコンが出てくるわけではない。対応製品が出るのは早くて来年(2026年)の今頃(9月)、実際には2027年に入ってからだろう。それまでの間は既存のXeon 6とその次のXeon 7(?)でつながなければいけない。そうそう簡単に状況が逆転するわけではないのだ。

資金が増えてもIntelのさまざまな問題は解決しない

ところで、PC Watch以外にも多くのメディアが今回の提携を報じており、その中にはNVIDIAが50億ドル分のIntelの株を購入することを決めたので、Intelの手元資金は大きく改善した(ほかにトランプ政権からの89億ドル、ソフトバンクからの20億ドルがある)ので、これを元手にIntel 14Aを量産可能とし、TSMCから先端プロセスのシェアを奪える可能性が出てきた、と評するものが少なくない。

「可能性」という意味では、これまで0%に近かったのがもう少し上がったという意味で言えばその通りだが、筆者はそこまで話は甘くないと考えている。そもそもIntel 18Aが顧客がつかなかったことも、さらに言えばその前のIntel 3やIntel 7/10、14nmなども顧客が獲得できなかったのは、別に開発資金が不足していたからではなかったはずだ。

もちろん開発資金がなければ話にならないのはその通りだが、資金があればIntel 14Aが無事完成して問題なく量産できるという話にはならない。それは別の問題であり、その問題は依然として解決していないと筆者は考える。

クライアントの方も茨の道だろう。こちらはIntelとNVIDIAの両方に問題がある。図3に戻ると、これはNVIDIAのGB10、つまり今年のCESでNVIDIAが発表したProject DIGITSに基づくDGX Spark Systemに搭載されるSoCである。BlackwellベースのGPUに、MediaTekが製造したCPU+メモリ+I/O(CPUはCortex-A925×10+Cortex-A725×10と発表されている)を組み合わせた構造である。

図3にはないが、このSoCのTDPは140Wと発表された。140WというのはGPUが100W、CPUそのほかが40Wぐらいだろうか?140Wという数字から分かるように、モバイルには全然無理で、デスクトップでも厳しい範囲である。なのでこのBlackwellベースのGPUをそのままx86に持ってきても、製品構成としては難しいことになる。次世代以降での対応になるだろう。

で、この構造のままCPUをx86に交換することを考えてみる。発表によれば、DGX Spark Systemに搭載されるSoCのSダイとGダイの間は600GB/sで接続されている。これは現在のArrow LakeのI/Oタイルの帯域(PCIe 5.0×16+Thunderbolt 4×2で74GB/sほど)の8倍以上の帯域となる。

つまり、IntelはSoCタイルの構造というか、内部のインターコネクトを完全に見直しというか再設計する必要があり、I/OタイルをNVLink C2C向けに作り替える程度の細工ではどうしようもない、という話になる。ひょっとすると2026年末にはGB86とか出てくるかもしれないが、もし出て来たとするとCPUタイルはともかくSoCタイルは完全に作り直しになるだろう。

ただクライアントがすべてAI推論の性能が必要というわけではないし、そもそもフルHDでのゲーミングができれば十分という層も存在する。NVIDIAはクライアント向けにはNVLinkを公開していないから、こちらはPCIe接続で十分と判断される。こうした向けの内蔵GPUというのは、要するに現在のIntel Xe2を置き換える用途ということになるが、ここで最大の問題はNVIDIAが低消費電力設計に非常に不慣れということだ。

BlackwellのローエンドといえばGB207になる。GeForce RTX 5050だが、これでもTDPは130Wで、到底内蔵GPUには適さない。GB10のものでも推定100Wだ。もっと低消費電力のものはJetson Orinシリーズがあり、AmpereベースのJetson Orinなら構成に応じて7W~60Wまで自由に選べるが、描画性能の方はXe2未満でしかない。時期から言えば次のRubinになると思うが、果たしてNVIDIAは同等の消費電力でXe2(か、この時期だとXe3の可能性もある)を上回る性能のGPUを作ることができるのだろうか?

しかもNVIDIAは、ローカルにメモリコントローラを持たないGPUの経験があまりない。ディスクリートGPUではGeForce 6200 with TurboCacheがあるが、これですらローカルに16MBのバッファを持っていた。統合GPUではGeForce 6100/nForce 400があって、これは完全にローカルキャッシュレスだが、HyperTransportを前提にした構造だから、現在のアーキテクチャに応用できるとも考えにくい。率直に言って「本当に作れるの?」がかなり疑問である。

そもそも今回の発表、割と突然決まった感がある。Webcastで見ると、Tan CEOはIntelのオフィスなのにHuang CEOは出先のホテル(この時はトランプ大統領に同行して英国に滞在していた)から、という感じからもこれは裏付けられる。トップ同士の話し合いで急遽決まったのだとしても、筆者は驚かない。ただそれを形にするエンジニアの皆さんが大変そうだなぁ、と思うだけである。とりあえず今年~来年前半には動きはないだろう。来年後半以降が楽しみである。

![DELL デル デスクトップパソコン Dell スリム[モニター無し / Windows11 Home / メモリ:16GB / SSD:512GB] ブラック SD60GH 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001749/4573661276474_1.jpg?_ex=128x128)

![[新品]メジャーMAJOR(1-78巻 全巻) 全巻セット 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0020/me-01_01.jpg?_ex=128x128)

![筋肉が全て 健康・不老・メンタル、人生のすべてが変わる唯一の方法 [ ガブリエル・ライオン ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0507/9784478120507_1_3.jpg?_ex=128x128)

![写真でスラスラわかる建築基準法 [ 関田 保行 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0162/9784767830162_1_2.jpg?_ex=128x128)

![アオのハコ 25 【電子書籍】[ 三浦糀 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2550/2000020202550.jpg?_ex=128x128)

![地球の歩き方 スター・ウォーズ [ 地球の歩き方編集室 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6939/9784058026939_1_2.jpg?_ex=128x128)

![ファイブスター物語 19 [ 永野 護 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3336/9784041173336_1_10.jpg?_ex=128x128)

![小学新漢字辞典三訂版 (光村の辞典) [ 甲斐睦朗 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0175/9784895720175.jpg?_ex=128x128)

![SAKAMOTO DAYS 27 【電子書籍】[ 鈴木祐斗 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2557/2000020202557.jpg?_ex=128x128)

![青の祓魔師 34 【電子書籍】[ 加藤和恵 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2522/2000020202522.jpg?_ex=128x128)

![呪術廻戦≡ 3 (ジャンプコミックス) [ 岩崎 優次 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0429/9784088850429_1_9.jpg?_ex=128x128)