大原雄介の半導体業界こぼれ話

製造原価が高そうなPanther Lakeと、対応拡張命令の謎

2025年10月23日 06:12

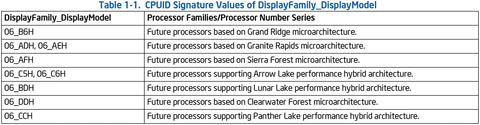

将来のCPUのDisplayFamilyとDisplayModel

2025年1月に「仕様書からIntel今後のコアをちょっと想像する」という記事をお届けしたが、あの記事の後も「Intel Architecture Instruction Set Extensions Programming Reference」は順調にバージョンアップを続けており、最新版のバージョンは059(2025年9月)になっている。

そんな最新版を見ていたらちょっと面白い記述を見つけたのでご紹介したい。

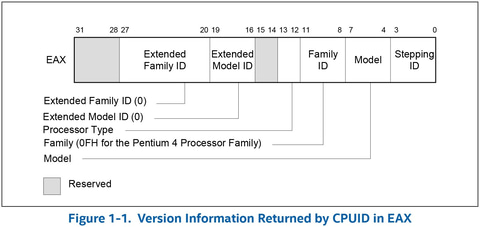

まずは「CPUID Signature Value of DisplayFamily_DisplayModel」である(図2)。これは何かといえばCPUID命令でそのCPUの特徴を取得する際に返される値である。EAXレジスタに「01H」を入れてCPUID命令を発行すると、EAXレジスタに「Family ID」や「Model ID」などが返される(図3)仕組みである。

このFamily IDとExtended Family IDを組み合わせると「DisplayFamily」が、「Model」と「Extended Model ID」を組み合わせると「DisplayModel」が示されるわけだが、当然数多くのプロセッサを出荷しているIntelではこれが膨大な量になる(図3)。

余談だが、AMDとかVIA(というかCentaur)、あと多分兆芯なんかもこの辺は独自に値を設定していると思われるので、CPU-Zのようなソフトを開発する場合はこうしたメーカーの情報も別途入手する必要がある。

話を戻すが、Version 059には「Wildcat Lake」および「Nova Lake Desktop」「Nova Lake Mobile」が新たに追加された(図4)。Wildcat Lakeは以前から噂されていた、Intel Processor系列などのバリュー向けCPUと目される製品である。詳細は不明だが、LGAパッケージではなくBGAパッケージが用意されている模様で、また新規の拡張命令への対応がないので、既存のコア(それがモノリシックなRaptor Lakeベースなのか、それともMeteor Lake/Lunar Lake/Arrow Lakeなどのチップレット構成のものなのかも不明)の機能縮小版と考えられる。

ちなみに図4で分かるようにWildcat Lakeも「hybrid architecture」と明記されているので、PコアとEコアの組み合わせとなる。Pコアの方はCPUタイルに搭載されているものを使うとして、Eコアの方が同じくCPUタイルのEコアを使うのか、それともRaptor Lake以外でSoC Tileに搭載されているLP Eコアを使うのか(あるいは両方使うのか)は定かではない。

一部報道にはPanther Lakeのサブセットの可能性も指摘されていたが、それだと後述するように拡張命令のサポートがあっても良さそうであり、その可能性は薄いのではないかと思われる。

というか、Panther Lakeの原価は結構なものになりそうで、バリュー向けには正直厳しいように思われる。Intel 4を使うMeteor Lakeや、TSMC N3Bを使うLunar LakeやArrow Lakeでも厳しそうで、個人的にはIntel 7のRaptor Lakeベースではないかと予想する(この話はまた後で)。

その話は後にして、ポイントはNova Lakeが公式に出現したことだろうか。デスクトップとモバイルが別々のDisplayModelになっているということは、物理的に構成が異なる(おそらくArrow Lake同様にSoCタイルは共通で、CPUタイル/GPUタイルの構成が異なるとか、IOタイルがなくなるとか、そういう感じだろう)のではないかと思われる。

ついでに、表1にVersion 053以降のこのDisplayFamily_DisplayModelとして示されるものの変遷をまとめてみた。

| Version | 053 | 054 | 055 | 056 | 057 | 058 | 059 |

|---|---|---|---|---|---|---|---|

| 公開日 | 2024年6月 | 2024年10月 | 2024年10月 | 2024年12月 | 2025年3月 | 2025年6月 | 2025年9月 |

| 06_B6H | Grand Ridge | ← | ← | ← | ← | ← | ← |

| 06_ADH, 06_AEH | Granite Rapids | ← | ← | ← | ← | ← | ← |

| 06_AFH | Sierra Forest | ← | ← | ← | ← | ← | ← |

| 06_B5H | Arrow Lake U | ← | ← | ← | ← | ← | |

| 06_C5H, 06_C6H | Arrow Lake | ← | ← | ← | ← | ||

| 06_C5H | Arrow Lake H | ← | |||||

| 06_C6H | Arrow Lake S | ← | |||||

| 06_BDH | Lunar Lake | ← | ← | ← | ← | ← | ← |

| 06_DDH | Clearwater Forest | ← | ← | ← | ← | ← | ← |

| 06_CCH | Panther Lake | ← | ← | ← | ← | ← | ← |

| 13_00H, 03_01H | Diamond Rapids | ← | ← | ← | ← | ← | |

| 06_D5H | Wildcat Lake | ||||||

| 12_01H | Nova Lake Desktop | ||||||

| 12_03H | Nova Lake Mobile |

面白いと思うのは、Version 058まではArrow Lake HとSの区別が明確ではなかったことだろうか。あるいは、以前はArrow Lake SをArrow Lake Hとしてリリースする(あるいはその逆の)計画があったのだが、それが取りやめになったので後からこの区別を追加したのかもしれない。

あと、Diamond RapidsとNova Lakeがどちらも新しいDisplayFamily(13H/12H)になっていることも目を惹く。単にこれまで使っていた06Hがそろそろいっぱいになってきたので新しい番号を割り当てたのか、それともこの世代から何か新しいアーキテクチャが採用されるという話なのか、そのあたりは定かではないのだが、興味深い。

それから、Diamond RapidsにはDisplayModelが00Hと01Hの2種類あるのも面白い。XCCとHCCで分けているという話かもしれないのだが、XCCとMCC、HBMの3種類のダイがあるSapphire Rapidsは06_BFHで全部共通、というあたり、必ずしもダイの構成を反映しているわけでもなさそうで、どう分けているのか知りたいところだ。

とりあえずNova LakeとWildcat Lakeという2種類のコアが公式にリリースに向けて進んでいることは今回のアップデートで明らかになった。

さらに余談であるが、将来のプロセッサとして公式に明らかになっているものに「Coral Rapids」がある。これはLip-Bu Tan CEOが2025年第2四半期のカンファレンスコールの中で、Wells FargoのAaron Rakers氏の「Diamond Rapidsは2026年後半に投入されると考えて良いのか?」という質問に「(Diamond Rapidsの投入時期は)前後半年程度の誤差はあると思う」と答えた後で、「次世代のCoral Rapidsは2028~2029年頃を予定している」と述べており、製品計画があることは確定している(出荷まで漕ぎつけられるか、はまた別の問題だが)。

ただこちらはまだ先過ぎるためか、DisplayFamily_DisplayModelのテーブルには示されていない。

拡張命令テーブルの謎

ここまで書いたので、では拡張命令テーブルの方も見てみたい。前回の記事では表1としてVersion 049~Version 056までの変遷をご紹介したので、今回表2にVersion 056~Version 059の変遷をまとめてみた。

| Version | 056 | 057 | 058 | 059 |

|---|---|---|---|---|

| 公開日 | 2024年12月 | 2025年3月 | 2025年6月 | 2025年9月 |

| AVX512_VP2INTERSECT | Tiger Lake | ← | ← | ← |

| TSX Suspend Load Address Tracking (TSXLDTRK) | Sapphire Rapids | ← | ← | ← |

| Advanced Matrix Extensions (AMX) | Sapphire Rapids | ← | ← | ← |

| User Interrupts (UINTR) | Sapphire Rapids, Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake | ← | Sapphire Rapids, Sierra Forest, Grand Ridge, Arrow Lake H | ← |

| Trust Domain Extensions (TDX) | Emerald Rapids | ← | ← | ← |

| Linear Address Masking (LAM) | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| IPI Virtualization | Sapphire Rapids, Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake | ← | Sapphire Rapids, Sierra Forest, Grand Ridge, Arrow Lake H | ← |

| RAO-INT | Future processors | ← | ← | ← |

| PREFETCHIT0/1 | Granite Rapids, Clearwater Forest | ← | ← | Granite Rapids, Clearwater Forest, Nova Lake |

| AMX-FP16 | Granite Rapids | ← | ← | ← |

| CMPCCXADD | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| AVX-IFMA | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| AVX-NE-CONVERT | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| AVX-VNNI-INT8 | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| RDMSRLIST, WRMSRLIST, and WRMSRNS | Sierra Forest, Grand Ridge, Panther Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Panther Lake, Diamond Rapids | ← |

| Linear Address Space Separation (LASS) | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| Virtualization of guest accesses to IA32_SPEC_CTRL | Sapphire Rapids, Sierra Forest, Grand Ridge, Panther Lake, Diamond Rapids | ← | ← | ← |

| UC Lock Disable Causes #AC | Sierra Forest, Grand Ridge | ← | ← | ← |

| LBR Event Logging | Sierra Forest, Grand Ridge, Arrow Lake S (06_C6H), Lunar Lake, Diamond Rapids | Sierra Forest, Grand Ridge, Arrow Lake S (06_C6H), Lunar Lake, Diamond Rapids | Sierra Forest, Grand Ridge, Arrow Lake S, Diamond Rapids | ← |

| AMX-COMPLEX | Granite Rapids D (06_AEH), Diamond Rapids | ← | ← | ← |

| AVX-VNNI-INT16 | Arrow Lake S (06_C6H), Lunar Lake, Clearwater Forest, Diamond Rapids | ← | Arrow Lake S, Clearwater Forest, Diamond Rapids | ← |

| SHA512 | Arrow Lake S (06_C6H), Lunar Lake, Clearwater Forest, Diamond Rapids | ← | Arrow Lake S, Clearwater Forest, Diamond Rapids | ← |

| SM3 | Arrow Lake S (06_C6H), Lunar Lake, Clearwater Forest, Diamond Rapids | ← | Arrow Lake S, Clearwater Forest, Diamond Rapids | ← |

| SM4 (VEX) | Arrow Lake S (06_C6H), Lunar Lake, Clearwater Forest, Diamond Rapids | ← | Arrow Lake S, Clearwater Forest, Diamond Rapids | ← |

| SM4 (EVEX) | Diamond Rapids | ← | ← | ← |

| UIRET flexibly updates UIF | Sierra Forest, Grand Ridge, Arrow Lake, Lunar Lake, Diamond Rapids | ← | Sierra Forest, Grand Ridge, Arrow Lake H, Diamond Rapids | ← |

| Total Storage Encryption (TSE) and the PBNDKB instruction | Future processors | ← | ← | Panther Lake |

| Advanced Vector Extensions 10 Version 1(AVX10.1) | Granite Rapids | ← | ← | ← |

| URDMSR and UWRMSR instructions | Clearwater Forest, Diamond Rapids | ← | Clearwater Forest, Diamond Rapids | Clearwater Forest |

| Flexible Return and Event Delivery (FRED) and the LKGS instruction | Panther Lake, Clearwater Forest, Diamond Rapids | ← | ← | ← |

| NMI-Source Reporting | Panther Lake, Clearwater Forest, Diamond Rapids | ← | Clearwater Forest | ← |

| User-Timer Events and Interrupts | Clearwater Forest | ← | ← | ← |

| APIC-Timer Virtualization | Clearwater Forest | ← | ← | ← |

| Management of IA32_SPEC_CTRL by VMX transitions | Clearwater Forest, Diamond Rapids | ← | ← | ← |

| Intel Processor Trace Trigger Tracing | Clearwater Forest | ← | ← | ← |

| Monitorless MWAIT | Clearwater Forest | ← | ← | ← |

| Advanced Performance Extensions (APX) | Diamond Rapids | ← | ← | ← |

| Advanced Vector Extensions 10 Version 2(AVX10.2) | Diamond Rapids | ← | ← | ← |

| Architectural PEBS | Panther Lake, Clearwater Forest, Diamond Rapids | ← | ← | ← |

| Immediate encodings for RDMSR and WRMSRNS | Clearwater Forest | ← | ← | ← |

| MOVRS and the PREFETCHRST2 | Diamond Rapids | ← | ← | ← |

| AMX-MOVRS | Diamond Rapids | ← | ← | ← |

| AMX-AVX512 | Diamond Rapids | ← | ← | ← |

| AMX-FP8 | Diamond Rapids | ← | ← | ← |

| AMX-TF32 | Diamond Rapids | ← | ← | ← |

| AMX-TRANSPOSE | Diamond Rapids | ← | Diamond Rapids | |

| RDT Region Aware Memory Bandwidth Allocation | Diamond Rapids | ← | ← | ← |

| RDT Allocation Asymmetric Enumeration | Panther Lake, Clearwater Forest, Diamond Rapids | ← | ← | |

| RDT Monitoring Asymmetric Enumeration | Panther Lake, Clearwater Forest, Diamond Rapids | ← | ← |

ただ、大きく変更はないというのが正直なところである。Version 058では結構並んでいるが、これは先に説明したようにArrow LakeがArrow Lake SとArrow Lake Hで区分けされた関係で、表記もこれに置き換わったためである。大きな変更はむしろVersion 059に集中しており、

- PREFETCHIT0/1のサポートプロセッサにNova Lakeが追加された

- Total Storage Encryption (TSE) and the PBNDKB instructionのサポートプロセッサがFuture ProcessorからPanther Lakeに変更された

- URDMSR and UWRMSR instructionsのサポートプロセッサからDiamond Rapidsが落ちた

- AMX-TRANSPOSEのサポートプロセッサからDiamond Rapidsが落ちた(というか、命令そのものが削除された)

ということになっている。あとVersion 058では

- LBR Event LoggingのサポートプロセッサからLunar Lakeが落ちている。

- NMI-Source ReportingのサポートプロセッサからDiamond RapidsとPanther Lakeが落ちている

という変更もある。NMI-Source Reportingの方は変更履歴にも明記されているし、まだ未発売のプロセッサだから影響は少ないと思うが、すでに量産出荷中のプロセッサの仕様が後から変更になって、しかもそれが変更履歴に明記されていないのはちょっと珍しい。

このサポートされる命令を、Version 059をベースにプロセッサ別に並び替えたのが表3である。前回の記事では表2にあたるものだ。その表3を見ると、まぁDiamond Rapidsに関してはまぁこんなもんかな?ということでそれほど違和感はないのだが、違和感があるのはNova Lakeである。いやPanther Lakeも結構アレだが。

| Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids | Sierra Forest | Clearwater Forest | Arrow Lake-H | Arrow Lake-S | Panther Lake | Nova Lake | |

|---|---|---|---|---|---|---|---|---|---|---|

| TSX Suspend Load Address Tracking(TSXLDTRK) | ○ | |||||||||

| Advanced Matrix Extensions (AMX) | ○ | |||||||||

| User Interrupts (UINTR) | ○ | ○ | ○ | |||||||

| Trust Domain Extensions (TDX) | ○ | |||||||||

| Linear Address Masking (LAM) | ○ | ○ | ○ | |||||||

| IPI Virtualization | ○ | ○ | ○ | |||||||

| PREFETCHIT0/1 | ○ | ○ | ○ | |||||||

| AMX-FP16 | ○ | |||||||||

| CMPCCXADD | ○ | ○ | ○ | |||||||

| AVX-IFMA | ○ | ○ | ○ | |||||||

| AVX-NE-CONVERT | ○ | ○ | ○ | |||||||

| AVX-VNNI-INT8 | ○ | ○ | ○ | |||||||

| RDMSRLIST, WRMSRLIST, and WRMSRNS | ○ | ○ | ○ | |||||||

| Linear Address Space Separation (LASS) | ○ | ○ | ○ | |||||||

| Virtualization of guest accesses to IA32_SPEC_CTRL | ○ | ○ | ○ | ○ | ||||||

| UC Lock Disable Causes #AC | ○ | |||||||||

| LBR Event Logging | ○ | ○ | ○ | |||||||

| AMX-COMPLEX | ○ | ○ | ||||||||

| AVX-VNNI-INT16 | ○ | ○ | ○ | |||||||

| SHA512 | ○ | ○ | ○ | |||||||

| SM3 | ○ | ○ | ○ | |||||||

| SM4 (VEX) | ○ | ○ | ○ | |||||||

| SM4 (EVEX) | ○ | |||||||||

| UIRET flexibly updates UIF | ○ | ○ | ○ | |||||||

| Total Storage Encryption (TSE) and the PBNDKB instruction | ○ | |||||||||

| Advanced Vector Extensions 10 Version 1 (AVX10.1) | ○ | |||||||||

| URDMSR and UWRMSR instructions | ○ | |||||||||

| Flexible Return and Event Delivery (FRED) and the LKGS instruction | ○ | ○ | ○ | |||||||

| NMI-Source Reporting | ○ | |||||||||

| User-Timer Events and Interrupts | ○ | |||||||||

| APIC-Timer Virtualization | ○ | |||||||||

| Management of IA32_SPEC_CTRL by VMX transitions | ○ | ○ | ||||||||

| Intel Processor Trace Trigger Tracing | ○ | |||||||||

| Monitorless MWAIT | ○ | |||||||||

| Advanced Performance Extensions (APX) | ○ | |||||||||

| Advanced Vector Extensions 10 Version 2 (AVX10.2) | ○ | |||||||||

| Architectural PEBS | ○ | ○ | ○ | |||||||

| Immediate encodings for RDMSR and WRMSRNS | ○ | |||||||||

| MOVRS and the PREFETCHRST2 | ○ | |||||||||

| AMX-MOVRS | ○ | |||||||||

| AMX-AVX512 | ○ | |||||||||

| AMX-FP8 | ○ | |||||||||

| AMX-TF32 | ○ | |||||||||

| RDT Region Aware Memory Bandwidth Allocation | ○ | |||||||||

| RDT Allocation Asymmetric Enumeration | ○ | ○ | ○ | |||||||

| RDT Monitoring Asymmetric EnumeratB5:L51ion | ○ | ○ | ○ |

まずPanther Lakeで言えば、Arrow Lake HでサポートされているCMPCCXADD/AVX-IFMA/AVX-NE-CONVERT/AVX-VNNI-INT8といった命令がガバっと落ちているのが気になる部分だ。あるいは後で追加されるのかもしれないが、ソフトウェア互換性を考えるとこれが落ちているのは結構不思議な感がある。

もっと謎なのがNova Lakeで、現状サポート対象になってるのがPREFETCHIT0/1のみ、というのは明らかにおかしい。こちらはArrow Lake Sの後継製品だから、AVX-VNNI-INT16/SHA512/SM3/SM4(VEX)あたりもサポートされないと困ってしまうケースが出てきそうに思うのだが、この辺も後で追加される、ということなのだろうか?ちょっとばかり謎である。

ただ、まだNova Lakeに搭載されると言われているCoyote Cove(Pコア)やArctic Wolf(Eコア)の仕様が固まっていない可能性がある。時期的に言えば、Coyote CoveはNova Lakeに加えて(先ほどちらっと話が出てきた)Coral Rapidsにも使われるかもしれないコアであり、現状はまだどの命令をクライアント向けに有効化するか決めかねているのかもしれない(といっても2028~2029年だと、Coyote Coveの次とか、さらにその次の可能性もなくはないが)。それにしてもNova Lakeは来年投入のはずなのに、えらく手間取っているなぁという感想は否めない。

Panther Lakeのダイサイズ

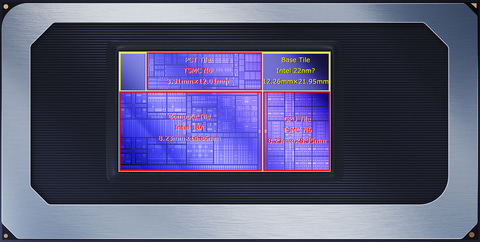

先日行なわれたIntelのTech Tour.us 2025の様子はこちらの記事などにまとまっているが、残念ながらまだ発売前製品ということで細かな寸法などは示されていない。ので、ざっくり推定してみようという試みである。

Intelの示したPanther Lakeの写真(というか、CG)を見ると、パッケージ全体の縦横比は1:2になっている。で、パッケージ全体の大きさは、Arrow Lake-Uのもの(FCBGA2049、50×25mm)とそう変わらないように見える。なので、Panther Lakeのパッケージサイズも(ボール数は異なるだろうが)やはり50×25mmと仮定した場合、3つのタイル+ベースタイルの大きさはどの程度か、をCGから算出したのがこちら(写真5)。

それぞれ、

| タイル | サイズ | 面積 |

|---|---|---|

| コンピュートタイル | 8.23×14.86mm | 122.30平方mm |

| GPUタイル | 8.23×8.95mm | 73.65平方mm |

| PCTタイル | 3.91×12.01mm | 46.96平方mm |

| ベースタイル | 12.26×21.95mm | 269.11平方mm |

となる。結構な大きさだ。特にコンピュートタイルが100平方mm超えなのはなかなかである。

さて、これの製造コストというのはもちろん不明なのだが、最近TSMCは先端ノードの値上げを行なっており、ウェハ1枚の製造コストは

- N7: 9,400ドル

- N5: 1万7,000ドル

- N3: 2万8,000ドル

- N2: 3万7,000ドル

と伝えられている(N6はN7と同等だろう)。仮にIntel 18Aの製造コストがTSMC N2と同等だと仮定、さらにDefect Density(欠陥密度)は0.1個/平方cmだとした上でそれぞれの製造コストを算出してみた(ベースの22nmに相当するものがないので、同じFinFETの14nmのコストである5,000ドルを当ててみた)。結果は?というと

| タイル名 | コスト | 歩留まり率 |

|---|---|---|

| コンピュートタイル | 85.25ドル | 88.6% |

| GPUタイル | 12.27ドル | 92.94% |

| PCTタイル | 7.76ドル | 95.43% |

| ベースタイル | 27.11ドル | 76.87% |

| タイル合計 | 132.39ドル | |

となった。これは純粋にタイルというかダイの製造費用のみであり、実際にはこれにパッケージ/テストとか実装(特にFoveros 3Dを利用してタイル同士が接続されるので、この実装コストがちょっと高い)のコストを加味すると、果たして200ドルを切れるかどうかというあたり。もちろん、これはハイエンドのCPU 16コア/GPU 12 Xeコア版の試算であって、同じことを8コア版でやってみると、寸法は

| タイル | サイズ | 面積 |

|---|---|---|

| コンピュートタイル | 8.23×11.98mm | 98.6平方mm |

| GPUタイル | 8.23× 3.41mm | 28.06平方mm |

| PCTタイル | 3.91×12.01mm | 46.96平方mm |

| ベースタイル | 12.26×15.66mm | 191.99平方mm |

となり、価格は

| タイル名 | コスト | 歩留まり率 |

|---|---|---|

| コンピュートタイル | 66.91ドル | 90.68% |

| GPUタイル | 4.54ドル | 97.24% |

| PCTタイル | 7.76ドル | 95.43% |

| ベースタイル | 17.51ドル | 82.79% |

| タイル合計 | 90.72ドル | |

となる。これにパッケージコストと実装コストを加味すると、100ドルを切るのは絶対に無理で、せいぜいが140~150ドルぐらいだろうか?先に「Panther Lakeの原価は結構なものになりそうで、バリュー向けには正直厳しいように思われる」と書いたのはこういう試算が成立するからだ。

もちろんこれはさまざまな仮定を積み重ねたものだから厳密さには欠ける試算ではあるが、大きく外れているとも思えない。やはりバリュー向けには、まだモノリシック構成の方が有利である(何しろ実装コストが下げられる)と思うのだが、さてどうだろう?

【15時14分追記】記事初出時、表が抜けておりました。お詫びして追記します。

![DELL デル デスクトップパソコン Dell スリム[モニター無し / Windows11 Home / メモリ:16GB / SSD:512GB] ブラック SD60GH 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001749/4573661276474_1.jpg?_ex=128x128)

![[新品]メジャーMAJOR(1-78巻 全巻) 全巻セット 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0020/me-01_01.jpg?_ex=128x128)

![筋肉が全て 健康・不老・メンタル、人生のすべてが変わる唯一の方法 [ ガブリエル・ライオン ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0507/9784478120507_1_3.jpg?_ex=128x128)

![写真でスラスラわかる建築基準法 [ 関田 保行 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0162/9784767830162_1_2.jpg?_ex=128x128)

![アオのハコ 25 【電子書籍】[ 三浦糀 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2550/2000020202550.jpg?_ex=128x128)

![地球の歩き方 スター・ウォーズ [ 地球の歩き方編集室 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6939/9784058026939_1_2.jpg?_ex=128x128)

![ファイブスター物語 19 [ 永野 護 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3336/9784041173336_1_10.jpg?_ex=128x128)

![小学新漢字辞典三訂版 (光村の辞典) [ 甲斐睦朗 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0175/9784895720175.jpg?_ex=128x128)

![SAKAMOTO DAYS 27 【電子書籍】[ 鈴木祐斗 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2557/2000020202557.jpg?_ex=128x128)

![青の祓魔師 34 【電子書籍】[ 加藤和恵 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2522/2000020202522.jpg?_ex=128x128)

![呪術廻戦≡ 3 (ジャンプコミックス) [ 岩崎 優次 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0429/9784088850429_1_9.jpg?_ex=128x128)