大原雄介の半導体業界こぼれ話

謎に包まれたIntelの288コアCPU「Clearwater Forest」

2025年8月28日 06:00

8月24日(米国時間)から恒例のHot Chips 2025がスタートした。概略はこちらにあるので省くとして、筆者はバーチャルで参加している。

2日目にあたる8月25日がカンファレンスデー初日で、ここのCPUセッションでIntelは「Clearwater Forest(開発コードネーム)」の詳細を公開したのだが、「あれ?」と思うことがあったので、ちょっとこの話をしたいと思う(上の写真)。

Clearwater Forestの概要

まずは発表の内容をまずご紹介したい。

Clearwater Forestは、同社のE-core Xeon 6シリーズとして現在出荷されているSierra Forestの後継にあたる。Sierra ForestベースのXeon 6xxxEシリーズは2024年6月に発表されており、今回のClearwater Forestはこの後継となるものである。

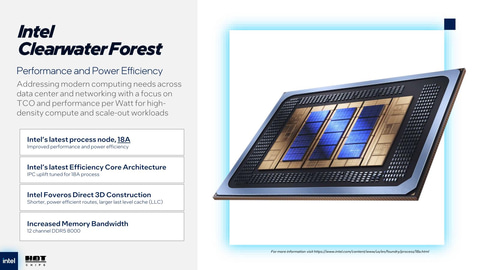

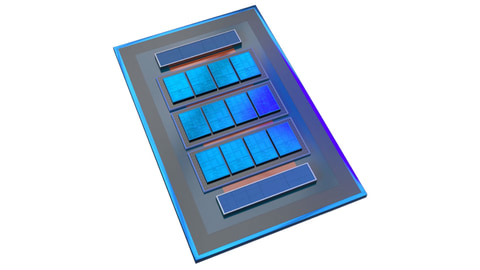

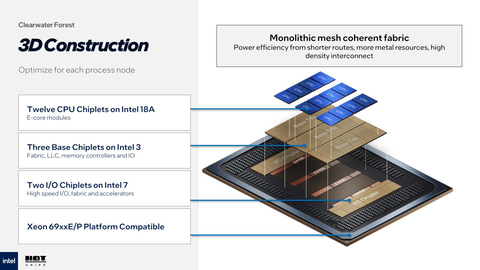

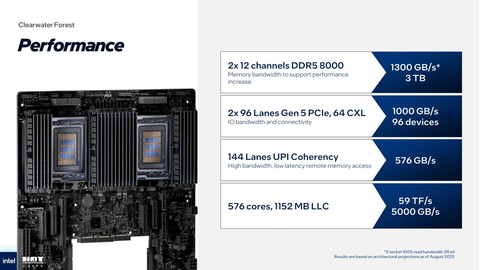

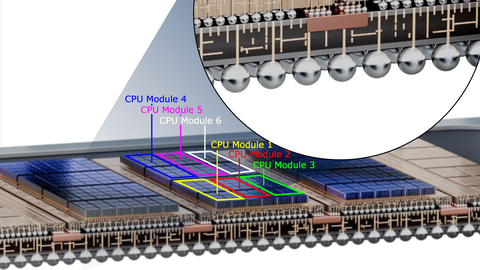

ということで、Clearwater ForestもやはりEコアをベースとした製品であり、Intel 18Aで製造されるとともに、Foveros Direct 3Dを採用している(スライド1)。この、複数のチップレットの上にさらにチップレットが載る構造そのものは、以前模式図(スライド2)が公開されており、これに沿った形と思えばそれほど違和感はない。

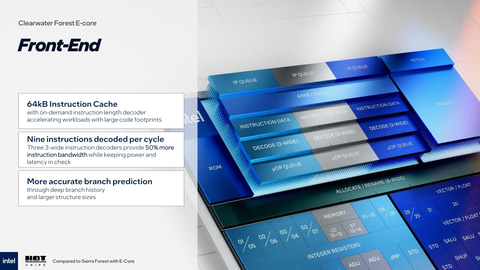

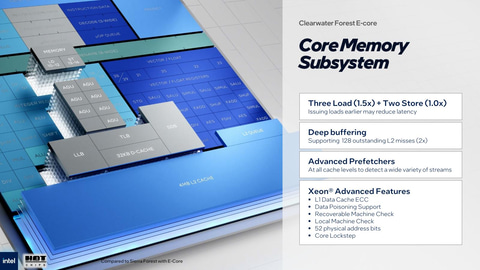

そのClearwater ForestのEコアについて、フロントエンド(スライド3)とアロケート/イシュー(スライド4)、実行(スライド5)とメモリサブシステム(スライド6)の構造は、後でもう少し詳細に見てみたいが、基本はTremont以降のEコアの構造をそのまま継承したものだ。Sierra Forestでは、Tremontに小改良を施したCrestmontコアが搭載されていたが、Clearwater ForestはCrestmontとは若干異なり、むしろLunar Lakeで搭載されたSkymontに近い気がする。

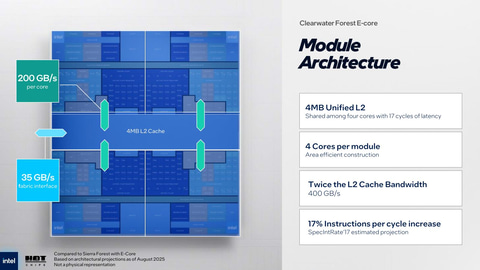

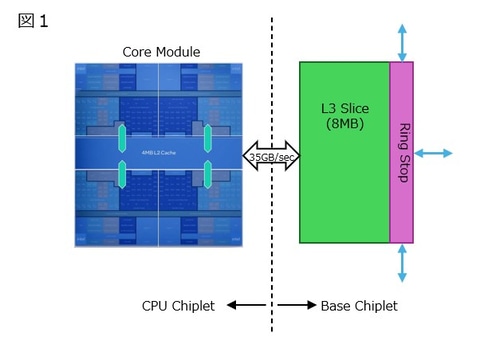

さて、Eコアは単独でも構成は可能(それを実現したのがMeteor LakeのSoCタイルに搭載されているLPEコアである)だが、基本は4コアで共有L2を搭載する形になる。Intelはこれをモジュールと呼んでいるが、モジュール内のコアとL2の間は200GB/s、モジュールとファブリックとの間は35GB/sの帯域をそれぞれ確保しているとする(スライド7)。

次が具体的な構造である。CPUはIntel 18Aで製造された12個のチップレットに格納され、それが3つのIntel 3で製造されたベースチップレットに4つずつ搭載される。さらにIntel 7で製造されたI/Oチップレットと接続されるという構造だ(スライド8)。

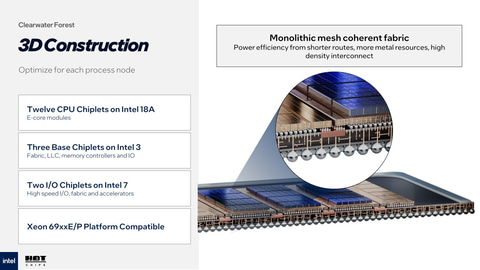

その接続部の拡大図がこちら(スライド9)。Eコアのチップレットとベースチップレットの間にはマイクロバンプが挟まれておらず、Foveros Direct 3Dでの接続であることが分かる。一方ベースチップレット同士(とおそらくベースチップレットとI/Oチップレットの間)はEMIBベースでの接続となっているように見える。

さて、今回サラッと示されたのがこちら(スライド10)。Clearwater Forestは288コア構成であり、LLCは576MBにも及ぶとされる。つまり、CPUチップレットは12個で、合計288コアである。ということは、CPUチップレットあたり24コアという計算で、スライド7で示されたモジュールが6つ、1つのCPUチップレットに搭載されていることになる。

これまでEコアのモジュールは正方形に近いという意識があった(スライド7はあくまでも説明のもので物理的形状は反映していないと注意書きがある)が、実際にはスライド11のようにModuleがかなり細長い形状になっているのかもしれない。

この288コアという数字はなかなかに意味深である。もともと2023年のIntel Innovationでは「Sierra Forestベースの288コア製品が2024年に投入される」という話になっていた。この時には144コアのSierra Forestのダイを2つ搭載したパッケージが示されたわけだが、最終的にこれは発売されずに終わっている(いやまだ出てないだけで、この後追加される可能性はなくもないのだが、少なくとも2024年中には発売されていないし、今年2月にSKUが追加された際にもなかった)。Sierra Forestでできなかったことを、Clearwater Forestで実現しようということかもしれない。

次はLLCである。Photo10にあるように、2ソケットで合計1,152MBのLLCを搭載しているので、ソケットあたり576MBになる。このLLCはスライド8で示されているように、Intel 3で製造されたベースチップレット内に収められている。なのでベースチップレットあたり192MBという計算になる。

このLLCの持ち方に関しては質疑応答の中で構成が明らかになっており、各々のベースチップレット内に8MBのL3ブロックが24個ずつ収まる格好になっているという。

謎のL3キャッシュの接続方法

問題は、これがそれぞれのコアモジュールとどういう関係になっているか、である。Pコアの場合、それぞれのCPUコアにL3が付属するような形で分散して配され、そのコア+L3がメッシュネットワークで接続されるという構図になっていた。

ただ今回の場合話が厄介なのは、コアモジュールの搭載されたチップレットと、LLCの搭載されたチップレットが別のものになっているということだ。先にスライド7の脚注で「35GB/sで足りるのか?」と書いたわけだが、それはここに絡んでくる。

考えられる構造は図1のように、各コアモジュールの共有L2と8MBのL3スライスが直接接続される形になっており、そのL3スライスの先にリングストップがあって、そこからメッシュでL3スライス同士が接続されるという構造だ。

Pコアならこの方法が多分一番簡単であり、Intelとしても手慣れた構造だから実装は容易だった。従来との違いはコアモジュールとL3スライスが物理的に異なるダイになっており、間をFoveros Direct 3Dで接続していることだけだ。この方式だとすると、Pコアと同様にL2とL3の間の信号をそのままFoveros Direct 3Dに通すだけなので、理屈的にはAMDの3D V-Cacheに近い。バスではなく配線をそのまま3Dに延長してつなぐというだけで、レイテンシもそれほど大きくはならないだろう。

しかしEコアの場合、L2にL3へのインターフェイスがもともと搭載されていない。L3をPコアと共有する構造になったSkymontベースのArrow Lakeでも、L2→L3は直接接続されるのではなく、コアモジュールからファブリック経由でL3をアクセスするようになっている。これを従来のPコア方式に改めるのは、色々影響が大きそうというのがまず最初の疑問点。

もう1つの疑問は、「そのL2とL3の帯域がたったの35GB/sec?」という点だ。L2と各コアの間が200GB/sの帯域で繋がっていることを考えると、あまりに帯域が少ないように感じられる。もちろん、ガンガンメモリアクセスを行なって、ガンガンデータを処理して吐き出す的な処理が多そうなP-cores Xeonと、たとえばAPIサーバーのようなワークロードの利用するメモリ量が圧倒的に少ない処理が多そうなE-cores Xeonでは、メモリ帯域に求められる要求が違うだろうというのは理解できるのだが、それにしてもこんなに帯域が低いのでは、そもそもL2とL3を直結させるメリットが分からない。

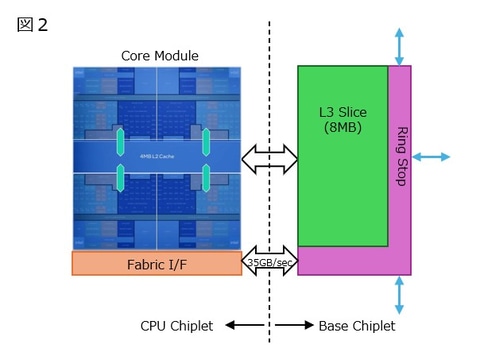

2つ目の案は、図2のようにL2/L3の接続とは別に、モジュールからファブリック接続用のインターフェイスが出ていて、このインターフェイスの速度が35GB/sというものだ(なのでL2とL3の接続速度はもっと高速)。性能の観点からすればこの図2の方がしっくりくるのだが、そういう面倒な実装にするか?と問われるとちょっと怪しいところである。

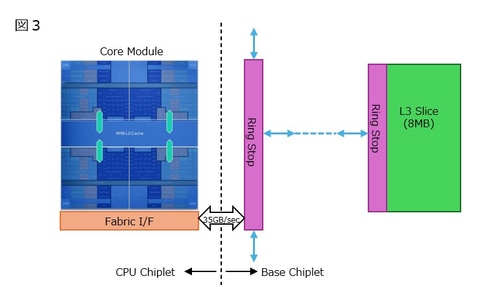

3つ目は図3のように、確かにL3はコアモジュールと同じだけの数のスライスがあるが、モジュールと接続せずにベースチップレットの先のメッシュネットワークの先に置かれているという可能性だ。つまりFoveros Direct 3D経由でL2―L3の配線を拡張するのではなく、コアからはL2までしか見えない(つまりL3はコアではなくファブリック側に属する)形にする実装だ。

実は実装そのものはこれが一番楽である。というのはそもそもEコアはL3をサポートしていないはずで、これを追加すると結構コアに激しく手を入れることになりかねないためだ。

実は質疑応答の中で、「So one socket has 576 MB of LLC (one 8 MB slice for each of the 72 quad core clusters) - is that right?」(1ソケットで576MBのLLCということは、72個の4コアクラスタの各々に8MBのスライスという理解で良いのか?)という質問に対する答えが「There are 72 8MB slices per socket」(ソケットあたり8MBのスライスが72個ある)で、そのスライスがコアモジュール(この質疑応答の表現ならコアクラスタ)と連携しているかどうかの答えを避けているのが非常に気になる部分である。図2はないだろう、とは思うのだが、図1と図3のどちらか?と言われると、筆者的には図3の可能性の方が高いように思える。このあたりはもう少し先、実際にClearwater Forestが発売されるまでははっきりしないかもしれない。

SkymontをベースとしたEコアか

コアの話に関して言えば、やはりベースとなるのはSkymontだったとして良いかと思う。スライド4の脚注に書いたように、今ひとつ辻褄が合ってないところもあるのだが、主要な構成はSkymontにかなり近い。

厳密に言えば、SkymontにXeon向けの拡張を施したもの、ということになる。これに関しては今年(2025年)1月の記事でも紹介したが、「Intel Architecture Instruction Set Extensions Programming Reference」の記述によれば、Lunar Lakeではサポートがなく、Clearwater Forestにはある拡張命令として

- PREFETCHIT0/1

- UC-Lock Disable via CPUID Enumeration

- USER_MSR/URDMSR and UWRMSR instructions

- Flexible Return and Event Delivery (FRED) and the LKGS instruction

- NMI-Source Reporting

- User-Timer Events and Interrupts

- APIC-Timer Virtualization

- Management of IA32_SPEC_CTRL by VMX transitions

- Intel Processor Trace Trigger Tracing

- Monitorless MWAIT

- Immediate encodings for RDMSR and WRMSRNS

- MOVRS and the PREFETCHST2 instruction

の12項目が挙げられ、逆に

- UIRET flexibly updates UIF

のサポートがClearwater Forestでは落ちている。

また、スライド6にもあるが、

- L1 Data ECC

- Data Poisoning Support

- Recoverable Machine Check

- Local Machine Check

- 52 physical address bits

- Core Lockstep

といった項目が追加されている。これらは多分Lunar Lakeでも実装はされていて、無効化されていたという感じ(AMDのRyzenとRyzen Pro/EPYCの関係と同じだ)だと思われる。

それとちょっと面白いのはメモリ。元々P-cores Xeon 6ではMR-DIMM(Intelの用語ではMCR-DIMM)のサポートがあり、一方E-cores Xeon 6はないという制約があった。ではClearwater Forestは?というと、DDR5-8000までのサポートが追加されたが、これはMR-DIMMではなく、ただの(という言い方も変だが)DDR5という話だった。

最近、DDR5の上限速度が6,400MT/sを超えて7,000MT/s台に到達、今年は本当に8,000MT/sに達しそうな勢いであるが、これをサポートする反面、MR-DIMMについては引き続き未サポートらしい(質疑応答でも「DDR5-8000は標準品?」「最近発売されたばかり(なのでまだ標準ではない)だが、性能向上に活用できる状態だ」というやり取りがあった)。

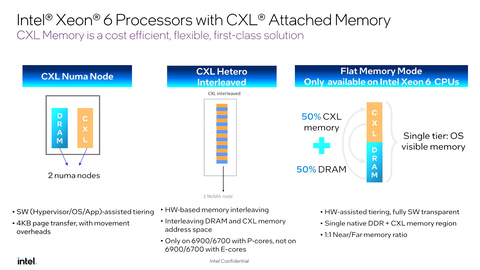

ちなみにPhoto10にはCXLを64レーン分サポートするとあるが、これはSierra Forestでもサポートされてはいた。ただ、Sierra ForestではなぜかHetero Interleavedがサポートされないという妙な制約があった(スライド12)が、Clearwater Forestでこの辺がどうなるのかは不明だ。

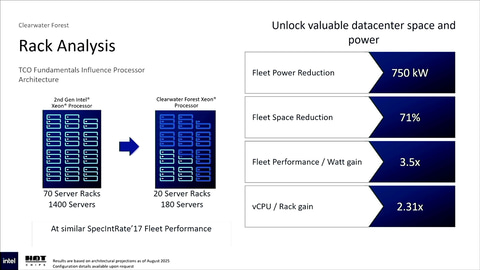

ちなみに事前配布スライドにはなく、講演で追加されたのがこちら(スライド13)だが、まぁ言いたいことは分からなくもないものの、あんまり意味がある比較とも思えない。

講演の中では、「既にラボで数カ月に渡ってテストを行なっており、量産開始は近い」としつつも、発表の時期は明らかにされなかった。またチップレットの数を減らした派生型については「技術的には可能」としつつ、実際の製品SKUについては語る立場にないとした。

Intel 18Aの難産ぶり(歩留まりがSamsungのSF2よりひどい、なんて話も伝わってきている)を鑑みると、今年中に発表されたとしても出荷は来年(2026年)以降になりそうだが、その頃にはこの構造の詳細が明らかになるといいなぁというのが筆者の願望だ。

![[台数限定価格★] ノートパソコン 店長おまかせ 最新 Windows11 Core-i5 等 八世代までCPU選択可 Core-i7 Core-i3 15.6型 SSD128GB メモリ8GB 無線LAN USB3.0 DVDドライブ 15.6インチ ノートPC パソコン 中古ノートパソコン 中古PC ノート Win11 Office付 中古パソコン 中古 製品画像:20位](https://thumbnail.image.rakuten.co.jp/@0_mall/pc-shinjyo/cabinet/pc-note/omakase-vol_r5b.jpg?_ex=128x128)

![I-O DATA|アイ・オー・データ PCモニター (5年保証) ブラック LCD-D222SD [21.5型 /フルHD(1920×1080) /ワイド /100Hz] 製品画像:12位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/11785/00000013987010_a01.jpg?_ex=128x128)

![[P10倍★8日20時〜]モバイルモニター 18.5インチ 大画面 ゲーム 映画 動画 薄型 モバイルディスプレイ フルハイビジョン ノングレア液晶 非光沢 簡単接続 スタンドカバー付 液晶モニター ポータブルモニター FHD アイリスオーヤマ DP-EF184S-B * [2606SS] 製品画像:5位](https://thumbnail.image.rakuten.co.jp/@0_mall/kadenrand/cabinet/11075038/12918368/imgrc0106186960.jpg?_ex=128x128)

![赤羽根良和の臨床 股関節 [ 赤羽根 良和 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2834/9784904862834_1_7.jpg?_ex=128x128)

![脊椎エコーのすべて 第2版 [ 山田 宏 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9464/9784784959464_1_3.jpg?_ex=128x128)

![文藝春秋 2026年 6月号 [雑誌] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0669/4912077010669_1_2.jpg?_ex=128x128)

![黄金の経験値 IX 特定災害生物「魔王」大戦バッドエンド 【電子書籍】[ 原純 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9059/2000020419059.jpg?_ex=128x128)

![10年先のわたしをつくる、家と時間 [ Emi ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2433/9784087902433_1_3.jpg?_ex=128x128)

![マイペースと歩く 3巻 【電子書籍】[ 三本阪奈 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/8648/2000020218648.jpg?_ex=128x128)

![【楽天ブックス限定特典】BULLET TRAIN ALOHA&HARU CONCEPT PHOTOBOOKアイハヨルノイロ(限定生ポストカード1枚) [ アロハ&ハル(超特急) ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6425/2100014986425.gif?_ex=128x128)

![人文知は武器になる (文春新書) [ 山口 周 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5292/9784166615292_1_9.jpg?_ex=128x128)

![宝島社スペシャルsweet6月号特別号『otona SWEET』 2026年 6月号 [雑誌] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0661/4912100370661.gif?_ex=128x128)