福田昭のセミコン業界最前線

ISSCC 2026で日本が魅せる衛星アレイ送受信器や超低消費連想メモリなどの回路技術

2026年2月17日 06:04

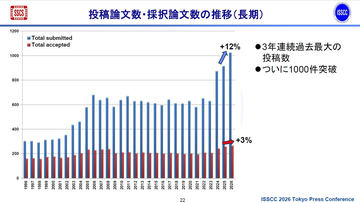

半導体集積回路の最先端技術が披露される国際学会「ISSCC(International Solid-State Circuits Conference)」が、今年(2026年)も米国カリフォルニア州サンフランシスコで始まった。本コラムの前々回ですでにご報告したように、会期(現地時間)は2026年2月15日~19日、会場はサンフランシスコ市街中心部のMarriott Marquisホテルである。

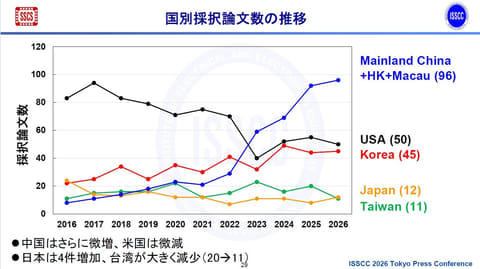

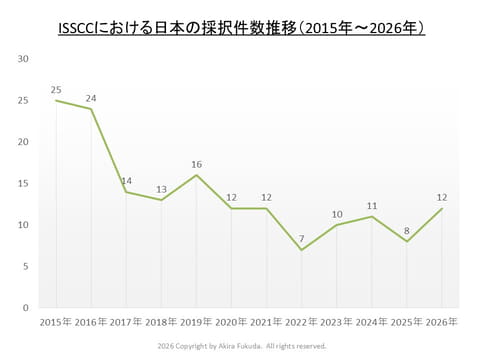

本コラムの前々回ではISSCCの開催概要、前回では注目発表をご紹介した。今回は日本からの発表をご報告する。ちなみに「日本から」とは、第1著者(論文著者が複数の場合、最初にくる著者。研究開発成果における貢献度が最も高い著者とされる)の所属組織が日本の場合を指す。ISSCCの実行委員会では国・地域別の論文数を公表する場合、第1著者の所属先をベースにカウントしてきた。

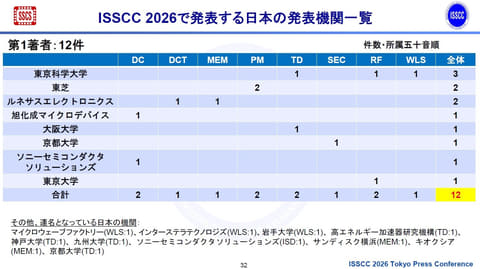

この定義によると、ISSCC 2026で日本から発表される論文の件数は12件で、前年の8件から増加した。内訳は企業が6件、大学が6件である。企業ではルネサス エレクトロニクスが2件、東芝が2件、大学では東京科学大学が3件と複数の発表を予定する。そのほかは旭化成マイクロデバイス、ソニーセミコンダクタソリューションズ、大阪大学、京都大学、東京大学が1件ずつである。

第2著者および第3以降の著者が所属する日本の発表機関は以下の通りだ。マイクロウェーブファクトリーとインターステラテクノロジズ、岩手大学が東京大学との共著(講演番号5.1)、高エネルギー加速器研究機構が東京科学大学と共著(同22.5)、神戸大学と九州大学が大阪大学などと共著(同29.5)、ソニーセミコンダクタソリューションズ(日本)がソニーセミコンダクタソリューションズ(イタリア)との共著(同7.5)、サンディスク合同会社とキオクシアがサンディスク(インド)およびサンディスク(米国)との共著(同15.1)、京都大学が南方科技大学(中国)およびソウル国立大学(韓国)との共著(同22.4)、となっている。

編隊飛行する衛星アレイの送受信器、ソフト定義車両の演算チップレット

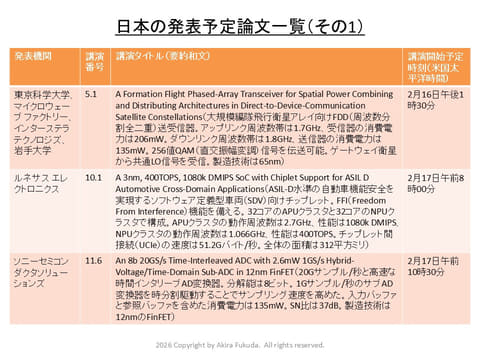

それでは日本の第1著者ベース発表機関による講演の概要をプログラムの順番に沿ってご紹介していこう。初めはセッション5、セッション10、セッション11の講演である。

東京科学大学、マイクロウェーブ ファクトリー、インターステラテクノロジズ、岩手大学の共同研究グループは、大規模編隊飛行衛星アレイ向けのFDD(周波数分割全二重)送受信器を開発した(講演番号5.1)。アップリンク周波数帯は1.7GHz、受信器の消費電力は206mW。ダウンリンク周波数帯は1.8GHz、送信器の消費電力は135mWである。256値QAM(直交振幅変調)信号を伝送可能。ゲートウェイ衛星から共通LO信号を受信する。製造技術は65nm。

ルネサス エレクトロニクスは、ASIL-D水準の自動車機能安全を実現するソフトウェア定義型車両(SDV)向けチップレットについて述べる(講演番号10.1)。機能安全水準の異なる故障が下位のECU(電子制御ユニット)で発生しても上位のECUに波及しない、FFI(Freedom From Interference)機能を備える。32コアのAPUクラスタと32コアのNPUクラスタで構成した。APUクラスタの動作周波数は2.7GHz、性能は1080kDMIPS、NPUクラスタの動作周波数は1.066GHz、性能は400TOPS。チップレット間接続(UCIe)のデータ転送速度は51.2GB/sと高い。全体の面積は312平方mm。

ソニーセミコンダクタソリューションズは、20Gサンプル/sと高速な時間インターリーブAD(アナログデジタル)変換器を報告する(講演番号11.6)。分解能は8bit。複数の1Gサンプル/sのサブAD変換器を時分割駆動することでサンプリング速度を高めた。入力バッファと参照バッファを含めた消費電力は135mW。SN比は37dB。製造技術は12nmのFinFETである。

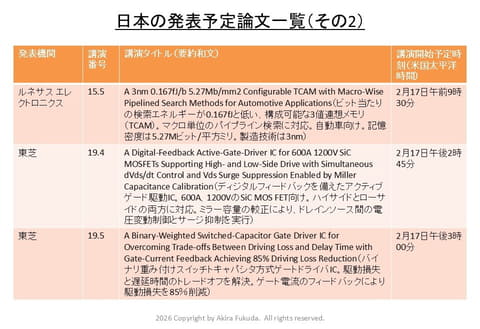

検索の消費エネルギーがきわめて低い連想メモリ

次はセッション15とセッション19の講演である。ルネサス エレクトロニクスは、ビット当たりの検索エネルギーが0.167fJと低い、構成可能な3値連想メモリ(TCAM)を開発した(講演番号15.5)。自動車向けである。マクロ単位のパイプライン検索に対応する。記憶密度は5.27Mbit/平方mm。製造技術は3nm。

セッション19では東芝が2件の研究開発成果を発表する。始めに、デジタルフィードバックを備えたアクティブゲート駆動ICを発表する(講演番号19.4)。600A、1,200VのパワーSiC MOS FET向け。ハイサイドとローサイドの両方に対応した。ミラー容量の較正により、ドレインソース間の電圧変動制御とサージ抑制を実行する。

次に、バイナリ重み付けスイッチトキャパシタ方式ゲートドライバICを報告する(講演番号19.5)。駆動損失と遅延時間のトレードオフを解決したとする。ゲート電流のフィードバックにより駆動損失を85%削減した。

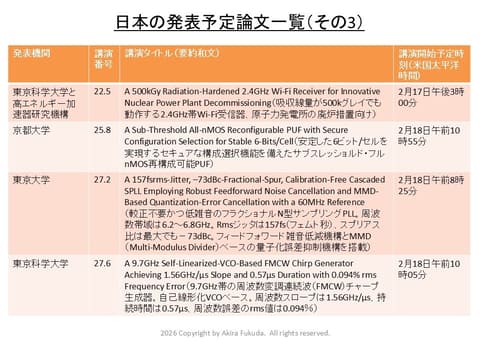

耐放射線型の2.4GHz無線LAN送受信器

続いてセッション22、セッション25、セッション27の講演である。東京科学大学と高エネルギー加速器研究機構は、吸収線量が500kグレイでも動作する耐放射線型2.4GHz帯Wi-Fi受信器を共同で開発した(講演番号22.5)。京都大学は、安定した6ビット/セルを実現するセキュアな構成選択機能を備えたサブスレッショルド・フルnMOS回路の再構成可能PUF(Physically Unclonable Function)回路を発表する(同25.8)。

東京大学は、較正不要かつ低雑音のフラクショナルN型サンプリングPLLを開発した(講演番号27.2)。周波数帯域は6.2~6.8GHz。Rmsジッタは157fs(フェムト秒)、スプリアス比は最大でも-73dBc。フィードフォワード雑音低減機構とMMD(Multi-Modulus Divider)ベースの量子化誤差抑制機構を搭載した。

東京科学大学は、9.7GHz帯の周波数変調連続波(FMCW)チャープ生成器を発表する(講演番号27.6)。自己線形化VCO(電圧制御発振器)ベース。周波数スロープは1.56GHz/μs、持続時間は0.57μs、周波数誤差のrms値は0.094%である。

スマート農業向けの超軽量センサータグ

最後にセッション29とセッション32の講演をご紹介する。大阪大学と神戸大学、九州大学ほかの共同研究チームは、重量が1グラム以下と軽い、植物のストレスを検出するセンサータグを報告する(講演番号29.5)。スマート農業向けである。

旭化成エレクトロニクスとオレゴン州立大学の共同研究グループは、PVT(プロセス、電圧、温度)変動に強いフルダイナミックΔΣ方式AD(アナログデジタル)変換器を開発した(講演番号32.2)。較正は不要。容量縮退積分器とボトムプレートレベルシフト(BPLS)により、95.6dBのダイナミックレンジと186dBの性能指数(FoM)を達成した(帯域幅は10kHz)。製造技術は65nmのCMOSである。

![ASUS ノートパソコン Chromebook Plus CX34(CX3402) CX3402CVA-MW1032 [パールホワイト] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/winkstore/cabinet/272500/272451.jpg?_ex=128x128)

![★エイスース / ASUS TUF Gaming T500MV T500MV-13420H412W [ソーラーエクリプスグレー]【デスクトップパソコン】【送料無料】 製品画像:6位](https://thumbnail.image.rakuten.co.jp/@0_mall/d-rise/cabinet/img054/p000000913791_1.jpg?_ex=128x128)

![わたしはこれでやせました [ MEGUMI ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4512/9784478124512_1_2.jpg?_ex=128x128)

![角川まんが学習シリーズ 日本の歴史 5大特典つき全16巻+別巻5冊セット [ 山本 博文 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3680/9784041153680_1_17.jpg?_ex=128x128)

![【楽天ブックス限定特典】KEITA MACHIDA 15th Anniversary Photobook 「sign」(限定トレカ) [ 町田啓太 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1991/2100014771991_1_3.jpg?_ex=128x128)

![リーガルプログレッシブ14 建築訴訟 改訂版 [ 小久保孝雄 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9060/9784417019060_1_2.jpg?_ex=128x128)

![[新品][ライトノベル]ようこそ実力至上主義の教室へ (全32冊) 全巻セット 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0029/set-youjitsu_01.jpg?_ex=128x128)

![世界は自分で創造する IQ148の天才舞踏家が語る現実創造の法則 [ 大瀧冬佳 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7989/9784815637989_1_9.jpg?_ex=128x128)

![CARPE DIEM 今この瞬間を生きて [ ヤマザキマリ ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1640/9784767831640_1_2.jpg?_ex=128x128)

![異常に非ず [ 桜木 紫乃 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7279/9784103277279_1_22.jpg?_ex=128x128)