福田昭のセミコン業界最前線

2010年代後半以降のDRAMトレンド、微細化と記憶密度に関する偽説のカラクリを暴く

2023年10月30日 09:42

DRAMの製造技術世代が10nm世代(20nm未満の世代)に突入してから、すでに5年が経過した。この5年間に、DRAMの技術と製品の状況はかなりの変化を見せている。そこでDRAMの製品と開発、技術の動向をまとめてアップデートする。とはいうものの、DRAMの位置付けはこの20年間に大きく変化してきた。このため本コラムの前回では、基本的な事柄の「おさらい」として西暦2000年以降のDRAM技術を2010年代前半まで振り返った。併せて参照されたい。

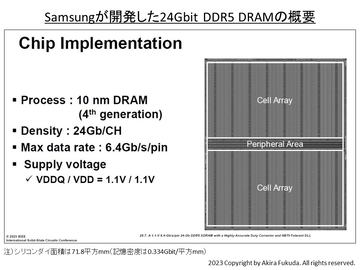

今回は2010年代後半から2020年代前半までのDRAM開発動向を扱う。技術ノードでは29nm世代(2Xnm世代)から12nm世代(1β世代)に相当する。国際学会ISSCCで発表されたDRAM試作チップの技術ノードに当てはめると、2014年に29nm~25nmノード、2016年に25nmノード、2017年に21nm~20nmノード、2018年に22nm~18nmノード、2019年に1Xnmノード~1Ynmノード、2020年に1Ynmノードと微細化が進んだ。

DRAMの開発トレンドとしては「加工寸法の微細化」、「記憶密度の向上」、「記憶容量の増加」、「データ転送速度(入出力速度)の向上」を取り上げる。また一部のメディアに散見される、トレンドに関する「偽説(あるいは誤解)」についても言及する。

DRAMが「微細化限界に来ている」という言説を検証する

半導体ロジックの研究開発では「微細化の限界」が取り沙汰されて久しい。前回でも触れたように、最先端ロジック用MOS FETの加工寸法は技術ノードの数値と一致しなくなっており、トランジスタの微細化は限界に達したとも言える。それではDRAMの微細化はどうだろうか。

冒頭のグラフは、国際学会ISSCCで発表されたDRAM試作シリコンダイの製造技術ノードを1998年から2023年まで(つまり25年間の推移を)まとめてみたものだ。縦軸を技術ノード、横軸を発表年としたグラフである。グラフからは、1998年から2010年までは微細化が急速に進んだものの、2010年以降は微細化があまり進んでいない。このことから、「2010年代以降、DRAMの微細化は限界に近づいている」という言説が成立する……ように見える。

ところが、この言説には重大な罠が仕掛けられている。それは縦軸である技術ノードが「線形目盛り」であることだ。

「比例縮小則(スケーリング則)」を無視した線形グラフの暴挙

半導体の研究開発で半ば常識となっている理論に「比例縮小則(「スケーリング則」、「デナード・スケーリング」、「デナード則」とも呼ばれる)」がある。1974年にIBMのロバート・デナード(Robert H. Dennard)らがIEEEの論文誌に発表した理論で、MOS FETの寸法をスケーリング係数「k」を基準として縮小すると、どのようなメリットがあるかを計算したものだ。

スケーリング則を結論から粗く言ってしまうと、MOSFETのゲート寸法(ゲート長とゲート幅)を「k分の1」にすると、遅延時間が「k分の1」に短くなり、消費電力は「kの2乗分の1」に下がる。小さくするだけで、理論的には高速化と低消費電力化を同時に達成するという夢のような理論である。しかも1970年代~1990年代のMOS FETと集積回路は、おおむねこのスケーリング則に従って開発が進行した。実際に使われた「k」は1.4前後、言い換えると「k分の1」は0.7前後である。

1970年代~1990年代に微細化を牽引したDRAMの寸法は、このスケーリング係数(1.4)に従って縮小された。もちろん少しのずれはあるものの、約3年で次世代品、すなわち加工寸法を0.7倍に縮小した大容量DRAMが開発された。3年で0.7倍というのは、6年で0.7の2乗である「0.49」、つまり寸法が半分になることを意味する。

ここでもう一度、ISSCCで発表されたDRAMの製造技術ノードを1998年から2023年まで(つまり25年間の推移を)まとめたグラフをお見せする。縦軸を技術ノード、横軸を発表年としたグラフである。ただし縦軸は「対数目盛り」に変更してある。

縦軸を対数目盛りに変更すると、見映えのまったく異なるグラフになってしまった。25年間、DRAMの技術ノードは「約7年で半分(年率0.906倍)」というほぼ一定のペースで微細化を継続してきた。1998年以前の「約6年で半分(年率0.891倍)」には及ばないものの、微細化は明らかに一定速度を維持している。限界の兆しは、(現実は別として)このグラフからは見えてこない。

比例縮小則は寸法の乗算で成立している。加算ではない。乗算(あるいは除算)によって変化する物理量のトレンドを正確に把握するグラフは、「対数グラフ」だ。そこに加算のグラフである「線形グラフ」を持ち込むこと自体が、一種の暴挙と言えよう。

「記憶密度の向上は2010年代後半以降に急速に進んだ」説を検証する

同様の暴挙あるいは偽説は、記憶密度の向上トレンドに関する言説にもみられる。以下は 国際学会ISSCCで発表されたDRAM試作シリコンダイの記憶密度を1999年から2023年までプロットしたグラフだ。縦軸(記憶密度)は線形目盛りにしてある。

1999年から2010年までは記憶密度(Gbit/平方mm)が横ばいあるいは微増で推移した。ところが2014年以降は急激に増加している。そこでDRAMシリコンダイの記憶密度は「2010年代半ば以降、急速に向上した」との言説が成立する……ように見える。

この言説も、記憶密度を線形目盛りでプロットしたことによる誤解が生じている。なぜなら、トランジスタの寸法が半分になるということは、トランジスタの面積が4分の1になることを意味するからだ。寸法の2乗で面積は縮小する。当然のことだ。従って原理的には、寸法が半分になると記憶密度は4倍に高まる。

記憶密度もまた、基本的には乗算で決まる。そこに線形グラフを持ち込むことは正しいとは言えない。対数グラフが適切と言える。対数グラフに変更すると、先程とはまったく違う景色が見えてくる。1999年から2023年まで、記憶密度は「11年で10倍(年率1.23倍)の一定速度で向上してきた」、という景色だ。2014年以降も、以前と同じペースで記憶密度が増加している。

年率1.23倍というペースは、6.7年で記憶密度が4倍になるということを意味する。微細化のトレンドである「7年で2分の1」(原理的には7年で記憶密度が4倍)と良く一致していることが分かる。

最大記憶容量が2010年代後半に再び拡大

次はシリコンダイ当たりの最大記憶容量である(ここからは偽説は取り上げない)。前回でも述べたように、2000年代にDRAMの記憶容量はあまり拡大しなくなった。ISSCCで1995年~2014年に発表された最大記憶容量は20年で8倍、年率1.11倍に鈍化した。ちなみに「3年で4倍」は年率1.59倍である。

それが2010年代後半に入ると、記憶容量は再び拡大傾向が強まった。2014年から2023年までの最大記憶容量は、8年で3倍、年率1.32倍に向上した。インターフェイス系列別に見ると、大容量化を牽引しているのはDDR系とLPDDR系であることが分かる。DDR系はデータセンター(サーバー)の主記憶に対する大容量化の要求が、LPDDR系はハイエンドスマートフォンの主記憶に対する大容量化の要求が、それぞれ強まっていることを反映したとみられる。

データ入出力速度でLPDDR系がDDR系を追い越す

続いてデータ入出力速度(データ転送速度)である。ピン当たりの速度(Gbps/ピン)をISSCCの発表から、2000年から2023年までプロットした。DRAMはインターフェイス系列によってデータ転送速度がかなり異なる。もっとも高速なのはGDDR系で、ほかのインターフェイス系に比べて3倍~4倍も高い。もっとも低速なのはHBM系である。HBM系はほかのインターフェイスとは設計思想が違う。回路のクロックを低くして消費電流を抑制し、入出力ピンの数を1,024ピンと多くしてデータ転送速度(帯域)を稼いでいる。

ピン当たりの速度をインターフェイス系列ごとに2000年~2012年と2000年~2023年で比較すると、いくつかの点で傾向の違いが見られる。2000年~2012年に速度向上ペースがもっとも高かったのはGDDR系で、年率換算で1.28倍のペースで高速化を続けた。次いでDDR系が年率1.18倍、それからLPDDR系が1.14倍となっている。なおHBM系は2012年時点では開発途上にあり、ISSCCでは発表されていない。

2000年~2023年では、速度向上ペースがもっとも高かったのはHBM系である。ISSCCで初めてHBMチップが発表されたのは2014年。この時点から2022年まで、年率換算で1.32倍とかなり高いペースで速度を向上させた。一方でGDDR系は2000年~2023年に年率換算で1.15倍と、高速化の勢いがかなり鈍った。DDR系も年率換算では勢いを少し下げている。LPDDR系は逆に高速化のペースを少し上昇させた。

DDR系とLPDDR系ではデータ転送速度の逆転が生じた。LPDDR系が実用化された2000年代後半は、DDR系に比べてデータ転送速度が低かった。LPDDR系は電源電圧を低くするとともにいくつかの工夫によって消費電流を抑えていたので、データ転送速度が低くなるのはごく普通のことだ。ところがその後、LPDDR系はDDR系よりも速いペースで高速化を進めた。その結果、2010年代半ばにはデータ転送速度が逆転し、2010年代後半以降はその差を広げていった。

インターフェイス系列によって開発の重点が高速化と大容量化に分かれる

ここからはまとめである。DRAMの開発動向を「2000年代~2010年代前半」と「2010年代後半~2020年代前半」で比較した。「2010年代後半~2020年代前半」のトレンドを以下に簡単に説明しよう。

高速化の要求増大は、超高速バージョンであるHBMモジュールを実用化させた。その反動なのかは不明だが、GDDR系の高速化ペースがやや鈍化した。

DDR系では大容量化が復活した。マシンラーニングの革新的な進化(大規模学習)によって主記憶の大容量化要求が一気に強まったことが、背景にある。データセンターやサーバーで扱うデータ量の増大も寄与していそうだ。

そしてもっとも注目すべきは、DRAMに限っては微細化のペースが現在でも一定で推移していることだろう。加工寸法の縮小(アクティブエリアのハーフピッチで換算)ペースは約7年で2分の1である。10nm世代以降もこのペースを維持できるのかに注目していきたい。

![【中古パソコン】Apple Mac mini MGNT3J/A A2348 M1 2020 小型デスク 選べるOS [Apple M1 8コア メモリ16GB SSD512GB 無線 BT シルバー]:良品 製品画像:5位](https://thumbnail.image.rakuten.co.jp/@0_mall/whatfun-pc/cabinet/35/mm-mgnt3ja-16br.jpg?_ex=128x128)

![液晶ディスプレイ アイ・オー・データ LCD-A241DB [液晶ディスプレイ 23.8型/ブラック/5Y/3辺フレームレス] 製品画像:20位](https://thumbnail.image.rakuten.co.jp/@0_mall/etre/cabinet/itemimage28/1264173.jpg?_ex=128x128)

![不滅なるものへの挑戦 [ 大川隆法 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4682/9784823304682_1_3.jpg?_ex=128x128)

![タッチペンで音が聞ける!はじめてずかん1000 英語つき [ 小学館 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6775/9784099416775_1_37.jpg?_ex=128x128)

![【サイン本】腐女医の医者道! [ さーたり ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1764/9784040681764.jpg?_ex=128x128)

![角川まんが学習シリーズ 日本の歴史 5大特典つき全16巻+別巻5冊セット [ 山本 博文 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/3680/9784041153680_1_17.jpg?_ex=128x128)

![呪術廻戦 11 死滅回游4呪胎戴天 (集英社リミックス) [ 芥見 下々 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2957/9784081152957.gif?_ex=128x128)

![2026年度版「みんなが欲しかった!」宅建士2冊セット [ 滝澤 ななみ ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1981/2100014701981.jpg?_ex=128x128)

![[新品]本好きの下剋上 コミックセット (全43冊) 全巻セット 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/mangazenkan/cabinet/syncip_0029/set-honzuki_01.jpg?_ex=128x128)

![ひよこクラブ 2026年夏号 [雑誌] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0665/4912177590665_1_3.jpg?_ex=128x128)