ニュース

Snapdragon X2 Eliteに搭載される「第3世代Oryon CPU」の詳細が明らかに

2025年11月19日 23:00

Qualcommは、米国本社があるカリフォルニア州サンディエゴ市において「Snapdragon Architecture Deep Dive 2025」を開催し、同社のPC向け最新SoC「Snapdragon X2 Elite」に関する詳細を説明した。Qualcommは9月に開催したSnapdragon SummitにおいてSnapdragon X2 Eliteを発表したが、技術的な詳細は明らかにしていなかった。それが本イベントで明らかになった形となる。

本レポートではそうしたSnapdragon Architecture Deep Dive 2025のセッションの中で、主にCPUの詳細などに関してレポートしていく。

Snapdragon X2の特徴は第3世代Oryon、第8世代Adreno、第6世代NPU

Snapdragon X2 Eliteは、2023年10月に発表され、2024年6月に出荷が開始されたSnapdragon Xシリーズ(X Elite、X Plus、Xの総称)の後継となる製品だ。

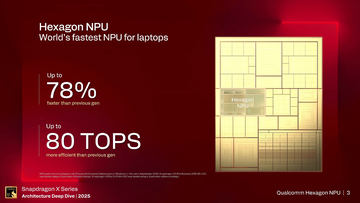

Snapdragon Xシリーズは、Qualcommが独自に設計したArmアーキテクチャのCPU(Oryon CPU)と、QualcommのAdreno GPU、さらには45TOPSとCopilot+ PCの要件である40TOPS以上の性能を実現したNPUを搭載し、発表時点でWindowsのモバイルノートPC向けとしては最高性能を実現したSoCとして話題を呼んだ。

その後継となるのがSnapdragon X2シリーズとなり、9月のSnapdragon Summitではその最上位グレードとなる「Snapdragon X2 Elite Extreme(X2E-96-100)」と「Snapdragon X2 Elite(X2E-88-100およびX2E-80-100)」という3つのSKUが存在することが明らかにされている(現時点ではX2 Plusや無印X2に関しては発表されていない)。

今回、そのSnapdragon X2シリーズのCPU、GPU、NPU、SoC全体などに関して詳細が明らかにされている。

| ブランド名 | SKU名称 | CPUコア数 | プライムコア | プライムコア周波数 | プライムコアブースト周波数 | パフォーマンスコア数 | パフォーマンスコア最大マルチコア時周波数 | キャッシュ容量合計 | GPU名称 | GPU最大周波数 | NPUピーク性能 | メモリ | チャンネル数 | 帯域幅 | MoP最大容量 | 最大容量 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Snapdragon X2 Elite Extreme | X2E-96-100 | 18 | 12 | 4.4GHz | 5GHz(シングル/デュアル) | 6 | 3.6GHz | 53MB | X2-90 | 1.85GHz | 80TOPS | LPDDR5x | 3 | 228GB/s | 48GB | 128GB+ |

| Snapdragon X2 Elite | X2E-88-100 | 18 | 12 | 4GHz | 4.7GHz(シングル/デュアル) | 6 | 3.4GHz | 53MB | X2-90 | 1.7GHz | 80TOPS | LPDDR5x | 2 | 152GB/s | - | 128GB |

| Snapdragon X2 Elite | X2E-80-100 | 12 | 6 | 4GHz | 4.7GHz(シングル)/4.4GHz(デュアル) | 6 | 3.4GHz | 34MB | X2-85 | 1.7GHz | 80TOPS | LPDDR5x | 2 | 152GB/s | - | 128GB |

QualcommのSnapdragon X2シリーズと従来製品となるSnapdragon Xシリーズの違いをハイレベルにまとめると、以下のようになる。

| Snapdragon X2 Elite | Snapdragon X Elite | |

|---|---|---|

| 発表年 | 2025年 | 2023年 |

| CPU名称 | Oryon(第3世代) | Oryon(第1世代) |

| ベースデザイン | 自社開発(18コア、12Prime+6PF) | 自社開発(12コア/すべてPrime) |

| クラスター構成 | Prime(6C)×2+PF(6C) | Prime(4C)×3 |

| L2キャッシュ | 16MB(Prime)×2+12MB(PF) | 12MB(Prime)×3 |

| LLC | 9MB | 6MB |

| トータルキャッシュサイズ(L2+L3) | 53MB | 42MB |

| GPU名称 | Adreno X2(第8世代) | Adreno X1(第7世代) |

| メモリ/バス幅 | 192bit(Extremeのみ)/128bit | 128bit |

| メモリ種類/データレート | LPDDR5x/9523 | LPDDR5x/8533 |

| 理論帯域幅 | 228GB/s(Extremeのみ)/152GB/s | 約136GB/s |

| NPU | 新Hexagon NPU(NPU6) | 新Hexagon NPU(NPU3) |

| ISP | 新Spectra | 新Spectra |

| モデム | X75(5G) | X65(5G) |

| PCI Expressコントローラ | Gen5(12x)Gen4(4x) | Gen 4(8x) |

| USB | USB4 | USB4 |

| 製造プロセスルール | 3nm(TSMC) | 4nm(TSMC) |

CPUはOryon(第1世代)からOryon(第3世代)に強化され、従来世代の12コア(Primeコアのみ)から18コア(Primeコアが12コア+パフォーマンスコア6コア)に強化されている。また、GPUは、同社GPUの第7世代(Adreno 7xx)から第8世代(Adreno 8xx)に強化されており、内部アーキテクチャが一新されている。NPUに関しては、従来製品では同社の内部世代でNPU3と呼ばれている第3世代から、NPU6という第6世代へと強化されている。

なお、GPUとNPUに関しては別記事で詳しく紹介しているので、そちらをご参照いただきたい。

第3世代Oryonは、6コアのパフォーマンスコアクラスタの追加が大きな強化点

Snapdragon X2シリーズに採用されているCPUは、独自開発したOryon CPUの第3世代となる。Oryonは、元々はQualcommが買収したArm CPUを設計する企業「NUVIA」のCEOだったジェラード・ウイリアムズ氏(現在はQualcomm エンジニアリング担当上級副社長)が率いる開発チームが開発した独自CPU。Qualcommが持つArmのアーキテクチャライセンスの権利を行使する形で、独自開発のCPUとして設計されている。AppleのAシリーズやMシリーズと同じような独自のマイクロアーキテクチャを持つ、Armプロセッサとなる。

QualcommはこのOryon CPUを、Snapdragon Xシリーズに採用したほか、2024年に発表したSnapdragon 8 Elite、2025年のSnapdragon Summitで発表したSnapdragon 8 Elite Gen 5などのスマートフォン向けのSoCや自動車向けのSoCなどにも採用している。

| 第1世代Oryon | 第2世代Oryon | 第3世代Oryon | |

|---|---|---|---|

| 採用製品 | Snapdragon X | Snapdragon 8 Elite(Gen 4) | Snapdragon X2/Snapdragon 8 Elite Gen 5 |

| ターゲット | PC | スマホ | PC/スマホ |

| 最大コア数 | 12コア | 8コア | 18コア(PC)/8コア(スマホ) |

| 命令セットアーキテクチャ | Armv8 | Armv8 | Armv8(PCはSVE2/SME対応) |

| プライムコア | 12コア | 2コア | 12コア(PC)/2コア(スマホ) |

| プライムコア最大周波数 | 4.3GHz(デュアルコア時) | 4.32GHz | 5GHz(PC/デュアルコア時)/4.6GHz(スマホ) |

| プライムコアのL2キャッシュ(クラスターあたり) | 12MB | 12MB | 16MB(PC)/12MB(スマホ) |

| パフォーマンスコア | - | 6コア | 6コア |

| パフォーマンスコア最大周波数 | - | 3.53GHz | 3.6GHz(PC)/3.62GHz(スマホ) |

| パフォーマンスコアのL2キャッシュ(クラスターあたり) | - | 12MB | 12MB |

| SLC(L3) | 6MB | - | 9MB(PC)/-(スマホ) |

| トータルキャッシュサイズ(L2+SLC) | 42MB | 24MB | 53MB(PC)/24MB(スマホ) |

簡単にいうと、第1世代では12コアのプライムコアだけで構成されており、第2世代では2コアのプライムコアに6コアのパフォーマンスコアというデザインが採用され、それがスマートフォン用(Snapdragon 8 Elite)とされ、第3世代ではPC用にも6コアのパフォーマンスコアが採用されたというのが流れになる。

なお、ここでいう第1世代、第2世代、第3世代というのはかなりマーケティング的な呼び方で、たとえばスマートフォン用の第3世代Oryonは、ほとんど第2世代と同じ世代と考えられる。その意味で、PC用とスマートフォン用を混在させて説明すると話がややこしくなるので、以下はPC用に絞って説明を続けて行く。

| 第1世代Oryon | 第3世代Oryon | |

|---|---|---|

| 採用製品 | Snapdragon X | Snapdragon X2/Snapdragon 8 Elite Gen 5 |

| 最大コア数 | 12コア | 18コア |

| 命令セットアーキテクチャ | Armv8 | Armv8(SVE2/SME対応) |

| プライムコア | 12コア | 12コア |

| プライムコア最大周波数 | 4.3GHz(デュアルコア時) | 5GHz(PC/デュアルコア時) |

| プライムコアのL2キャッシュ(クラスターあたり) | 12MB | 16MB |

| パフォーマンスコア | - | 6コア |

| パフォーマンスコア最大周波数 | - | 3.6GHz |

| パフォーマンスコアのL2キャッシュ(クラスターあたり) | - | 12MB |

| SLC(L3) | 6MB | 9MB |

| トータルキャッシュサイズ(L2+SLC) | 42MB | 53MB |

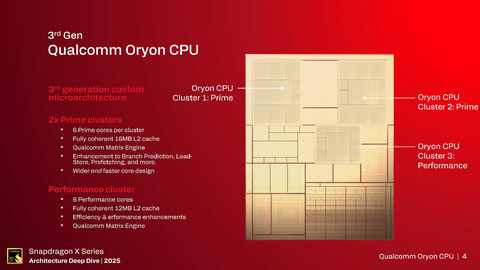

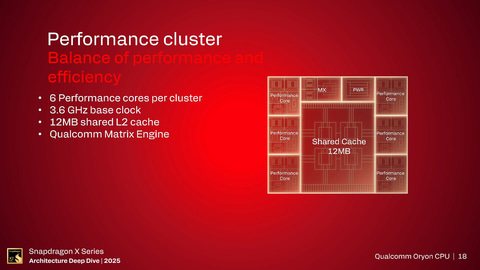

PC用の第3世代と第1世代を比較すると、2つの大きな違いがある。1つは6コアのパフォーマンスコアが追加されたことで、もう1つは12コアのプライムコアのクラスタが、第1世代では4コアで1つのクラスタを構成していたが、第3世代では6コアで1つのクラスタという形になっていることだ。

これにより、第1世代では4コアのクラスタが3つで12コア、第3世代では6コアのプライムコアクラスタが2つと6コアのパフォーマンスコアのクラスタが1つで合計18コアというのが最大構成になる。

これに伴いクラスタに内蔵されているL2キャッシュの容量も変更されている。第1世代では1つのプライムコアクラスタあたり12MBのL2キャッシュが内蔵されており、3つのクラスタ合計で36MBのL2キャッシュとなっている。

それに対して、第3世代ではプライムコアクラスタあたり16MBのL2キャッシュとなっており、プライムコアのL2キャッシュ容量という意味では32MBとむしろ減っている。

かつ、プライムコアのL2キャッシュの、L1にヒットしなかった時の平均レイテンシは、第1世代よりも増大している。Qualcommによれば、L1キャッシュにヒットしなかった場合、L2キャッシュにあるデータを読み込んでくる場合の平均レイテンシは第1世代の17サイクルから、21サイクルに増えている。

Oryon CPUは演算器より低速なL3キャッシュを持たず、CPUと同じ程度高速なL2キャッシュの容量を増やすことで性能を向上させるという設計思想で作られており、L2キャッシュの容量が増えていることが大きな意味があるので、L2の平均レイテンシが増大していることは好ましいことではないと考えられる。

Qualcommによれば、このことはクラスタあたりのキャッシュ容量が増えたこと、クラスタに内蔵されているCPUコアが増えたことによる影響とのことだが、クロック周波数などが上がっていることで、トータルでみると大きな影響はないとの説明だった。

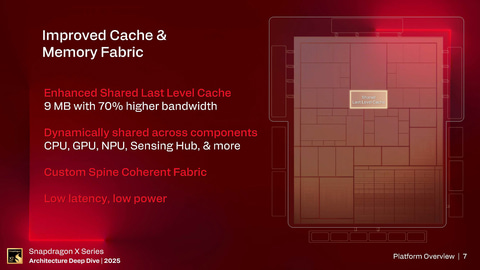

なお、追加されたパフォーマンスコアクラスタあたり12MBのL2キャッシュが搭載されており、さらにLLC(Last Level Cache、CPUだけでなくGPU/NPUなどからも利用できる)も6MBから9MBに増やされ、さらに帯域幅も70%改善されている。そうしたキャッシュ階層の最適化により、SoC全体で従来製品よりも高い性能を発揮できるとQualcommは説明した。

第3世代Oryonのマイクロアーキテクチャは、基本的には第1世代を踏襲

それでは、CPUコア内部の構造(マイクロアーキテクチャ)に関してはどうなのかといえば、Qualcommの説明を聞く限りは、基本的に大きな違いはなく、マイクロアーキテクチャに関してはほぼ同じだと考えることができる。

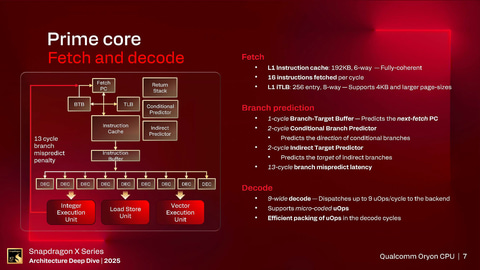

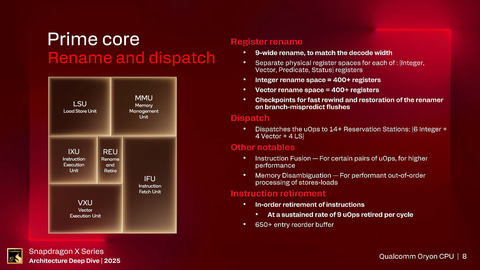

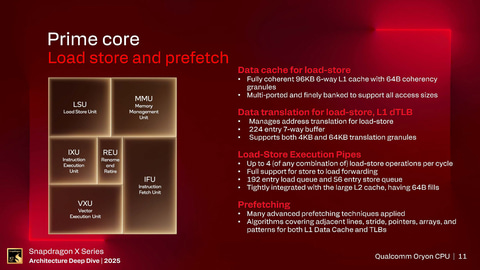

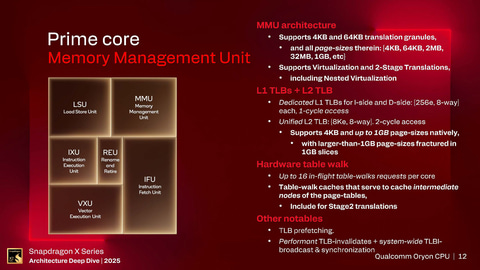

29KBのL1命令キャッシュ、256エントリー/8ウェイのL1 命令TLB、1サイクルあたり16命令読み込みが可能なフェッチユニット、13サイクルの分岐予測ミスレイテンシの分岐予測ユニット、9ワイドのデコーダなど、第1世代Oryonとスペック的にはまったく同じだ。

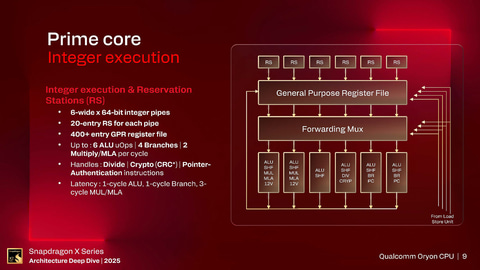

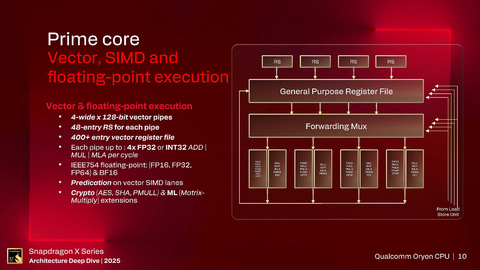

実行ユニットも同様に、6ワイドの64bit整数パイプで、最大6つのALU μOpsの整数演算ユニット、4ワイドで128bitの浮動小数点パイプで、最大4つのFP32ないしはINT32の演算が可能になる浮動小数点ユニットなど、実行ユニットも同様。ロードストアも96KBのL1データキャッシュ、224エントリー/7ウェイバッファのL1データTLBなど、こちらも第1世代と同じスペックだ。つまり、第1世代と第3世代Oryonはマイクロアーキテクチャはほぼ同一で、基本的には最適化が行なわれたものだと考えてよいだろう。

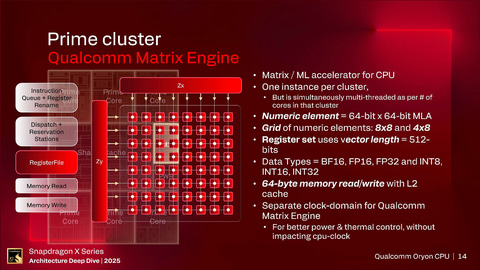

ただ、今回の世代では新しくQualcomm Matrix Engine(Matrix Engine)という行列演算アクセラレータが追加されている。これは、CPUを利用して行列演算を行なう際に一種のアクセラレータとして利用できるエンジンになる。プライムコアクラスタに1つのMatrix Engineが内蔵されており、クラスタに内蔵されている6つのCPUコアがSMT(仮想マルチスレッディング)的に、つまりエンジンは1つだけど、6つのCPUコアからみると複数あるかのように利用でき、Matrix Engineを利用して行列演算を高速に行なうことができる。

QualcommのMatrix Engineは、64bit×64bitの積和演算命令を実行することが可能で、8×8ないしは4×8のグリッドを利用して演算することができる。レジスタセットは512bitの浮動小数点長に対応しており、BF16/FP16/FP32、INT8/INT16/INT32のデータ精度に対応している。また、このMXはCPUとは異なるクロック周波数で動作しており、必要のない時にはクロック周波数を落とすなどして、省電力を実現している。

なお、命令セットとしてArmv8と、SVE2/SMEの拡張命令セットに対応していることを明らかにしている。特にSMEのような行列演算が多用される命令セットが利用される場合には、Matrix Engineを利用する意味があると考えられ、その場合にCPUに内蔵されている浮動小数点演算ユニットだけで処理する場合に比べて高い性能を発揮できる可能性がある。

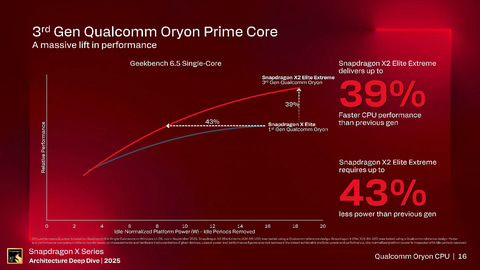

こうした設計により第3世代Oryonのプライムコアは、ピーク性能は39%向上しており、同じ性能であれば、消費電力は43%少なくなっているとQualcommは説明している。

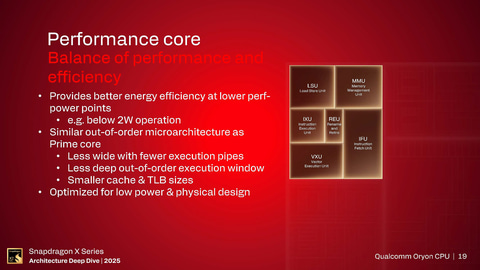

パフォーマンスコアの詳細も明らかにされる、パフォーマンスコアは2W以下の動作に最適化

今回Qualcommは、初めてOryonのパフォーマンスコアに関しても詳細を説明した。Oryonのパフォーマンスコアは、基本的なマイクロアーキテクチャはプライムコアと共通化されているが、実行パイプが減らされていること、同じようにアウトオブオーダー(OoO)の実行ウィンドウが減らされていること、キャッシュやTLBのサイズが減らされていることなどが違いになっているという。

それにより、ダイサイズがプライムコアよりも小さくなっており、パフォーマンスコアだけで動作しているときには2W以下と、アクティブ時のCPUとしては極めて低消費電力な動作を実現することができる。また、パフォーマンスコアクラスタにも同じようにMatrix Engineが1つ搭載されている。

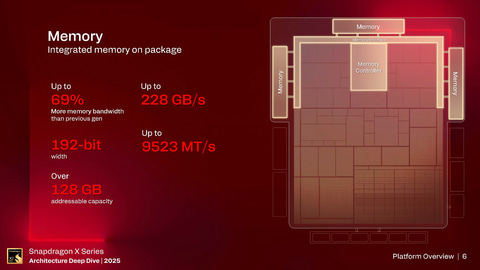

メモリコントローラは、SoCのアーキテクチャレベルでは64bitコントローラを3つ搭載しており、最上位SKUとなるSnapdragon X2 Elite Extreme(X2E-96-100)では、3チャンネルすべてが利用でき、192bit幅でメモリはLPDDR5x-9523を利用することが可能だ。

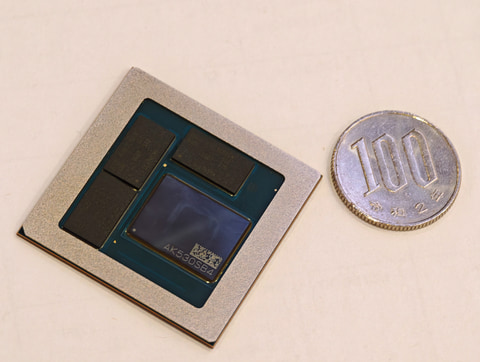

また、X2E-96-100には、MoP(Memory on Package)版が用意されており、その場合メモリ容量は48GB(16GBのDRAMチップ×3)で、192bit幅で228GB/sのメモリ帯域幅が実現される。なお、X2E-96-100はスペック上128GBを超えるメモリもサポートするとされており、その場合にはMoPではなく、マザーボード上に別途DRAMを搭載する形になると考えられる。別のパッケージが用意されるのか、それともMoPのパッケージがそのまま外部DRAMも利用できるのかは明白ではないが、MoPと外部DRAMは排他利用となる。

下位SKUとなるSnapdragon X2 Elite(X2E-88-100、X2E-80-100)に関しては3つのメモリコントローラのうち2つが有効になっており、128bit幅でLPDDR5x-9523が利用可能で、メモリ帯域幅は152GB/sとなる。こちらの最大メモリ容量は128GBで、多くの製品では16GBないしは32GBという構成になると考えることができる。

![[VETESA正規販売店]一体型デスクトップパソコン PC 24インチ Windows11 Office付き 第4世代 Core i7 メモリ16GB SSD512GB タッチパネル FHD 高視野角液晶 Webカメラ スピーカー内蔵 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/clovertradingshop/cabinet/item/a24tc-i74_1.jpg?_ex=128x128)

![【エントリーで最大全額ポイント還元|5/6まで】 JAPANNEXT|ジャパンネクスト ゲーミングモニター JN-T215FLG144FHD [21.5型 /フルHD(1920×1080) /ワイド /144Hz] 製品画像:11位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/7062/00000010163824_a01.jpg?_ex=128x128)

![隔週刊 1/18エクストラスケール 国産名車コレクション 2026年 5/13号 [雑誌] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0560/4912305320560_1_2.jpg?_ex=128x128)

![ボンボンドロップシール パーフェクトBOOK 公式ファンブック (アサヒオリジナル) [ 朝日新聞出版 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7671/9784022727671_1_4.jpg?_ex=128x128)

![sweet (スウィート) 2026年 6月号 [雑誌] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0665/4912154410665.gif?_ex=128x128)

![霊学 [ 江原啓之 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8384/9784336078384_1_4.jpg?_ex=128x128)

![くわしく学ぶ世界遺産300<第6版> 世界遺産検定2級公式テキスト [ 世界遺産検定事務局 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8999/9784839988999_1_3.jpg?_ex=128x128)

![【全巻】 無職転生~異世界行ったら本気だす~ 1-24巻セット (MFコミックス フラッパーシリーズ) [ フジカワ ユカ ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6938/2100014806938.jpg?_ex=128x128)

![【特典】しなこのほん(限定シール1枚) [ しなこ ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4219/2100014954219_1_3.jpg?_ex=128x128)

![クエスチョン・バンク 社会福祉士国家試験問題解説 2027 [ 医療情報科学研究所 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9773/9784896329773_1_4.jpg?_ex=128x128)