ニュース

Intelをも唸らせるTSMCが今後投入する新しい半導体技術

2024年7月1日 09:47

TSMCは、6月28日に神奈川県横浜市の横浜ベイホテル東急において「Japan Technology Symposium」という顧客向けのイベントを開催した。これは顧客だけに限定的に行なわれているイベントになるため、報道関係者などには公開されていないが、同日に記者説明会を開催し、イベントの概要を説明した。

TSMCが日本で躍進

今でこそ、半導体の設計や販売はAMD、Apple、NVIDIA、Qualcommが行ない、製造はTSMCやSamsungといったファウンドリが担当するという水平分業が当たり前になっているが、TSMCが創業した1987年当時は、半導体メーカーが自前で工場を持ち、設計、製造、販売まですべて一社で行なう垂直統合があたり前だった。そこから40年近くが経過し、今ではIntelなどの一部の例外を除き状況が一変、TSMCはグローバルに50%超のシェアを持っており、今や半導体産業のけん引車と言って良い状況だ。

TSMCジャパン株式会社 代表取締役社長 小野寺誠氏は、そうしたTSMCの日本での概況に関して説明。「日本のTSMCは1997年に1億5,000万ドル、2010年に6億ドル、そして2023年には41億ドルと成長を続けてきた。1年前のこの場では38億ドルと説明させていただいたので、引き続きプラス成長となっている。特に2023年にはTSMCグローバルでは7~8%のマイナス成長になっているのに、日本はプラス成長をしている」と述べた。

2023年の実績について小野寺氏は「12インチ換算のウェハ数では148万9,000枚とほぼ150万枚を実現し、1997年からの累計では1,000万枚を超えている。日本のビジネスは順調に推移している」と説明した。

また、日本の事業所に関しては、本社のある横浜のほか、茨城県つくば市に3DIC研究センター、大阪と横浜に最先端のプロセスノードを使った製品開発の支援、サポートを行なうジャパン・デザインセンターが用意されているほか、今年(2024年)の2月に開所式が行なわれたJASM(Japan Advanced Semiconductor Manufacturing)は、熊本県にTSMCとしては日本で初めてファブとして開設されたもので、「2024年中の量産開始を目指して順調に準備が進んでいる」という。

このファブは28nm~12nmなどの既に成熟しているプロセスノード(製造技術)を利用して製造される半導体の工場で、日本での需要の中心となるCMOS用のロジック半導体や自動車向けのマイクロコントローラなどをターゲットにしているものだ。

小野寺氏によれば「既に第2フェーズという7nmなどのより進んだプロセスノードをターゲットしたプロジェクトも動き始めている」との通りで、JASMをベースにTSMCの日本でのビジネスは今後も拡大することが期待されている状況だ。

NanoFlexに対応したN2を来年投入、裏面電源供給のA16は2026年末までに量産開始

TSMC シニア・バイス・プレジデント 兼 副共同最高業務執行責任者 ケビン・ジャン氏は、同社がJapan Technology Symposiumが説明した内容の概要を説明した。

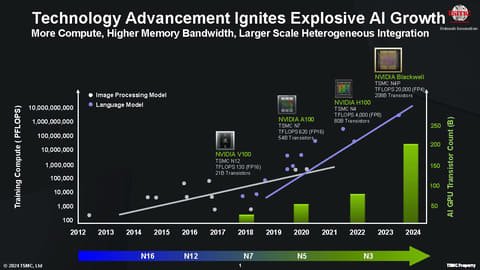

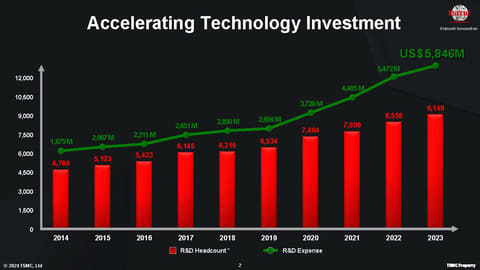

「現在AIによって演算性能に対するニーズは文字通り爆発的に増えている。たとえば弊社の顧客であるNVIDIAを例にとってみると、V100ではFP16で130TFLOPSだった性能は、H100ではFP8で4,000TFLOPSになり、さらに今年発表されたBlackwellではFP4で2万TFLOPSになっている。そしてトランジスタ数もV100では210億トランジスタだったのが、2,080億トランジスタへと10倍近くになっている」と述べ、新しいアプリケーションの登場が、演算能力への要求を引き上げる一方で、それを実現する半導体のプロセスノードと後工程(チップレットなど)の進化が重要になっていると説明した。このためTSMCの半導体研究者は年々増えており、2023年で9,149名、研究開発に利用したコストは58億4,600万ドルへと増大傾向にあるという。

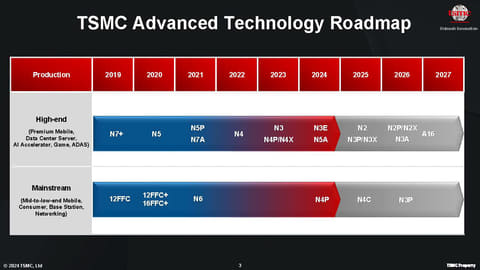

プロセスノードへの進化という意味では、3nm(N3ノード)をはじめとした各プロセスノードの開発が順調に推移しているという。N3は昨年(2023年)中に既に量産が開始されており、現在はバリエーションになるN3E、N3P、N3Xなどの開発が進められており、今年にN3Eの量産が開始される計画になっている。

N3はAppleのA17 Proなどの製造に利用されているほか、Intelが第3四半期中に投入を計画しているLunar Lakeのコンピュートタイルの製造に利用されていることも既に明らかにされており、今後さまざまな製品に採用される可能性が高いプロセスノードになっている。

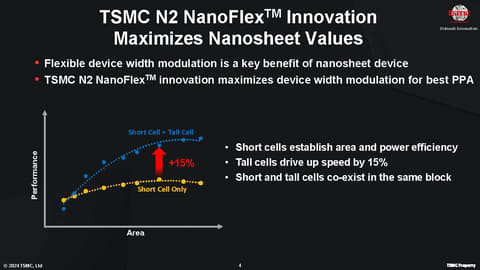

そして2025年には2nm(N2)の投入が行なわれ、N2ではNanoFlexと呼ばれる、GAA(Gate All Around)という4D形状のFETの構成を調整する技術が投入される。それによりPPA(面積および電力あたりの性能の略)と呼ばれる、ダイサイズや性能、電力などを最適化することを可能にする。

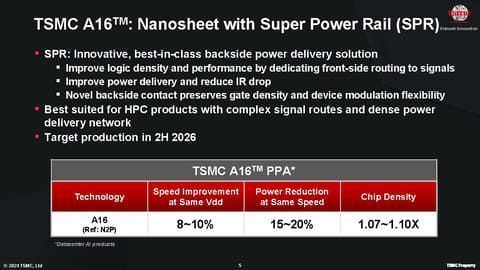

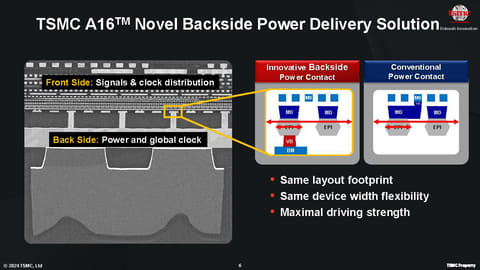

さらに2026年末までに量産開始が予定されているのがA16と呼ばれる単位がナノからオングストロームへとさらに小さくなったプロセスノードの導入が行なわれる。A16世代では、Super Power Rail(SPR)と呼ばれるシリコンの背面に電源層を設けることで、シリコン全体の電気特性を改善する「裏面電源供給技術」を導入する。ダイの前面では信号品質やクロック周波数の供給品質などが改善され、背面の電源層では電力供給の品質などの改善を期待できる。

このA16では、N2のバリエーションになるN2Pと比較して、同じ供給電力で8~10%の性能向上が実現され、同じ性能であれば15~20%の電力の削減が実現され、ダイの密度では1.07~1.1倍になるなどと説明している。

CoWoS、SoICなどの2D、3Dのチップレット技術を発展させて、AI向け半導体の進化を支える

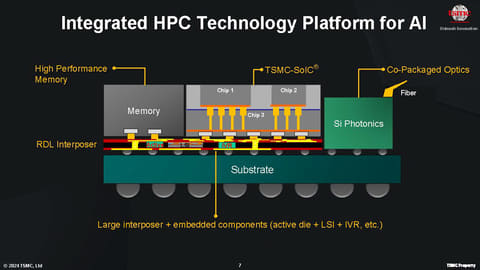

TSMCのジャン氏は「そうしたプロセスノードの進化と同時に、後工程のチップレット技術が今後のAIチップの進化では重要になる」と述べ、TSMCが提供する2Dや3Dのチップレット技術に関しても説明した。

実際、現在NVIDIAが提供しているH100/H200では、CoWoSと呼ばれるTSMCの2Dのチップレット技術を利用して、HBMメモリのパッケージ上での実装が行なわれている。また、AMDのInstinct MI300A/MI300Xでは、TSMCの3Dチップレット技術である「SoIC」などが利用されてメモリやGPUのチップがパッケージ上に混載されている。

NVIDIAが3月に発表したBlackwell(B200/B100)でも、2つのGPUチップと、HBMメモリが1つのパッケージ上に混載されている。このように、現状AI向けのGPUは例外なく2Dないしは3Dのチップレットが利用されており、チップレットがAI技術の未来を左右していることは明白だ。

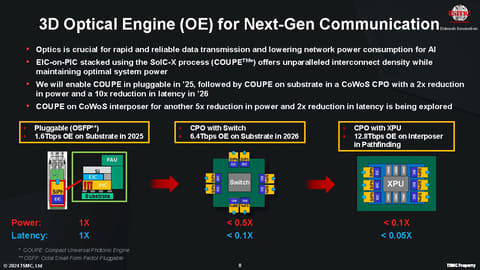

こうしたチップレットの中で、特に「3D OE」と呼ばれる光通信のエンジンをサブ基板やインターポーザなどに統合する技術に関して説明した。2025年にはまずCOUPE(Compact Universal Photonic Engine)と呼ばれる、SoIC-X(SoICのバリエーション)を利用したPICの上にEICを積層する技術を導入する。

翌2026年にはそれをCoWoS CPOという技術でサブ基板に統合することを実現し、6.4Tbpsの伝送速度を実現しながら、消費電力を半分、レイテンシを10分の1にする。さらにその先にはCPU、GPUなどが混載されているインターポーザにCPOを統合する技術で12.8Tbpsの伝送速度を実現し、さらに消費電力を10分の1、レイテンシを5%まで削減する。

現代のスーパーコンピュータは、GPUをNVLinkやInfinityFabricなどによりスケールアップし、EthernetやInfiniBandなどを利用してスケールアウトすることで、複数のGPUを1つのGPUとして使えるようになっている。3D OEのような技術により、スケールアップ時の帯域幅やレイテンシ削減などが可能になり、1つの巨大GPU全体の性能が引き上げられることになるので、プロセスノードの進化と同じぐらい重要な技術だという。

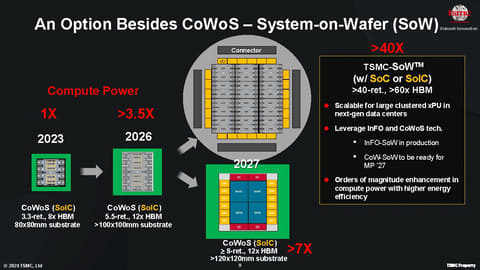

また、SoW(System-on-Wafer)に関しても説明した。現在AMDがTSMCの3Dチップレット技術で、キャッシュメモリとなるSRAMをダイの上に3D方向に積載している。SoWはその進化版のような技術で、ウェハとして製造する段階で既に複数のレイヤーを製造しておき、演算を行なう論理回路と、HBMメモリなどのメモリを製造時に積層し、メモリの容量を大きく増やすことが可能になる。

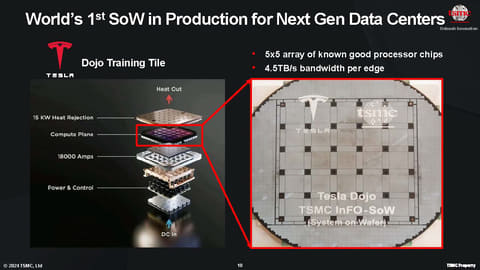

既に、自動車メーカーTESLAが試作した「Dojo」というAI学習用のチップでは、ウェハ上に5x5(つまり25個)のチップを構築することが可能になっているという。

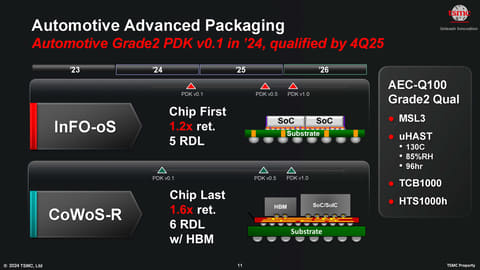

また、自動車グレードに対応したチップレット技術として「InFO-oS」と「CoWoS-R」を説明し、3nmなどの最先端のプロセスノードを利用して強力なチップを構築する環境が整っていると説明。日本に集中している自動車メーカーやティアワンの部品メーカーなどに採用を呼びかけた。

![Lenovo(レノボジャパン) ノートパソコン Chromebook Duet Gen9 ルナグレー 83HH000UJP [10.95型 /Chrome OS /MediaTek /メモリ:4GB /eMMC:128GB /日本語版キーボード /2024年10月モデル] 83HH000UJP 製品画像:11位](https://thumbnail.image.rakuten.co.jp/@0_mall/dtc/cabinet/mc4936/2468072.jpg?_ex=128x128)

![I-O DATA|アイ・オー・データ PCモニター ブラック KH-A241DB [23.8型 /フルHD(1920×1080) /ワイド /75Hz] 製品画像:9位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/9568/00000012607811_a01.jpg?_ex=128x128)

![IOデータ ゲーミングモニター KH-GD251UH 240Hz&フルHD対応 GigaCrysta [24.5型 / フルHD(1920×1080) / ワイド / 240Hz] ブラック 製品画像:7位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001504/4957180184845_1.jpg?_ex=128x128)

![IOデータ USBType-C搭載&フリースタイルスタンド採用液晶ディスプレイ [23.8型 / フルHD(1920×1080) / ワイド / 100Hz] ブラック KH-C242SDB-F 製品画像:5位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001651/4957180184692_1.jpg?_ex=128x128)

![I-O DATA|アイ・オー・データ USB-C接続 PCモニター フリースタイルスタンド(5年保証) ブラック LCD-C222SDB-FX [21.5型 /フルHD(1920×1080) /ワイド /100Hz] 製品画像:4位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/13735/00000014311243_a01.jpg?_ex=128x128)

![店舗やサロンのためのMeta広告集客・販促の教科書 ゼロからはじめて成果を出す! Meta広告入門・活用ガイド [ おだ ゆきえ ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2191/9784911572191.gif?_ex=128x128)

![解剖学を偏愛するトレーナーがたどり着いた! こちら、40代が当たり前にくびれる方法です。 [ Sachiyo ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0181/9784043300181_1_10.jpg?_ex=128x128)

![Betsucomi (ベツコミ) 2026年 6月号 [雑誌] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0669/4912047930669_1_2.jpg?_ex=128x128)

![ゲーム知識で最強に成ったモブ兵士は、真の実力を隠したい(コミック) : 3 【電子書籍】[ 二時八 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/3377/2000020563377.jpg?_ex=128x128)

![薬屋のひとりごと(17) (ビッグガンガンコミックス) [ 日向夏 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6558/9784301006558.gif?_ex=128x128)

![キングダム 79 (ヤングジャンプコミックス) [ 原 泰久 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1967/9784088941967_1_15.jpg?_ex=128x128)