笠原一輝のユビキタス情報局

AWSが発表したArm CPU「Graviton5」とAI ASIC「Trainium3」の詳細

2025年12月5日 02:00

Amazonの関連会社で、クラウドサービス事業者(CSP)のAWS(Amazon Web Services)は、12月1日~12月5日に同社の年次イベント「re:Invent 2025」を、米国ネバダ州ラスベガス市の会場で開催している。

AWSは近年、自社設計の半導体を開発製造して、自社のクラウドサービス事業に活用している。Arm CPUのGravitonシリーズ、AI向けのASIC(Application Specific Integrated Circuit、特定用途向け回路)となるTrainiumシリーズがそれだが、イベントの中で最新モデル「Graviton5」の発表、および「Trainium3」の一般提供開始発表を行なった。

本記事では、re:Invent 2025で発表された半導体関連の話題で、現地取材で分かったことなどを追加しながら解説していきたい。

2年ぶりに更新されたGraviton5、ArmのNeoverse V3ベースのArm CPU

AWS 副社長 兼 最上級エンジニア アリ・サイディ氏は、基調講演の中で自社製ArmアーキテクチャCPUの最新製品となる「Graviton5」に関して説明を行なった。

サイディ氏は「AWSでは2年に1度新しいCPUを導入してきた。2019年にGraviton2の投入を明らかにし、2021年にはGraviton3を、そして2年前の2023年のre:Invent 2023ではGraviton4を発表した。今回はその後継となるGraviton5を発表する。

Graviton5はCPUコア数が、Graviton4の96コアから2倍の192コアへと強化し、CPUコアそのものも20%性能が向上する。それにより、マシンラーニングで32%、データベースでは30~40%、Javaのアプリケーションでも30~40%程度性能が向上する」と述べ、大きな性能強化になると明らかにした。

| Graviton | Graviton2 | Graviton3/3E | Graviton4 | Graviton5 | |

|---|---|---|---|---|---|

| 発表 | 2018 | 2019 | 2021 | 2023 | 2025 |

| ISA | ARMv8-A | ARMv8.2-A | ARMv8.4-A | Armv9.0-A | Armv9.2-A |

| 拡張ISA | Neon | Neon | Neon/SVE | Neon/SVE | Neon/SVE |

| マイクロアーキテクチャデザイン | Cortex A72 | Neoverse N1 | Neoverse V1 | Neoverse V2 | Neoverse V3 |

| コア数 | 16コア | 64コア | 64コア | 96コア | 192コア |

| L1キャッシュ(命令/データ)/CPUコア | 48KB/32KB | 64KB/64KB | 64KB/64KB | 64KB/64KB | 64KB/64KB |

| L2キャッシュ/CPUコア | 512KB | 1MB | 1MB | 2MB | 1MB~3MB |

| L3キャッシュ/SoC | ? | 32MB | 32MB | 36MB | 192MB |

| インターコネクト | ? | CMN-600 | CMN-650 | CMN-700 | DSU-120? |

| メモリコントローラ | ? | 8xDDR4 | 8xDDR4 | 12xDDR5(DDR5-5600) | ?(DDR5-8800) |

| プロセスノード | 16nm | 7nm | 7nm | 5nm | 3nm |

Gravitonシリーズは、いずれもCPUコアはArmのIPデザインに基づいている。初代Gravitonこそモバイル用に開発されたCortex-A72だったが、Graviton2はデータセンター用のCPUとして開発されたNeoverse N1、Graviton3はNeoverseでもより高性能なNeoverse V1に、Graviton4ではNeoverse V2へと正常進化してきた。

今回のGraviton5は、その正常進化版となるNeoverse V3になる。今回AWSはArmのISAの世代に関して何も言及していないが、Neoverse V3はArmv9.2-Aなので、Graviton5は同様にArmv9.2-A対応だと考えられる。

拡張命令セットに関しては、「Neon/SVEに対応している。SMEには現状では対応していない」と述べ、Graviton4と同じくSMEには非対応となる。SMEに対応した場合、SMEに必要な演算器などの追加によるダイ面積のペナルティと、SME自体の普及率を天秤にかけた結果、今のところは必要ないと判断して見送ったということだ。

AWSとしてもSMEの効果に関しては大きいと考えているそうだが、現状ではSMEの普及率が低いため、こういう判断になったということだ。

3nmで製造されるGraviton 5、CPUコア数は192コアと倍増、L3キャッシュも192MBへ

製造に利用されるプロセスノードは、Graviton4の5nmから3nmへと微細化されている(AWSではハッキリとは言及していないが、いずれもTSMCだと考えられる)。

CPUコア数を倍の192コアに増やせたことは、こうしたプロセスノードの微細化が理由の1つだと考えられるが、同じコスト(有り体にいえばダイサイズ、基本的にはダイサイズが大きくなればなるほど製造コストは増えてしまう)で、これだけコア数を増やすのは不可能だと考えられる。

そこで考えられる可能性は、ダイを2つに分割して製造し、パッケージ上で1つに統合する「チップレット」方式の採用。サイディ氏に確認したところ「今回はそのあたりはまだお話しすることができない」という答えが返ってきた(今回、Graviton5の写真などが公開される予定は、取材時点ではないということだった)。

なお、Graviton3以降のGravitonシリーズでは、メモリコントローラは別ダイとして製造され、チップレットの形で1パッケージ上に統合される形になっている。Graviton5でも、少なくともメモリコントローラはチップレットの形で搭載されていることは明らかにされたので、少なくともチップレットの技術は利用されている。それがCPUダイにも利用されているか、それが今後より詳細な情報が明らかにされる時の注目点となる。

また、今回L3キャッシュがGraviton4の36MBから192MBと約5.3倍になっていることを明らかにしている。つまり1コアあたり376KBだったのが、1コアあたり1MBに強化されていることを意味している。キャッシュメモリの容量は、メモリレイテンシの削減につながるため、低レイテンシを必要とするアプリケーションなどで有利なのはいうまでもない。

なお、L1キャッシュとL2キャッシュの仕様は明らかにしていないが、ArmのNeoverse V3ではL1キャッシュが64KB/64KB、L2キャッシュは1MB~3MBとなっているので、L1キャッシュに関してはこの容量で、L2キャッシュに関してはGraviton4と同じ2MBあたりの可能性が高い。

加えてDRAMコントローラの数に関しては明らかにされていないが、Graviton4の時に8チャネルから12チャネルに増やされているので、12チャネルの可能性が高いのではないかと予想している。

ただ、サイディ氏によれば、AWSが本日よりプレビュー提供を開始するEC2インスタンス「M9g」ではDDR5-8800がメモリとして採用される計画だという。従来のGraviton4を搭載したEC2インスタンス「M8g」ではDDR5-5600を採用していたので、メモリチャネル数が同じだと仮定すれば、メモリ帯域幅が約57%向上することになる。M9gは、M8gと比較して25%の性能向上を実現すると説明しており、その25%の中にはメモリ帯域幅が向上していることも含まれることになる。

M9gは本日よりプレビュー提供が開始されている。ほかにCPUの性能に特化した「C9g」、メモリ重視のワークロードに特化した「R9g」などが計画されており、それらは2026年に導入される計画だ。

AWS、Trainiumの第3世代となるTrainium3の一般提供を開始

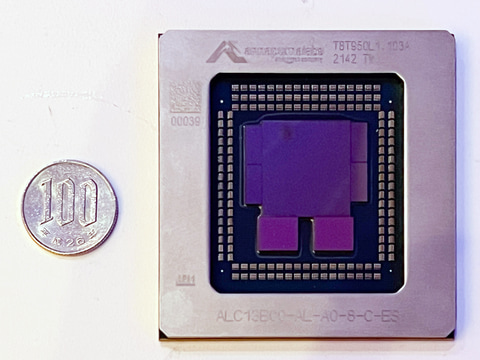

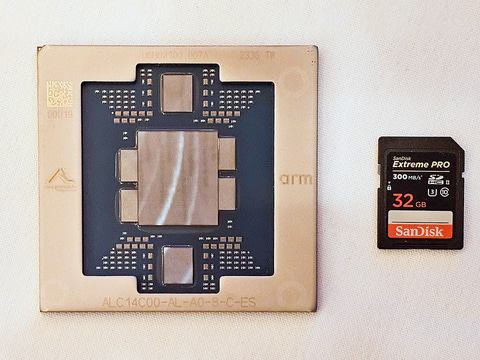

12月2日(現地時間)に開催したAWS CEO マット・ガーマン氏の基調講演の中で、AI学習/推論向けのASICとなるTrainiumシリーズの最新版、「Trainium3」の一般提供開始を明らかにした。

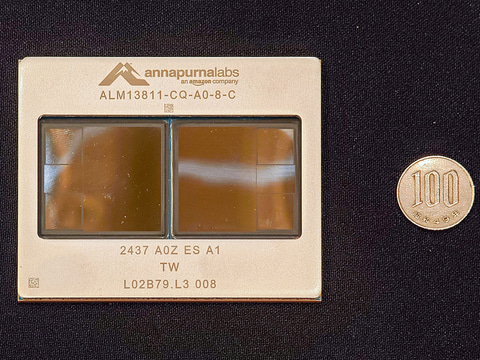

Trainium3は、傘下のAnnapurna Labsが開発したAIに特化した演算装置で、浮動小数点、整数演算などの内部演算装置を持ち、それを利用して行列演算などを効率よく行なえるようにしたもの。以前は推論用のInferentia、学習用のTrainiumと製品を分けて展開していたが、Inferentiaの第2世代(Inferentia2)と初代Trainiumはブランドこそ違うものの、チップそのものは同じになっており、事実上推論用と学習用は1つの製品に統合されている。

Inferentiaの第3世代、第4世代は登場していないため、事実上Inferentiaは今後登場しない可能性が高い。こうした傾向はAWSだけでなく、Google CloudのTPUも、Microsoft AzureのMaiaも共通で、学習用であり推論用でもある。

今回AWSはガーマンCEOの基調講演の中で「負荷が高い推論はTrainium3で処理するのに適している」という非常に微妙な言い回しをしたが、Trainium3を学習だけでなく推論にも適していると強調した。

そうしたメッセージを打ち出す背景としては、前述の通りInferentiaに関しては後継製品が用意されておらず、事実上のディスコン(AWS自身は決してディスコンとは言っておらず、今でも販売は続いている)であるということと、新しいTrainium3が、実のところ推論向けといってよい設計になっているからだ。

AWSが「Trainiumでも推論」と言い出した背景には、Trainiumの強化点が推論で利用するデータ型の性能が強化されているから

以下の表はAWSが公開している資料から、Inferentia、Trainium(Inferentia2)、Trainium2、Trainium3のスペックなどを表にしたものだ。

| Inferentia | Trainium1/Inferentia2 | Trainium2 | Trainium3 | |

|---|---|---|---|---|

| 演算コア | NeuronCore-v1 | NeuronCore-v2 | NeuronCore-v3 | NeuronCore-v4 |

| 演算エンジン | Tensor/FP/Scalar | Tensor/FP/Scalar/GPSIMD | Tensor(スパース)/FP/Scalar/GPSIMD | Tensor(スパース)/MXFP/FP/Scalar/GPSIMD |

| ローカルメモリ | SRAM | SRAM | SRAM(28MB) | SRAM(32MB) |

| スパース | - | - | 対応 | 対応 |

| 演算コア数/ダイ | 4コア | 2コア | 4コア | 4コア |

| ダイ数 | 1ダイ | 1ダイ | 2ダイ | 2ダイ |

| 演算コア数/パッケージ | 4コア | 2コア | 8コア | 8コア |

| メモリ | 8GB(DDR4) | 32GB(HBM) | 96GB(HBM) | 144GB(HBM3e) |

| メモリ帯域 | 50GB/s | 820GB/s | 2.9TB/s | 4.9TB/s |

| インターコネクト(チップあたりの帯域幅) | NeuronLink-v1(非公表) | NeuronLink-v2(384GB/s、192GB/s) | NeuronLink-v3(1.28TB/s) | NeuronLink-v4(2.56TB/s) |

| MXFP4/MXFP8 | 未対応 | 未対応 | 未対応 | 2517TFLOS |

| INT8スループット | 128TFLOPS | 380TFLOPS | 非公表 | 非公表 |

| FP8スループット | 非公表 | 191TFLOPS | 1299TFLOPS | 2517TFLOS |

| FP16スループット | 64TFLOPS | 191TFLOPS | 667TFLOPS | 661TFLOPS |

| FP32スループット | 非公表 | 47.5TFLOPS | 181TFLOPS | 183TFLOPS |

| FP8/FP16/BF16/TF32(スパース)スループット | 未対応 | 未対応 | 2563TFLOPS | 非公表 |

| 製造プロセスノード | 非公表 | 7nm | 5nm | 3nm |

元々、Inferentia/Trainiumは、NeuronCoreというプロセッサコアをベースとしており、そのコア自体のアーキテクチャの拡張と、コア数を増やすという2つの方法で性能を引き上げてきた。初代InferentiaからTrainium(Inferentia2)では、NeuronCore-v2のマイクロアーキテクチャが拡大され、コア数は4コアから2コアに減ったが、FP16のスループットが3倍になるなど大きく性能が引き上げられた。

TrainiumからTrainium2への強化では、ダイ1つに統合されるNeuronCoreが2倍の4コアになっただけでなく、チップレットの採用により、2つのダイがパッケージに混載されており、コア数が4倍の8コアになっている。それにより、FP16のスループットは、Trainium比較で約3.5倍になる667TFLOPSが実現されている。

では、Trainium2からTrainium3への進化ではどうかといえば、4コアの2ダイが1パッケージというチップレット構成は変わっていないし、性能面、たとえばFP32のスループットでみるとほとんど変わっていない(Trainium2が181TFLOPS、Trainium3が183TFLOPS)。つまり、単純な性能では特に大きな進化はないと考えることができる。

ではどこが変わっているのかというと、4つある。1つ目が新しいデータ型の手法となるMXFP4/MXFP8に対応していること、2つ目がメモリの容量が増えて帯域幅が上がっていること、3つ目はローカルメモリが28MBから32MBに増量されていること、最後にチップ間インターコネクト(NeuronLink)の帯域幅が倍になっていることだ。

新しいMXFP4/MXFP8は、OCP(Open Compute Project)により規定されている新しいデータ型。MXFP4では、任意のプログラマーが規定したマッピングを利用して、Tensorエンジンが演算を行なう前にMXFP4をMXFP8にコンバートして演算する。そのMXFP4とMXFP8を利用した場合のスループットが2517TFLOPSになる。

なお、FP16/BF16/TF32でスパース性を利用した時にも2,517TFLOPSというスループットを実現する。こうしたMXFP4/MXFP8は推論を意識した実装で、AWSがTrainium3は推論にも使えると強調する背景にはこれがあると考えられる。

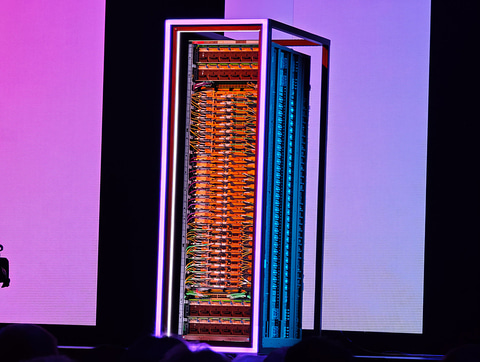

最後の強化点であるチップ間インターコネクトの帯域幅が倍になっていることは、1つのクラスタ(AWSではクラスタをUltraServerと呼んでいる)に格納できるチップの数が増えることを意味している。Trainium2のクラスタである「Trn2 UltraServer」では最大64基を1つのクラスタにできていたが、Trainium3のクラスタである「Trn3 UltraServer Gen2」では最大144基までクラスタ化することができるようになっている。

今回AWSはTrainium3単体の性能にはほとんど言及していないが、Trn3 UltraServerはTrn2 UltraServerに比較して性能が最大4.4倍、メモリ帯域が3.9倍、5倍のトークン/電力(同じ電力で処理できるトークン数、トークンの数が多ければ多いほど電力効率が高い)だと説明しているのは、こうした事情があるからだと考えることができる。

次世代Trainium4の構想を明らかに、FP4で6倍、FP8で3倍の性能向上などを実現

なお、今回AWSは、Trainium3の後継となるTrainium4に関しても構想だけを公開した。FP4利用時の処理能力が6倍に、FP8利用時の処理能力が3倍に、メモリ帯域は4倍に、メモリ容量は2倍になる。

また、NVIDIAが同社のチップ間インターコネクトNVLinkをサードパーティに半解放する「NVLink Fusion」に対応する計画で、NVIDIAのCPUやGPUなどと組み合わせて、より大規模にスケールアップしていくことが可能になる。

こうしたTrainium4に関しては、今回は存在が明らかにされただけで、それ以上の詳細はなかった。昨年(2024年)のre:Invent 2024で、Trainium3の構想が明らかにされ、今年には一般提供開始が明らかになったことからも分かるように、おそらく来年(2026年)のre:Invent 2026で詳細が明らかにされ、実際に提供されることになるだろう。

![レノボジャパン Lenovo ノートパソコン Chromebook Duet Gen9 [ 10.95型 / Chrome OS / MediaTek / メモリ4GB / eMMC128GB ] ルナグレー 83HH000UJP 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001243/4582763801897_1.jpg?_ex=128x128)

![【5日間限定20%オフクーポン!】中古ノートパソコン 第11世代 Panasonic Let's note SV1 12.1型 Core i5 [メモリ8GB/16GB SSD256GB/512GB/1TB] Windows11 Office付き 軽量 モバイルPC WEBカメラ Bluetooth 無線LAN HDMI 在宅勤務 テレワーク 学生向け ビジネス 高速起動 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/digitalcon/cabinet/12534579/12762892/sv1-i511.jpg?_ex=128x128)

![HP ProBook 450 G9(Win11x64) 中古 Core i7-1.2GHz(1255U)/メモリ16GB/512GB/フルHD15.6インチ/Wi-Fi6対応/Webカメラ [B:良品] 2022年頃購入 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/usedpc/cabinet/url1/5725981b.jpg?_ex=128x128)

![Dell デスクトップパソコン 23.8 型(インチ) Inspiron 24 5430 オールインワン AI57-EHHBW [パールホワイト] メモリ:8GB SSD:512GB Windows 11 Home Office付き 展示品 製品画像:3位](https://thumbnail.image.rakuten.co.jp/@0_mall/ryouhinkobo/cabinet/12804579/imgrc0101572424.jpg?_ex=128x128)

![Dell デスクトップパソコン 27 型(インチ) Inspiron 27 7730 オールインワン AI779T-EHHBBC [ダークシャドウグレー] インテル Core 7 150U メモリ:16GB SSD:1TB Windows 11 Home Office付き 展示品 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/ryouhinkobo/cabinet/12804579/imgrc0102216237.jpg?_ex=128x128)

![【エントリーで最大全額ポイント還元|5/6まで】 PHILIPS|フィリップス PCモニター ブラック 22E1N1100LA/11 [21.5型 /フルHD(1920×1080) /ワイド /120Hz] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/13552/00000014269493_a01.jpg?_ex=128x128)

![【エントリーで最大全額ポイント還元|5/6まで】 I-O DATA|アイ・オー・データ PCモニター ブラック KH-A221DB [21.5型 /フルHD(1920×1080) /ワイド /75Hz] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/9568/00000012607810_a01.jpg?_ex=128x128)

![100日後に英語がものになる1日10分 ネイティブ英語書き写し [ ブレット・リンゼイ ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2429/9784763142429_1_2.jpg?_ex=128x128)

![お隣の天使様にいつの間にか駄目人間にされていた件13 キャンバスアート付き特装版 (GA文庫) [ 佐伯さん ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4598/9784815644598_1_2.jpg?_ex=128x128)

![【特典】黄泉のツガイ 1~12巻 セット(ポストカード7種) (ガンガンコミックス) [ 荒川弘 ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6934/2100014846934.jpg?_ex=128x128)

![傲慢と善良 (朝日文庫) [ 辻村深月 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0597/9784022650597_1_12.jpg?_ex=128x128)

![中学英語をもう一度ひとつひとつわかりやすく。改訂版 [ 山田 暢彦 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/4821/9784053054821_1_5.jpg?_ex=128x128)

![いまさら聞けない看護図鑑 根拠をズッシリ詰め込みました! [ 看護師モカ ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0601/9784796580601_1_24.jpg?_ex=128x128)

![学研の学習 はにわの大国宝展 世界とつながるほんもの体験キット [ 東京国立博物館 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9822/9784057509822_1_4.jpg?_ex=128x128)

![呪術廻戦≡ 3 (ジャンプコミックス) [ 岩崎 優次 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0429/9784088850429_1_10.jpg?_ex=128x128)