ニュース

Zen 5は前世代からIPCが16%向上。3nm版も登場か?AMDがCPUの詳細を明らかに

2024年7月15日 22:00

AMDは6月のCOMPUTEX TAIPEI 2024開催時に、ノートPC向けのRyzen AI 300シリーズ、デスクトップPC向けのRyzen 9000シリーズといった、新しいCPUアーキテクチャ「Zen 5」を搭載した製品を発表している。そのときは概要の紹介のみにとどまっていたが、7月15日(現地時間)についに詳細が明らかにされた。

実行ユニットに大きく手が入ったZen 5

Zen 5のアーキテクチャは、フロントエンド(デコーダなど)、実行ユニット(スケジューラやALUなど)、バックエンド(ロード/ストア、データキャッシュなど)のいずれも手が入れられており、前世代となる「Zen 4」に比べて同クロックでも性能が向上していることが大きな特徴となる。

| Zen 4 | Zen 5 | |

|---|---|---|

| L1命令 | 32KB | 32KB |

| L1データ | 32KB | 48KB |

| L2 | 1MB | 1MB |

| L3 | 4MB | 4MB |

| デコーダ | 4命令/クロックサイクル | 4命令/クロックサイクル×2 |

| Op Cache | 9マイクロOps/クロックサイクル | 6マイクロOps/クロックサイクル×2 |

| ディスパッチ | 6Ops | 8Ops |

| スケジューラ(整数演算) | 4 | ユニファイドシェーダ |

| レジスタファイル | 224 | 240 |

| 実行ユニット(整数演算) | 8 | 10 |

| スケジューラ(浮動小数点演算) | 2 | 3 |

| 実行ユニット(浮動小数点演算) | 6 | 6 |

| FADDレイテンシ | 3 | 2 |

| AVX512実行 | 256bit幅 | 512bit幅 |

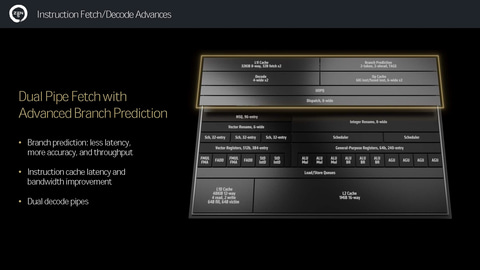

フロントエンドでは、デコーダとOp Cacheに大きく手が入っている。従来のZen 4のデコーダは1クロックサイクルあたり4命令を内部命令に変換できるようになっていたが、Zen 5では1クロックサイクルあたり4命令は変わっていないものの、そのデコーダユニットがデュアルパイプになっており、1クロックあたり4命令×2でデコード可能になっている。

また、そのデコードされた内部命令を保存しておくOp Cacheもデュアル化されており、Zen 4では1クロックサイクルで9内部命令となっていたが、Zen 5では1クロックサイクルで6内部命令×2(つまり12内部命令)が処理できる。

これらの強化により分岐予測の低遅延、正確性の向上、スループットの向上などが実現され、実行ユニットに命令を引き渡すディスパッチも1クロックサイクルでZen 4の6内部命令から8内部命令に引き上げられている。

要するに、x86命令をより内部命令に多く変換可能になっているということだ。

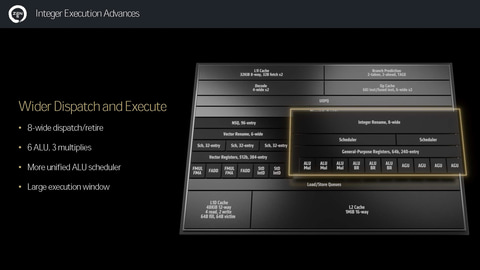

実行ユニットも同様で、整数演算器では内部の実行ユニットが2つ増やされている。Zen 4ではALUが5、AGUが3という8つの演算ユニットが用意されていたが、Zen 5ではALUが6、AGUが4となり、合計で10個の演算装置を利用して演算できる。

それに合わせてレジスタファイルも増やされており、Zen 4の224からZen 5では240に強化されているほか、スケジューラはZen 4に比べてより大型の統合されたスケジューラに強化されており、より効率よく整数演算を行なうことが可能になっている。

浮動小数点演算器も同様でスケジューラがZen 4世代の2つから3つに増やされているほか、Zen 4世代ではレジスタファイルが256bitになっていたため、AVX512の実行には2クロックサイクルが必要になっていたが、Zen 5ではレジスタファイルが512bitに強化され、1クロックサイクルでAVX512命令を行なえるようになっている。

また、浮動小数点演算ユニットのうちFADDの低遅延化が実現されるなどの強化で、より多くの浮動小数点命令を同時に処理可能になった。

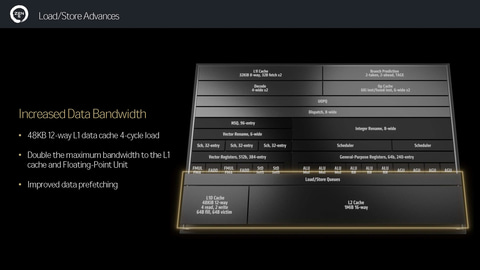

バックエンドでの強化では、L1データキャッシュが32KB(8ウェイ、3ロード/2ストア)から48KB(12ウェイ、4ロード/2ストア)へと強化されている。これにより、L1キャッシュの帯域幅は2倍になり、データの読み込み速度が大きく向上している。

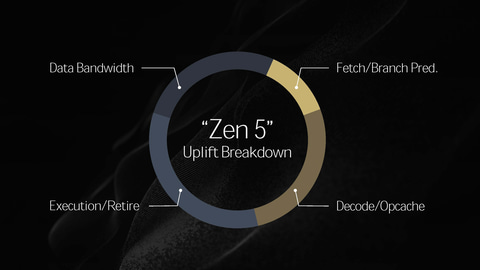

TSMCの4nm、3nmに最適化

AMDによれば、Zen 4世代の強化では主にフロントエンドとバックエンド(ロードストア)の強化が大きかったが、Zen 5では実行ユニットの強化が性能向上に大きく貢献しているとのことで、整数演算器と浮動小数点演算器それぞれが強化され、性能向上につながっていることが分かる。

Zen 5の性能向上は、同じクロック周波数で比較した場合、平均して16%の性能向上が確認できるという。つまり、IPCが16%向上しているわけだ。

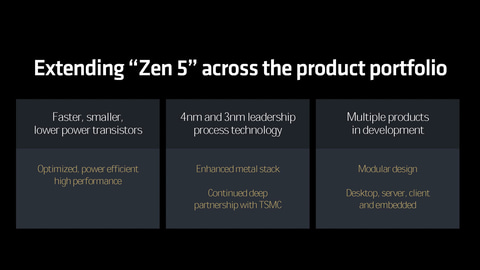

Zen 5はTSMCの4nmと3nmに最適化されているという。今回同時に発表されたノートPC向けのRyzen AI 300シリーズ、デスクトップPC向けのRyzen 9000シリーズはいずれも4nmで製造されており、今後どこかのタイミングで登場する将来の製品では3nmで製造されるオプションがあるということだ。

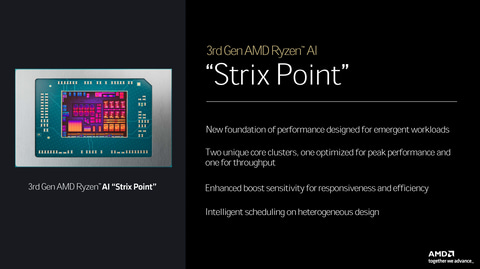

また、Zen 5にはL3キャッシュをCPUコア1つあたり1MBにした「Zen 5c」のオプションが用意されており、小型CPUデザインとして活用することもできる。

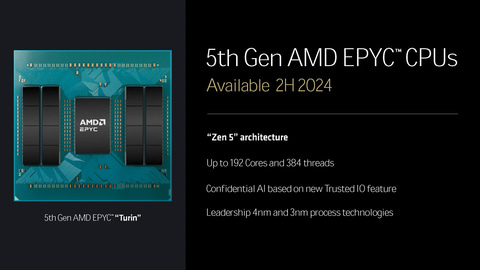

このZen 5cは、異種混合(ヘテロジニアス)なCPUコアとして、Intel的な言い方をするならEコアとしてRyzen AI 300シリーズに採用されているほか、将来的には第4世代EPYCでそうであったように、高密度バージョンとして第5世代EPYCで採用される可能性がある。

なお、AMDはこのZen 5の後継としてZen 6、そのコンパクトバージョンとしてZen 6cを開発していることをすでに明らかにしている。

![一体型pc タッチパネル[第13世代CPU] オールインワン All-in-One デスクトップパソコン 一体型pc 23/27型 フルHD液晶一体型 インテル Core i5-3320M i7【Windows 11搭載】 一体型パソコン メモリー8~16GB SSD 128~1024GB PSE認証済 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/phi777/cabinet/11118046/11823533/imgrc0153403213.jpg?_ex=128x128)

![[アウトレット] ゲーミングモニター ホワイト パステル ブルー 200hz 24インチ pcモニター 144Hz 165Hz対応 モニター 白 フルHD IPS HDR ノングレア スピーカー搭載 VESA 23.8インチ 液晶ディスプレイ Pixio ピクシオ 公式 PX248WAVE 製品画像:9位](https://thumbnail.image.rakuten.co.jp/@0_mall/pixiogaming/cabinet/outlet/px248w-outlet.jpg?_ex=128x128)

![WINTEN モバイルモニター 15.6インチ テレワーク/デュアルモニター/サブモニターに最適!ゲーミング 1080P FHD IPSパネル 軽量 薄型 非光沢 カバー付 ミニPC Switch iPhone Type-C/HDMI接続 [1年保証] WT-156H2-BS 5523 製品画像:8位](https://thumbnail.image.rakuten.co.jp/@0_mall/win10/cabinet/monitor/imgrc0112809238.jpg?_ex=128x128)

![三省堂 例解小学国語辞典 第八版 オンライン辞書つき オールカラー [ 田近 洵一 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9623/9784385139623_1_2.jpg?_ex=128x128)

![はる!たまごっちコネクション まるごとシールブックDX [ 小学館 ] 製品画像:28位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6110/9784097356110_1_12.jpg?_ex=128x128)

![キングダム 79 (ヤングジャンプコミックス) [ 原 泰久 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1967/9784088941967_1_10.jpg?_ex=128x128)

![鬼の花嫁9巻【電子書籍】[ 富樫じゅん ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/2774/2000020132774.jpg?_ex=128x128)

![螢雪時代4月臨時増刊 全国大学 学部・学科案内号 2026年 4月号 [雑誌] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0468/4912033620468_1_2.jpg?_ex=128x128)

![回復術士のやり直し(18) 【電子書籍】[ 月夜 涙 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9001/2000020419001.jpg?_ex=128x128)

![弱虫ペダル 100 【電子書籍】[ 渡辺航 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/6942/2000020406942.jpg?_ex=128x128)

![悪役令嬢転生おじさん(10) 【電子書籍】[ 上山道郎 ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/0539/2000020190539.jpg?_ex=128x128)