大原雄介の半導体業界こぼれ話

次期CPU「Zen 6=大変革」説に物申す。AMD公式文書を冷静に読み解いてみた

2025年12月23日 09:56

12月12日、AMDは技術文書をアップデートし、「Performance Monitor Counters for AMD Family 1Ah Model 50h-57h Processors」を公開した。ちなみにこれに最初に気が付いたのはInstLatX64である。

AMD Family 1Ah Model 50h-57h Processorsは何なのか、まだAMDは公式に説明していないが、そもそもこの文書のファイル名が「69163-VenicePMC-pub.pdf」である時点でVenice――つまりZen 6ベースのEPYCプロセッサであることは明白であり、これはZen 6の内部構成に関する最初のドキュメントであると判断してよいと思う。

Performance Monitor Counterから分かった事実

このPerformance Monitor Counterとは何か?というとCPU内部の性能に関わる状況を記録するためのもので、Profilerと呼ばれる情報取得ツールを利用して性能分析を行なう際に利用される(このProfilerまで含めた分析ツールは「AMD μProf Performance Analyzer」として提供されている)。

ちなみにこのAMD μProf Performance Analyzerは、「AMD μProfという開発ツール」のコンポーネントの1つであり、無償で入手して利用できる。原稿執筆時点での最新版は12月11日リリースのRelease 5.2であり、先のドキュメントは翌日のリリースというのは、つまり次のμProf(Release 5.3?)で、Zen 6への対応が果たされる予定ということと考えて良いだろう。

さて、このPerformance Monitor Counterは別にZen 6で初めて入ったわけではなく、以前から用意されている。EPYC 9005シリーズ、つまりZen 5 EPYCについてはこちらのドキュメントで説明されている。

ここまでは普通のことなのだが、このZen 6対応のPerformance Monitor Countersのドキュメントについて、Zen 6はZen 5の延長線にない、スループット志向のアーキテクチャであると言い出したサイトがある。Tom's Hardwareのこの記事のことであり、この記事を受けて、多くの情報系サイトが一斉にZen 6で大きく中身が変わると騒ぎ出した。

8-wideはZen 5からだった?

……なのだが、筆者がこれを読んでも、どう見てもそう思えないのである。そこでちょっと真面目にドキュメントを読み解いてみたいと思う。

まずPerformance Monitor Counterの配置であるが、

- スレッドあたり6つ、L3 Complexあたり6つ、データファブリック(Data Fabric)あたり16のPerformance Event Counterが搭載されている

- 各々のPerformance Event Counterは、RDPMC(ReaD Performance-Monitoring Counters)命令で読み出しできる

- RDPMC[5:0]はCore Eventに、RDPMC[9:6,1B:10]はData Fabric Eventに、RDPMC[F:A]はCache Eventにそれぞれアクセスする

となっており、これはZen 5/Zen 6で共通である。

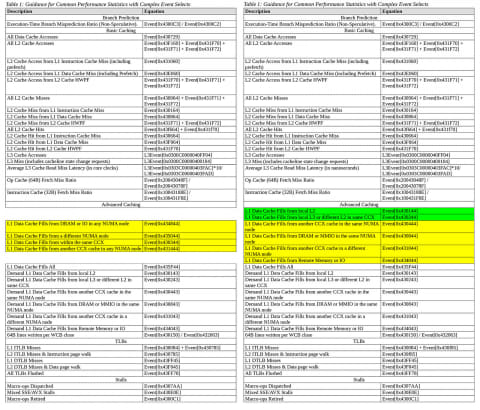

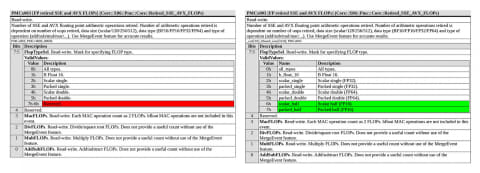

次いでCommon Performance Statistics(一般的なパフォーマンス統計)を比較したのがこちら(図1)。左がZen 5、右がZen 6である。黄色が変更箇所、緑が新規追加である。コアそのものには特に変更はなく、L1データキャッシュフィルの際に、それがどこからフィルされたのかを、より詳細に取得できるようになっているのが主な相違点であり、ほかに違いはない。

3番目はPipeline Utilization Analysis Statistics(パイプライン利用率分析統計)の比較である(図2)。命令パイプラインに関わるところで、同じく左がZen 5、右がZen 6である。

ここで、実はTotal Dispatch Slots(合計ディスパッチスロット)の説明が異なっている(黄色部)のだが、実はこれZen 5の側はTypoであろうと判断できる。

というのも、「Up to 6 instructions can be dispatched in one cycle(1サイクルで最大6つの命令をディスパッチできる)」となっているのに、Equation(方程式)は「8 * Event」というのは明らかにおかしいからだ。あと、これはAMDの説明とも異なる。

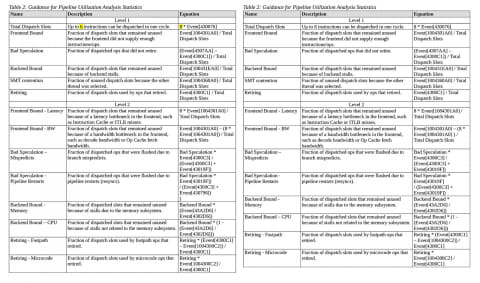

図3は昨年のHot Chipsで説明された、Zen 5の内部構造である。フロントエンド(Front End)の最後、MicroOp Queue(キュー)の下には明確に「Dispatch 8-wide」と書かれているのがお分かりかと思う。

Tom's Hardwareの記事では「wide, throughput-oriented design with an eight-slot dispatch engine and simultaneous multi-threading(8スロットのディスパッチエンジンと同時マルチスレッドを備えた、幅広いスループット重視の設計)」などと書いてあるが、これを見る限りZen 6もZen 5と同じく8-wideのデコード構造と考えざるを得ない。なので、基本的にはパイプラインに関わるところは大きくは変わらないと考えられる。

ただ、改善がないわけではない

まったく違いがないわけではない。たとえば、PMCx003(FP retired SSE and AVX FLOPs)というカウンタ(図4)のValid Value、Zen 5(左側)で6h-7hは「Reserved」なのに、Zen 6(右側)ではFP16の「Scalar half/Packed half」に割り当てられている。これは要するにZen 5ではサポートされていなかったAVX512-FP16(Packed FP16)と、FPUでのFP16(Scalar FP16)の動作がZen 6でサポートされていることを示唆している。

面白いものとしては、今回PMCx00F(FP packed 512 uops retired by FP or INT type)およびPMCx013(FP NSQ Read Stalls)が追加されたことが挙げられる(図5)。

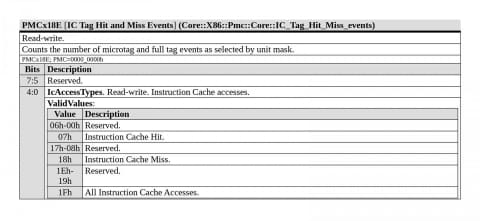

PMCx00F、PMCx013はともにZen 5世代に存在しなかったことが不思議ではあるのだが、単にいろいろ追いついていなかったのかもしれない。PMCx00Fは512bit動作(つまりAVX512動作モード)における動作をモニターするもの、NSQはNon-Scheduled Queueの状態をモニターするもので、どちらもZen 6以前から搭載されているものである(512bit幅のAVX512動作はZen 5世代で実装されている)。逆にPMCx18E(IC Tag Hit and Miss Events)(図6)はなぜかZen 6では落とされている。

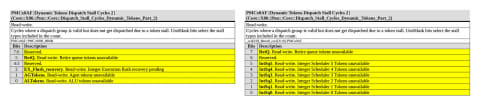

結構激しく違っているのがPMCx0AF(Dynamic Tokens Dispatch Stall Cycles 2)である(図7)。左のZen 5世代では、Dispatch Groupを纏めて扱っているのに対し、右のZen 6世代ではInteger Scheduler 1~6(整数スケジューラ1~6)とRetire(リタイア)について、各々トークンの有無をチェックする仕組みになっている。より細かく、どのスケジューラが遊んでいるかを監視できるわけだ。

実はここでスケジューラが1~6まであり、かつ先の図2のTypoに引っかかって、Zen 6では8-Wideのディスパッチエンジンを、6つのドメインに分割するとかいうわけの分からない解釈が生まれてきたっぽいのだが、ここでもう一度図3を見直してほしい。

ディスパッチはZen 5の世代ですでに8-wideある。この出力の整数側はリネームを経てスケジューラに入るわけだが、これはZen 5の世代ですでに6-wideになっている。というか、単にALU×6が実装されており、このALUに対するスケジューリングがどこまで有効かを計測するためにカウンタの構成を変えた、という話にしか筆者には読めない。

ついでに言えば、Zen 6でこれが実装されているということは、つまりこの辺の構造はZen 5とZen 6で変化がないということにも読み取れると思う。

Zen 6はZen 5のリファインだ

それ以外には(筆者が調べた限りでは)違いが見当たらなかった。要するに、PMCx18Eみたいな例外はあるものの、基本的にはZen 6でやや細かくPerformance Counterを取得できるようになったこと、それとFPU/AVX512にFP16のサポートが追加されたこと、だけが現時点でZen 5とZen 6の違いとして示されている内容であり、根本的な設計方針の変更といった話は今回のドキュメントから読み取ることは一切できなかった。

筆者が思うに、構造そのものは図3とほとんど変わらないままだと思う。といっても、たとえばx86命令からMicroOpに変換する方法の改良とかスケジューラ内のスケジューリング技法の改良、分岐予測の改良(まだTAGEベースを維持するのかどうか、現時点では不明)など、構造を変える前にやれることは多いと思うからだ。

現状でも8命令デコード、10命令発行というかなり強力なパイプラインであり、しかもこれがフルに生かされているかどうかはちょっと疑問である。次々世代、つまりZen 7やその先まで行けばもっとデコードやディスパッチの幅を広げるかもしれないが、Zen 6世代ではZen 5をベースに効率を上げる方向に進化するのが妥当なように思える。

そもそもスループットコンピューティングは、過去に苦汁をなめたBulldozerの設計方針そのものであり、まぁAMDが今さらあの路線に回帰するとは思えない。また昨今のスループット重視はAIワークロードに向けたものであり、であればCPUパイプラインをいじるより、AMXとか(Armの)SME2のような行列演算を高速に実行できるアクセラレータを搭載する方が簡単かつ効率的である。

ということで、Tom's Hardwareの分析は間違いである、というのが筆者の結論である。

![Microsoft|マイクロソフト ノートパソコン 特別モデル Surface Pro 12インチ プラチナ + キーボード(スリムペン付き)+ 充電器 EP2-46399 [Copilot+ PC /12.0型 /Windows11 Home /Snapdragon X Plus /メモリ:16GB /UFS:256GB /M365 (24か月) or Office 選択可能] 製品画像:1位](https://thumbnail.image.rakuten.co.jp/@0_mall/biccamera/cabinet/product/15530/00000014704980_a01.jpg?_ex=128x128)

![IOデータ ゲーミングモニター KH-GD251UH 240Hz&フルHD対応 GigaCrysta [24.5型 / フルHD(1920×1080) / ワイド / 240Hz] ブラック 製品画像:2位](https://thumbnail.image.rakuten.co.jp/@0_mall/r-kojima/cabinet/n0000001504/4957180184845_1.jpg?_ex=128x128)

![怠惰な悪辱貴族に転生した俺、シナリオをぶっ壊したら規格外の魔力で最凶になった Vol.3 【電子書籍】[ 菊池 快晴 ] 製品画像:30位](https://thumbnail.image.rakuten.co.jp/@0_mall/rakutenkobo-ebooks/cabinet/9037/2000020419037.jpg?_ex=128x128)

![【楽天ブックス限定特典】MGA MAGICAL 10 YEARS ANNIVERSARY BOOK -OUR STORY-(限定絵柄ポストカード1枚) [ Mrs. GREEN APPLE ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2004/2100014772004_1_2.jpg?_ex=128x128)

![チャイロイコグマの10th Anniversary BOOK (生活シリーズ) [ サンエックス ] 製品画像:26位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5606/9784391645606.jpg?_ex=128x128)

![転生したらスライムだった件(32) (シリウスKC) [ 川上 泰樹 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/7544/9784065437544_1_2.jpg?_ex=128x128)

![地球の歩き方 スター・ウォーズ [ 地球の歩き方編集室 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/6939/9784058026939_1_2.jpg?_ex=128x128)

![大きな活字の新明解国語辞典 第八版 [ 山田 忠雄 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0873/9784385130873.jpg?_ex=128x128)

![takt op. 運命は真紅き旋律の街を OFFICIAL ARTWORKS [ DeNA ] 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1385/9784768331385_1_5.jpg?_ex=128x128)