大原雄介の半導体業界こぼれ話

エクサバイトを実現するDNAストレージと、TSMCの先端パッケージ施設の話

2024年3月22日 06:13

DNA Data Storage Allianceが最初の仕様をリリース

3月12日、SNIA(Storage Networking Industry Association)はAffiliate AllianceであるDNA Data Storage Allianceが最初の仕様である「DNA Data Storage Sector Zero」と「DNA Data Storage Sector One」をリリースした。

DNAストレージの話が何かないか? と探したら、2017年の記事が見つかった。

元々DNAを記憶素子として使おうというアイデアを出したのは物理学者のリチャード・P・ファインマン博士で、1959年12月29日に行なわれたアメリカ物理学会の総会の際に「There's Plenty of Room at the Bottom」というタイトルで講演を行ない、この中でDNAを利用した記憶素子というアイデアを述べている。もっともこの時はあくまでもアイデアが示されたに過ぎない。

ただその後、DNA解析とかDNA操作の技術の進化により、コストとかアクセス時間(という表現が適切かどうかは不明だが)が大幅に削減されるようになった。もちろん、アクセス時間は、ある一連のDNA群の変更に数十日を要していたのが数日になったとか、1日未満になったとかのレベルなので、まだ実用の範囲には至っていないのだが。

先に示した記事の翌年には、ワシントン大学とMicrosoftが共同で、200MB以上のデータを格納したDNAストレージへのランダムアクセスを行なうことに成功したという論文を発表、2019年には同じチームがDNAに格納するデータのエンコード/デコードを完全自動化することに成功したと発表している。

ほかにもDNAストレージに関する研究や論文はいろいろ行なわれており、こうした機運を受けて2020年10月にDNA Data Storage Allianceが立ち上げられた。創業メンバーはIllumina、Microsoft、Twist Bioscience、Western Digitalの4社である。この4社が同時にボードメンバーになっており、2021年10月の時点では35のメンバー企業/団体が加盟していた。

ちなみに現在は? というと、メンバーのページによればボードメンバーがCatalog、Quantum、Twist Bioscience、Western Digitalの4社で、ほかにメンバー企業/団体が34となっている。

一番不可解なのが、illuminaとMicrosoftがボードだけでなくメンバー企業からも外れていることだ。またメンバー企業もいろいろと入れ替わっており、何かしら水面下であったように思うのだが、詳細は不明なままである。

DNAストレージの仕様

さて、そのDNA Data Storage Allianceは2022年6月にSNIAと技術提携を結んでいることもあり、今回の発表もSNIAからリリースが出ている(DNA Data Storage Alliance自身はリリースを出していない)。その内容であるが、最初に書いた通り今回のリリースは、DNA Data Storage Sector ZeroとSector Oneの仕様を規定した、というニュースである。

この仕様は、要するにDNAストレージにどう記録を保存するかを規定したものであって、DNAストレージそのものの仕様ではない。なぜこんな保存法を規定する必要があるか? というと

- DNAストレージは、従来のストレージと異なっており、特定の物理的な順序のスキームがない。HDDだったら最外周にセクター0があるし、NANDフラッシュなら0番地がスタートになるわけだが、DNAストレージにはこうした物理的なスタート位置というものが存在しない

- DNAストレージには現在の所専用のコントローラもなければ、それを利用するためのAPIもない。そもそもまだ物理的にDNAストレージを作る手法が確立していないので、将来そうしたものが出てくる時に、コントローラやAPIを構築するための共通手法を先に決めておくことで、複数規格が乱立したりしないように注意する必要がある

- DNAストレージ内部の記録手法そのものも決まっていない

といった理由が挙げられている。これを解決するために、DNAストレージの内部に

- DNAストレージのアーカイブ作成ベンダーと、利用するコーデックは何かを示す(Sector Zero)

- アーカイブの論理的構造、およびコーデックの詳細を示す(Sector One)

を設け、コントローラはまずSector Zeroを読み出し、次いでこれを利用してSector Oneを読み出すことで、DNAストレージの内部にアクセスできるようにする、という手順を定めた形だ。

ちなみにそのSector Zeroの構造はこんな感じ(図1)。「base」というのは塩基のことで、要するにDNAを構成する4つの塩基(A:Adenine C:Cytosine G:Guanine T:Thymine)のどれかが入ることを示す。

ここで「Fwd Sector Zero Primer」と「Rev Sector Zero Primer」は、これがSector Zeroであることを示すもので、

- Fwd Sector Zero Primer:GCCTCGGTACACGGTATGAG

- Rev Sector Zero Primer:ATGCTCCAGTTCGGTCAGTG

になることが決まっている。要するにこのFwdとRevの2つのAmp Primerに挟まれた70basesがSector Zeroの中身ということになる。

ちなみにその中身も決まっており、前半の35baseがアーカイブ生成ベンダーのVendor Codeで、現在はTwist Bioscience/Microsoft/Dellの3社のIDが定められている。後半の35baseはCodecを示すCodec Codeで、現在はSuper Codec/Hyper Codec/Jimbob's Codecの3種類が定義されている。

同様にSector Oneの構造がこちら(図2)。Sector Zeroと似た構造だが、異なるのはSector Oneが複数のヌクレオチドから構成できることである。またペイロード部分、つまり中身はJSONで記述されており、Sector Zeroで指定したCodecを利用することになっている。

ここで延々と中身を説明しても仕方がないので割愛する(仕様そのものはSNIAから無償で入手できる(Sector Zero、Sector One、リンク先はPDF直)ので、興味ある方は確認していただきたい)が、おもしろいのはこのSector ZeroやSector Oneが「システムに1つ」とはどこにも記述がないことだ。

Western Digitalが2023年2月24日に掲載したブログ投稿によれば、18TBを格納できるLTO-9カートリッジと同じ容積に、DNAストレージだと2EB近くを格納できるとする。

先に書いたように、今のところDNAストレージには特定の物理的な順序のスキームがない。ということは、もしSector ZeroやSector Oneが1カ所にしかなかったら、それを探すために2EBのストレージエリアを全部なめることになりかねない。これを避けようとしたら、Sector ZeroやSector Oneを複数置き、最小限の検索でSector Zeroを読み込めるようにするといった実装が考えられる。ちょっと従来のストレージとはだいぶ様相が異なっていることが、ここからも推察できる。

先のWestern Digitalのブログは、TechTarget(米国版)の2021年4月の記事を引用して、「『2024年までに、デジタル企業の少なくとも30%がDNAストレージを試行するようになる』と推定しています。」としているが、ご存じの通り、まだ試行できるようなDNAストレージそのものが存在していない。今のままだと、2030年までに出るかどうかも怪しい感じではある。ただ、最終的にどんな形でいつ出るかは不明ながら、そこに向けて各社が努力を積み重ねているのは事実であり、今回の仕様もこうした努力の1つと数えられよう。

TSMCが先端パッケージング工程を日本に建設?

3月18日、TSMCが先端パッケージング工程を日本に建設することを検討しているという報道がロイターなどであった。これに関していろいろな意見が出ているので、大原の私見を述べておく。

まず前提となる話をいくつかしておくと、

立地とは関係ないパッケージング工程

そもそもパッケージング工程は、本来立地に依存しない。たとえばIntelで言えば、前工程はアリゾナとかオレゴン、最近だとオハイオにも建設を開始したが、あとはアイルランドとかイスラエルである。一方後工程はニューメキシコとマレーシアである。もし立地に依存、つまり前工程工場と近いところに置くべきというのであれば、そもそもニューメキシコやマレーシアに置くべき理由がない。

これはOSATを使った場合も同じで、台湾のASEとか米国のAmkor、中国JCET(STATS ChipPAC)など多数のOSATメーカーがあり、複数の製造拠点を構えているが、別に必ずしもファウンドリのそばに立地しているというわけでもない。

コストが重要

では何を重視しているのか? といえば、コストである。土地や建物だけでなく、電力や人件費、そのほかの要するに運用コストと呼ばれるものが安いことが重要視される。

もちろん、大前提として、その前にインフラが整っており、高等教育を受けたエンジニアを集めやすい場所で、治安が良いことや、流通網が発達していることなどが当然挙げられる。

先端パッケージングでは話が変わる

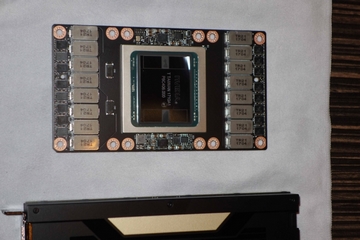

ただし、パッケージング工程の中でも先端と呼ばれる部分だと話は変わる。つまり、TSMCで言えばCoWoSとかInFO、SoICに相当するものだが、これはちょっと話が変わってくる。

たとえばCoWoSであれば・シリコンインターポーザそのものは前工程を利用して製造されるためだ。シリコンインターポーザは、トランジスタ層とM0~M3あたりがないだけで、あとは通常の配線工程をそのまま利用して製造される。

ということは、EUVこそ要らないし、トランジスタ層を構築する際にのみ必要となる(=配線層には必要ない)成膜工程や洗浄工程こそ省けるが、基本前工程と同じ製造装置や製造工程が必要になる。

SoICもそうで、これは2種類のダイをバンプではなくファンデルワールス力を利用して接続する技法だが、このためには2種類のダイの接合面を極めて滑らかにしてやる必要がある。これは従来後工程で利用していた研磨装置のレベルでは不十分で、前工程でトランジスタの構築を行なう際に利用するようなCMPを含む研磨装置を使うことになる。

要するに先端プロセスの前工程の製造技術を応用する形で、こうした先端パッケージ技術が実現しているわけだ。

OSATがこうした先端プロセスで一歩遅れているのは、同じことを実現しようとすると前工程のFabと同じ製造装置というか製造ラインを導入する必要があり、コスト的にこれが敵わないためである。

たとえばASEのFOCoS(Fan-Out Chip on Substrate)のように、既存の後工程の設備を利用した3Dソリューションを提供しているベンダーも存在するが、どうしても限界はある。あるいは最近だとシリコンインターポーザ以上の配線密度を有機パッケージで実現している例も存在する(AMDのRadeon RX 7000シリーズで、GCDとMCDの間の接続がこれである)が、これが全面的にシリコンインターポーザを置き換えられるわけでもない。

といったあたりだ。以上を念頭に置いた上で。昨今の先端パッケージのビジネスを見ると、今後チップレットなどの普及がより進む(今年のGTCで、ついにNVIDIAもBlackwellにマルチチップ構成を導入したことが明らかにされた)ことは明白である。

実は今でもTSMCの先端パッケージのビジネスはかなり需要が高いというか、供給が追い付いていないほどであり、しかもこの先さらに需要が増えることも見えている。なので先端パッケージの供給能力を高めたいと思うことそのものは当然である。

その一方で、TSMCの先端パッケージは前工程のラインを利用して提供されているわけで、であれば先端パッケージ施設そのものは、前工程の施設とあまり遠くない場所(できれば同じ敷地内位)に設けたいと考えるのは自然である。場合によっては前工程施設と先端パッケージ施設の間をウェハが何度か行き来することもありえるからだ。手間を考えると、前工程のクリーンルームを拡充して、そこに先端パッケージ施設を設ける辺りを考えて居るかもしれない。

ところが、現在のTSMCの台湾のファブは、もうそういう施設拡充の余地があまりない。現在TSMCが投資を行なって拡充しているのは2nmとかの先端プロセスであって、ここに先端パッケージ向けの設備を入れるのは無駄が多いというか、そこまで先端である必要性がない。

現状必要なのは28nm世代あたりの配線層を実現できることで、今後はこれが16nm世代あたりまで微細化され、その先には7nm世代あたりまで行くかもしれないが、それでも配線層そのものはそこまで微細化が進まない(M4以上を使うため)から、ArF+液浸でダブルパターニングがあれば十分対応ができる。

ただ。現状TSMCのこうした“Mature”なファブにはもう基本新規投資が行なわれない(現在は投資回収フェーズに入っている)から、ここに先端パッケージ設備を新設するのはちょっと厳しいものがある(前工程の製造能力を引き上げないといけないためだ)。

ではどうするか? というと、ちょうどこれからまさにMatureな28nm/22nmの前工程プロセスを立ち上げようとしている場所がある。要するに日本とドイツだ。

米国でもまさに新工場を立ち上げようとしているが、こちらは先端プロセス向けということもあってちょっとニーズとマッチしていない。であれば、この日本やドイツのラインについて、「後で先端パッケージ向けの量産も追加される」ことを配慮しておくのは難しくないし、先端パッケージ施設を追加するのも容易だろう。

日本とドイツ、インフラやコストの面でも、集める必要のあるエンジニアの質についても条件的には同等と思われる。少なくとも、そのほかの地域に新たに立ち上げるよりはずっと条件が良い。

日本で言えば、JAMS(Japan Advanced Semiconductor Manufacturing)の第1工場は既に立ち上がっており、しかもシリコンインターポーザの製造に適した28/22nm世代と16/12nm世代のプロセスを手掛けている。

ドイツのESMC(European Semiconductor Manufacturing Company)は2027年末の立ち上げであり、ここはここで後追いで先端パッケージ施設が追加される可能性はあるが、今から3年待てるか? といえば待てないわけで、先んじて日本に先端パッケージ施設を立ち上げる公算は決して低くないと筆者は考える。

先のロイターの報道では「検討は初期段階で、規模や時期など詳細は決まっていない」とあったし、実際そうだと思うが、もし決断がなされたらすぐに立ち上がるかもしれない。

![マウスコンピューター 15.6型 IPS方式 フルHD モバイルモニター iiyama ブラック P1671HSC-B1J [P1671HSCB1J]【RNH】 製品画像:13位](https://thumbnail.image.rakuten.co.jp/@0_mall/edion/cabinet/goods/ll/img_560/4948570127375_1.jpg?_ex=128x128)

![大人の科学マガジン BESTSELECTION07 小さな活版印刷機 [ 大人の科学マガジン編集部 ] 製品画像:29位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9501/9784057509501_1_3.jpg?_ex=128x128)

![学校では教えてくれない大切なこと 48 働くってどういうこと? 今の自分が未来をつくる [ 旺文社 ] 製品画像:27位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/5480/9784010115480_1_2.jpg?_ex=128x128)

![殺人の門 下 新装版 (角川文庫) [ 東野 圭吾 ] 製品画像:25位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/8752/9784041168752_1_13.jpg?_ex=128x128)

![公共建築工事標準仕様書 建築工事編(令和7年版) [ 国土交通省大臣官房官庁営繕部 ] 製品画像:24位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/1175/9784938421175_1_2.jpg?_ex=128x128)

![公共建築改修工事標準仕様書(建築工事編)(令和7年版) [ 国土交通省大臣官房官庁営繕部 ] 製品画像:23位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/2773/9784907762773_1_2.jpg?_ex=128x128)

![イヤーノート 2027 内科・外科編 [ 岡庭 豊 ] 製品画像:22位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/9681/9784896329681_1_6.jpg?_ex=128x128)

![ViVi (ヴィヴィ) 2026年7・8月合併号 増刊 [雑誌] 表紙:JI-DF ver. 與那城奨、白岩瑠姫、河野純喜(JO1)、後藤威尊、佐野雄大、池崎理人(INI)付録:JI BLUE フォトアルバム 製品画像:21位](https://thumbnail.image.rakuten.co.jp/@0_mall/book/cabinet/0866/4912013800866_1_3.jpg?_ex=128x128)