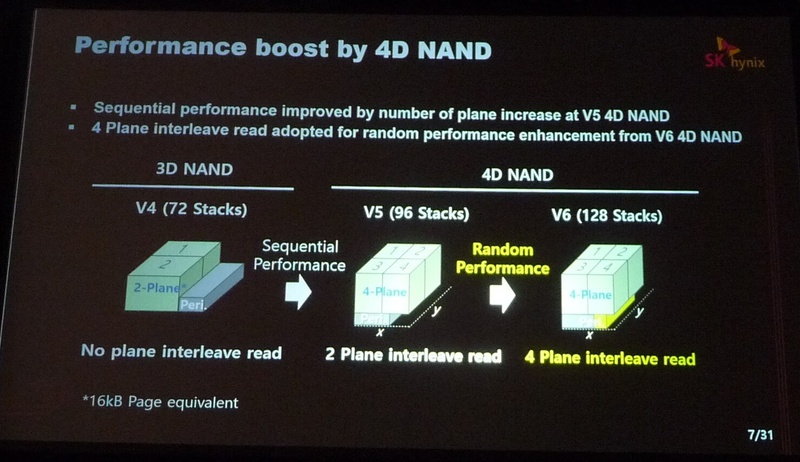

メモリセルアレイの分割。第4世代(V4)ではメモリセルアレイを物理的には2個のプレーンに分割していた。ただし、各プレーンを交互に連続して(インタリーブして)アクセスする回路は設けていなかった。次の第5世代(V5)では、メモリセルアレイを物理的には4個のプレーンに分割した。回路的には2個のプレーンを交互に連続してアクセスできるようにした。この回路によってシーケンシャルアクセスの速度を高めた。最新の第6世代(V6)では、4個のプレーンすべてを交互に連続してアクセスできるようにした。この工夫によってランダムアクセスの速度も高めた。SK Hynixによるキーノート講演のスライドから