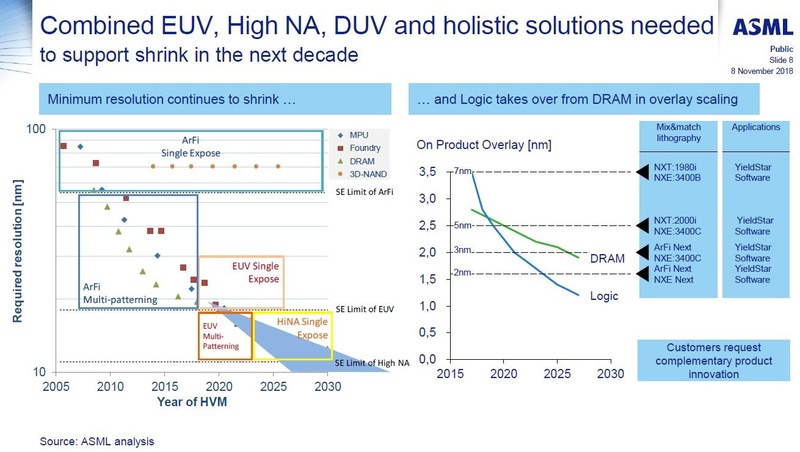

最先端半導体の製造を支えるリソグラフィ(露光)技術のトレンドと将来予測。左のグラフは主要な半導体製品とそのリソグラフィ(露光)技術のトレンド。マイクロプロセッサ(グラフ内の「MPU」、以下同じ)とロジック(Foundry)、DRAMは2020年以降も微細化を継続する。これまではArF液浸(ArFi)露光とマルチパターニングの組み合わせ(青色の実線による囲み)によって微細化を進めてきた。今後は、EUV露光(橙色の実線による囲み)が微細化を牽引する。EUV露光でもマルチパターニングを組み合わせる。そして2020年代後半には、次世代のEUV露光(HiNA、黄色の実線による囲み)を導入する。右のグラフはロジックとDRAMの量産における重ね合わせ誤差のトレンド。7nm世代では重ね合わせ誤差が3.5nmだったのを、5nm世代では2.5nm、3nm世代では2.0nmと減らしていく。今後はDRAMよりもロジックのほうが、重ね合わせ誤差に対する要求が厳しくなる。ASMLが2018年11月にアナリスト向け説明会で公表したスライドから