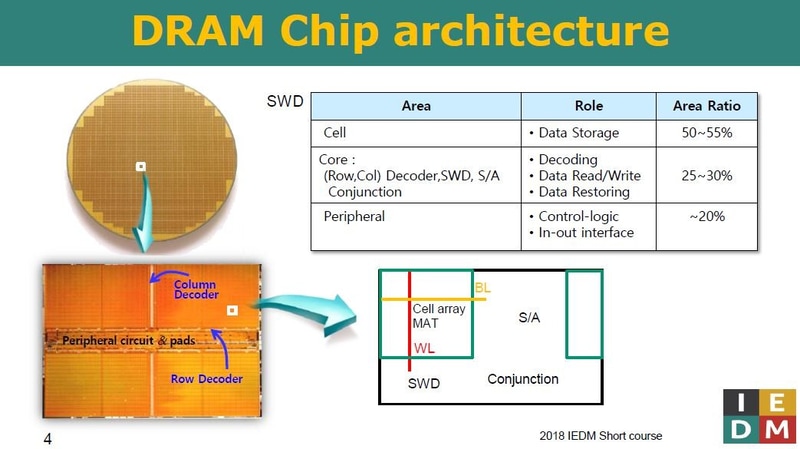

DRAMの基本的なアーキテクチャを説明した図面。左上がシリコンウェハの写真(実際の直径は300mmと推定)。左下がDRAMのシリコンダイ写真。シリコンダイの中央左右には周辺回路と入出力パッド、行デコーダ(Row Decoder)、中央上下には列デコーダ(Column Decoder)、残りの上下左右(四角い部分)にはメモリセルのアレイ(「サブアレイ」とも呼ぶ)を配置してある。図面の右下はメモリセルアレイ(サブアレイ)の基本構造。赤色のワード線(WL)と黄色のビット線(BL)の交点に1個のメモリセルを配置する。ワード線の端部はサブワード線ドライバ(SWD)、ビット線の端部はセンスアンプ(S/A)につながっている。図面の右上はシリコンダイ面積に占める各部の比率。メモリセルが50~55%、コア(デコーダ、ドライバ、センスアンプ、相互接続)が25~30%、ペリフェラル(制御回路と入出力回路)が20%前後を占める。Samsung Electronicsが2018年12月に国際学会IEDMのショートコース(技術講座)で示したスライドから