|

■後藤弘茂のWeekly海外ニュース■Intel最大のモンスターチップ「Tukwila」の概要が明らかに |

●システムアーキテクチャが刷新されたTukwila

Intelの次世代CPUファミリの最上位に位置するのが、65nmプロセスのクアッドコアIA-64プロセッサ「Tukwila(タックウイラ)」だ。Tukwilaは価格帯として最上位というだけでなく、その規模の面でも最上位となっている。トータル30MBのキャッシュメモリを搭載し、トランジスタ数は2.05B(20.5億)、ダイサイズ(半導体本体の面積)は約700平方mmに達し、TDP(Thermal Design Power:熱設計消費電力)は170Wになる。単体のCPUとしては、最大級の規模のCPUだ。パフォーマンスは従来のデュアルコアの2倍、メモリ帯域は6倍となる。

Intelは、2月3日~7日(米国時間)にかけて開催された「ISSCC(IEEE International Solid-State Circuits Conference) 2008」でTukwilaの概要を明らかにした。TukwilaはIA-64系で初のクアッドコアCPUで、65nmプロセスのデュアルコアIA-64 CPU「Montvale(モンベール)」をベースにしている。CPUコアのマイクロアーキテクチャ自体は、Montvaleから大きく変更されていないという。実際、CPUコア部分のダイ(半導体本体)レイアウトはほぼ同じに見える。しかし、Tukwilaではシステムアーキテクチャは大きく変わった。

Montvaleまでは、CPUはパラレルバスのFSB(Front Side Bus)でチップセットと接続され、DRAMインターフェイスはチップセット側にあった。また、マルチプロセッサ構成では、CPU同士をチップセットを介して接続していた。つまり、Core 2までのIA-32系CPUと同種のシステムアーキテクチャだった。

しかし、Tukwilaからは、CPUにDRAMコントローラが統合され、CPU同士はポイントツーポイント接続のシリアルバス「QuickPath InterConnect(QPI)」で相互接続される。IA-32系の次期CPU「Nehalem(ネハーレン)」と同じシステムアーキテクチャへと変わる。

|

| Tukwila (Estimated) (※別ウィンドウで開きます) PDF版はこちら |

Tukwilaのチップ間インターコネクトは6リンクのQPI。フルインターフェイス幅(Full-width)のQPIが4リンク、ハーフインターフェイス幅(Half-width)のQPIが2リンクとなっている。基本的にフル幅のQPIをCPU間の接続に、ハーフ幅のQPIをI/Oチップなどとの接続に使う構成だ。QPIはスペック的には転送レートで4.8~6.4Gtpsまでの幅があるが、Tukwilaでは4.8Gtpsのみをサポートする。それ以上の転送レートは、CPUコア数が増えた後にサポートされるようだ。1リンクのピーク帯域は19.2GB/secで、4+2リンクで合計96GB/secのピーク帯域となる。ちなみに、Nehalem系のMP(Multi-Processor)向けCPU「Nehalem-EX(Beckton:ベックトン)」は、4リンクのQPIを備える。Tukwilaの方がハーフ幅が2リンク多い構成となっている。

●CPUコア以外の部分が肥大化したTukwila

Tukwilaはメモリインターフェイスとして、FB(Fully Buffered)-DIMM(FBD)インターフェイスを実装している。FB-DIMMは、従来のFBD 1だけでなく、DDR3世代の新しいFBD 2もサポートするという。合計4つのFB-DIMMチャネルをサポートし、転送レートは4.8Gtps。メモリ帯域はピークで34GB/sec。この数字は、読み出し帯域と推定される。Tukwilaは、2つの独立したメモリコントローラを搭載しており、それぞれが2チャネル分のFB-DIMMコントローラを制御すると見られる。

4チャネルのFB-DIMMインターフェイスという構成は、Nehalem-EX(Beckton)と同じだ。ただし、IntelはNehalem-EXでは、FB-DIMM自体は使わない。FB-DIMM2(FBD2)インターフェイスをDDR3インターフェイスに変換するメモリバッファチップ「Mill Brook」を、マザーボードに搭載することで、DDR3のRegistered DIMM(RDIMM)をサポートする。つまり、Nehalem-EXはFB-DIMMのインターフェイスは実装するものの、RDIMMを使うシステムとなる。おそらく、IA-64系も同じ流れになると推定される。

Mill Brookはそれぞれ2チャネルのDDR3インターフェイスを備える。そのため、Mill Brookを使う場合は、Tukwilaは4チャネルFB-DIMM2×2チャネルDDR3で合計8チャネルのDDR3インターフェイスを備えることになる。

Intel CPU中で最大の帯域となるインターコネクトとメモリインターフェイスは、Tukwilaのダイ(半導体本体)の3エッジに配置されている。QPIは3リンクずつ上下のエッジに配置され、FB-DIMMは左エッジに配置されている。

QPIとFB-DIMMは、ともにシリアルインターフェイスであるため、TukwilaではI/O回りは完全にシリアル化されたことになる。3エッジのI/Oロジックが占めるダイ面積は123平方mmでトランジスタ数は39M(3,900万)。つまり、TukwilaではCPUコア2個分弱のダイをI/Oが占めていることになる。CPUコアよりI/Oが肥大化するCPUの傾向を示している。

CPUコア群とインターフェイスを結ぶシステムロジック部分も大きい。システムロジックはダイのちょうど中央に位置している。中核となるのは12ポートのクロスバースイッチで、これは4個のCPUコア、2個のメモリコントローラ、6個のQPIリンクを接続しているものと推定される。また、TukwilaはCPU間のキャッシュコヒーレントプロトコルをディレクトリベースとしており、そのために、オンチップで1MB弱ずつのディレクトリキャッシュを搭載し、ディレクトリステイトを保持している。これはシステムロジック部の上下に配置されている。

システムロジックも107平方mmのダイを占めており、I/Oとシステムロジックだけで230平方mmと、一般的なPC向けCPUより大きな面積となっている。また、システムロジックとI/Oブロックは2.4GHzで駆動されており、4.8Gtpsの両I/Oと同期しやすくなっている。

|

| Tukwila Statistics (※別ウィンドウで開きます) PDF版はこちら |

|

| Tukwilaのダイ (※別ウィンドウで開きます) PDF版はこちら |

●TDP 170WのホットなCPU

TukwilaのCPUコアは、Montvaleとほぼ同一で、2GHzをターゲットクロックとしている。従来のIA-64系CPUと比べて、回路設計が低電圧動作に向けて拡張され、より低い電圧での駆動が可能になったという。下がISSCCで示された動作周波数と電圧のチャートだ。グリーンが動作パスした周波数と電圧の組み合わせ、レッドが動作失敗した組み合わせだ。CPU温度(Tj)が摂氏80度のケースだという。ISSCCでは0.9~1.2Vの動作電圧になると説明された。

|

| Tukwilaの動作周波数 (※別ウィンドウで開きます) PDF版はこちら |

Tukwilaも、動的に動作周波数と電圧を切り替えられる。ただし、4つのCPUコアが連動して切り替わる。QRコントロールユニットが、CPU群の320のアーキテクチャルイベントをモニタし、6μs毎に電圧と周波数のペアを決定する。切り替えレイテンシを短縮するために、Tukwilaでは2系列のPLLを搭載し、片方のPLLがコアクロックをドライブしている間に、もう1つのPLLが要求のあったクロック比に設定される。PLLを切り替えることでスイッチする。

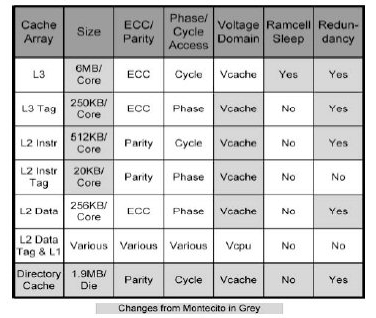

Tukwilaのキャッシュは、それぞれのCPUコア毎に占有で3階層。L3キャッシュは各CPUコアに6MBずつで、合計24MB。L3キャッシュのタグRAMだけで各コアに250KBずつが搭載されている。L2はL2命令キャッシュが各コアに512KBずつ、L2データキャッシュが256KBずつ。キャッシュ量はともかく、キャッシュ階層の基本は従来のIA-64系CPUと変わらない。このほか、ディレクトリキャッシュがダイに1.9MBあるため、合計のキャッシュは30MBに達する。

L2とL3キャッシュ用の電圧は、CPUコアとは別個に供給し、CPUコア電圧が変動してもキャッシュ電圧(Vcache)は1.1Vを保つ。キャッシュ電圧を分離しているため、CPUコアの電圧を下げた場合も安定した動作を保つことができる。従来はL3だけがキャッシュ用電圧(Vcache)だったが、TukwilaではL2にまで広げられた。

また、TukwilaではL3キャッシュにスリープトランジスタを導入した。これによってアイドル時に、キャッシュSRAMからのリーク電流(Leakage)を抑えることが可能になった。

|

| Tukwilaのキャッシュ |

このほか、回路設計ではTukwilaはソフトエラー対策が強化された。これは、ソフトエラー対策を重視するエンタープライズ市場のためだ。

TukwilaのTDPは、クアッドコア版で130Wと170Wの2レベル。ISSCCではCPU温度(Tj)の上限が摂氏110度となっていたが、製品版のTcase(CPUケース温度)の上限は摂氏85度だと伝えられる。消費電力面でも、規模の大きなCPUだ。

パッケージは「LGA1248」。パッケージサイズは66×66mm(縦×横)で、ヒートスプレッダが覆うCPUダイの4周囲を、電力供給のLGAランドが取り囲む構成となっている。IA-64系CPUでは、電力はマザーボード経由ではなく、CPUのサブストレートに直接電力を供給する。この仕組みはTukwilaでも継続される。

●紆余曲折のあったTukwilaのプロジェクト

Tukwilaは紆余曲折のあったCPUだ。「Tanglewood(タングルウッド)」というコードネームで呼ばれていたこのCPUの開発について、Intelは当初、旧DECのAlphaプロセッサチームが開発に加わっていると公式に説明していた。しかし、ISSCCでのTukwilaの発表で登場したのは、従来のIntel-HPのIA-64開発チーム。マイクロアーキテクチャも、従来のIA-64の延長にある。Tukwilaの開発は、いったんは新チームに渡ったものの、もう一度、従来のIA-64開発チームに戻されたと言われている。

旧Alphaチームの時点では、CPUコア自体をより小さくシンプルにして、CPUコア数を増やすことが検討されたと言われている。実際、Intelは以前、“片手以上の数のCPUコア”をTukwilaに搭載すると説明していた。それにはマイクロアーキテクチャ上の大きな変更が必要となるはずで、Tukwilaは根本から再設計されたIA-64になる予定だったと推定される。

IA-64系のCPUコアを小さくするための手段として考えられるアプローチの1つは、VLIW型のIA-64命令を分解してしまう方法だ。IA-64では、3命令を1つにまとめた命令グループ「バンドル」を構成している。現在のIA-64 CPUは、2バンドル、最大6命令を並列に実行する。そのため、6命令の組み合わせにマッチするだけのCPUリソースを備えなければならず、それがCPUコアの大型化を招く原因の1つとなっている。

そのため、このバンドルをCPUのデコーダで分解すれば、CPUコアの簡素化のチャンスが生まれることになる。バンドルを分解すれば、個々の命令は単純な固定フォーマット固定長の命令となる。そのため、スーパースカラ型の比較的シンプルなCPUコアで実行することが可能になる。しかも、バンドルにグループ化する際に、並列実行できるようにコンパイラで並べ替えられているため、スケジューリングも最低で済む。

しかし、このアプローチを取った場合には、従来のIA-64ソフトウェアで積み上げてきた、コード最適化の多くがムダになってしまう。つまり、従来の「命令レベルの並列性(ILP:Instruction-Level Parallelism)」を維持するか、CPUコアを増やすことによる「スレッドレベルの並列性(TLP:Thread-Level Parallelism)」を取るかの選択となる。そもそもIA-64命令セットアーキテクチャ(ISA)はILPを追求するために作られた。それをILPを犠牲にしてTLPに振ってしまうと、IA-64 ISAである存在意義が揺らいでしまう。そのため、Intelとしては、そのアプローチは採ることができなかったと推定される。

Tukwilaでは、2個のデュアルダイCPUを、MCM(Multi-Chip Module)で封止してクアッドコアにする案も検討されたと言われている。しかし、これも採られず、最終的に700平方mmの巨大チップに行き着いた。

|

| Tukwilaの過去のプランの推定図 (※別ウィンドウで開きます) PDF版はこちら |

□ISSCCのホームページ(英文)

http://www.isscc.org/isscc/

□関連記事

【2月4日】【海外】IntelがいよいよSilverthorneとTukwilaの概要を発表へ

http://pc.watch.impress.co.jp/docs/2008/0204/kaigai415.htm

【2007年10月2日】【海外】デュアルコアからオクタコアまでスケーラブルなNehalem

http://pc.watch.impress.co.jp/docs/2007/1002/kaigai390.htm

【2007年3月30日】【海外】Intelのマイクロアーキテクチャ改革「Nehalem」

http://pc.watch.impress.co.jp/docs/2007/0330/kaigai348.htm

(2008年2月8日)

[Reported by 後藤 弘茂(Hiroshige Goto)]

【PC Watchホームページ】

PC Watch編集部 pc-watch-info@impress.co.jp ご質問に対して、個別にご回答はいたしません

Copyright (c) 2008 Impress Watch Corporation, an Impress Group company. All rights reserved.