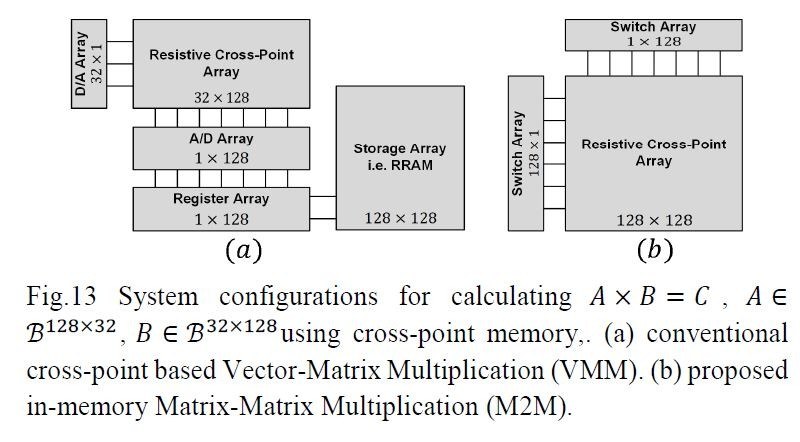

行列同士の演算を実行する回路のブロック図。左(a)は、従来の回路方式(VMM:Vector-Matrix Multiplication)。ReRAMのクロスポイントアレイのほかに、A-D変換回路と結果格納用メモリを必要とする。右(b)は開発した回路方式(M2M:in-memory Matrix-Matrix Multiplication)。クロスポイントアレイの規模は増大するものの、A-D変換回路と結果格納用メモリを省ける。清華大学とスタンフォード大学の共同研究チームが2018年のVLSIシンポジウムで発表した論文(論文番号T3-4)から