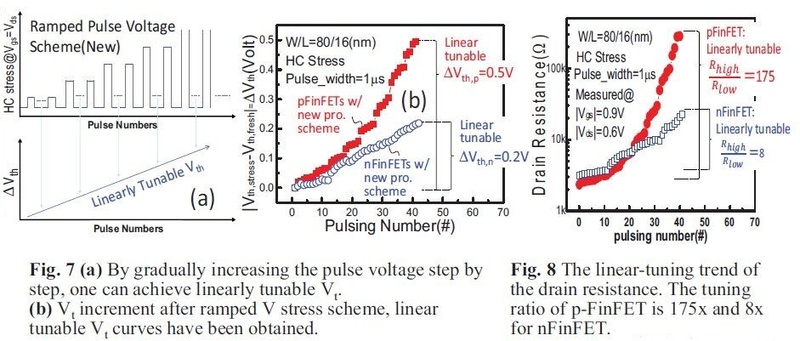

左のグラフはFinFETに加える電圧パルス列と、しきい電圧の変化(イメージ)。電圧をじょじょに高くしていくことで、しきい電圧をリニアに上げていく。中央のグラフは電圧パルス数としきい電圧の変化量の関係(測定値)。約45回の電圧パルス印加によってnチャンネルFinFETのしきい電圧は約0.2V上昇し、pチャンネルFinFETのしきい電圧は約0.5V上昇した。右のグラフは電圧パルス数とドレイン抵抗の関係(測定値)。約45回の電圧パルス印加によってnチャンネルFinFETのドレイン抵抗は8倍に、pチャンネルFinFETのドレイン抵抗は175倍に増大した。国立交通大学とUMCの共同研究グループが2018年のVLSIシンポジウムで発表した論文(論文番号T3-3)から